Single layer polysilicon grid OTP device and method for forming the same

A technology of single-layer polysilicon and polysilicon, which is applied in the manufacture of electrical solid-state devices, semiconductor devices, semiconductor/solid-state devices, etc., can solve the problems of large space, inability to effectively reduce the device area, and the large area of a single OTP device, and achieve a small area , large unit capacitance and high coupling efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

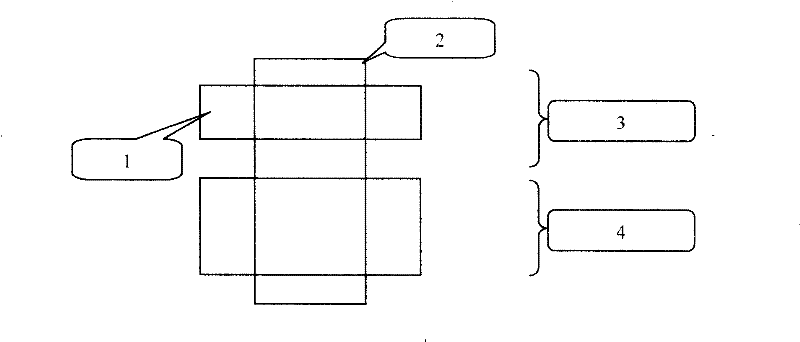

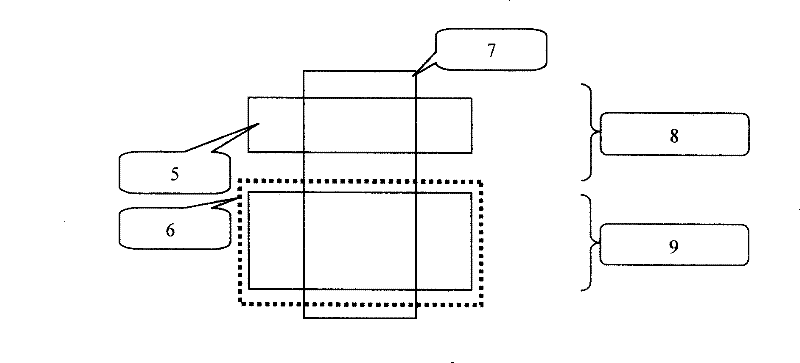

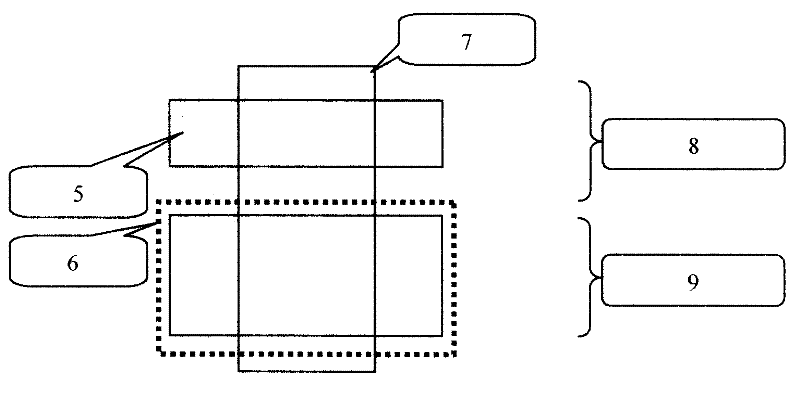

[0014] Such as figure 2 It is the device design and structure of a specific embodiment of the present invention, wherein: 5. Active region, 6. Offset injection region, 7. Polysilicon gate, 8. Memory transistor, 9. Transistor capacitor region. The structure features a high-voltage offset implant in an existing high-voltage process figure 2 The device structure of the buried layer (or similar to the buried layer) is formed on the capacitor side of the transistor shown. With the buried layer, the capacitance value per unit area of the transistor capacitor is improved, and the overall coupling efficiency of the OTP device is increased; at the same time, due to the buried layer The depth of the junction is usually deeper (should be deeper than the common source-drain junction), so this also improves the breakdown voltage of the transistor-capacitance active region junction; therefore, this embodiment effectively realizes embedding with reduced area, good programming effect, and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More