Method and device for expanding internal integrate circuit bus

An internal integrated circuit and bus technology, applied in the direction of electrical digital data processing, instruments, etc., can solve the problems of receiver data sampling error, communication error, slow transition edge, etc., and achieve the effect of reducing the expansion cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

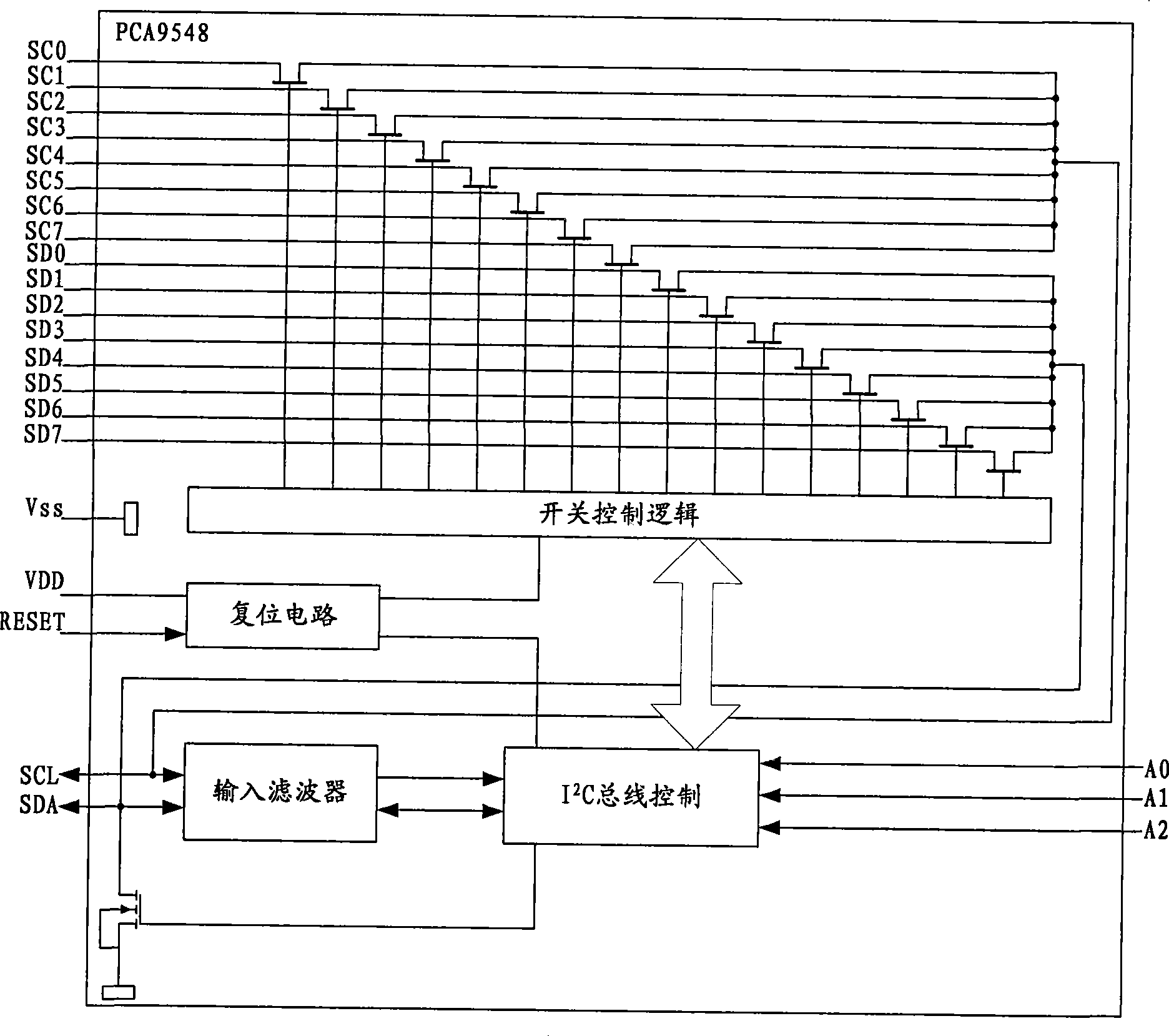

[0032] Figure 6 The flow chart of the embodiment of the method for extending the internal integrated circuit bus of the present invention includes:

[0033] Step 61, pass the I 2 The serial clock line (SCL) of the C-bus is expanded into multiple serial clock lines; a strobe multiplexer can 2 The serial clock line of the C bus is extended to multiple I 2 The serial clock line of the C bus; when there are multiple I 2 C bus can be used with I 2 The same number of strobe multiplexers for the C bus, one-to-one correspondence, to expand each I 2 SCL of the C bus. The gating multiplexer can control the gating of the SCL before and after the expansion by the programmable input / output (PIO) interface signal of the controller, see the description in the second embodiment of the device for details.

[0034] Step 62, connecting the plurality of serial clock lines to each slave device; wherein, each slave device is to be connected to I 2 C-bus devices.

[0035] Step 63, the I 2 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More