MOSFET having a high stress in the channel region and fabricating method thereof

A region and drain region technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as small process windows, achieve good etching profile, reduce barrier reduction, and improve etching uniformity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

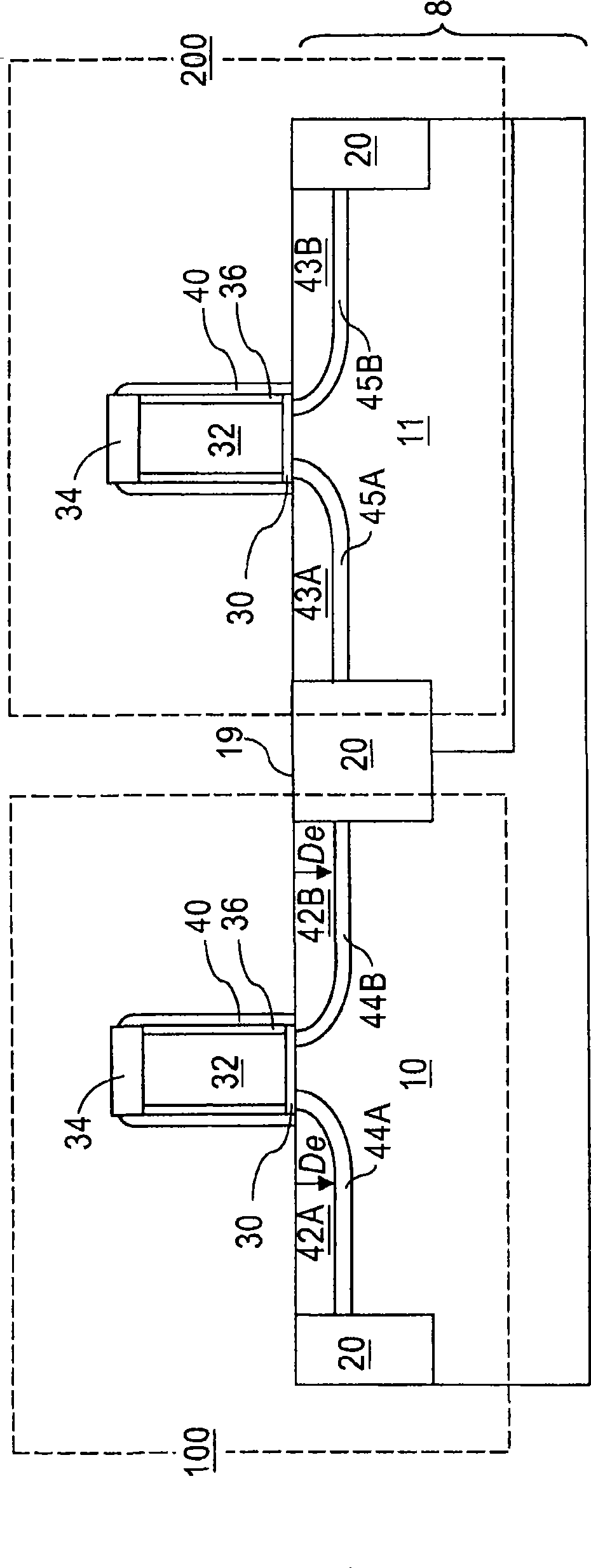

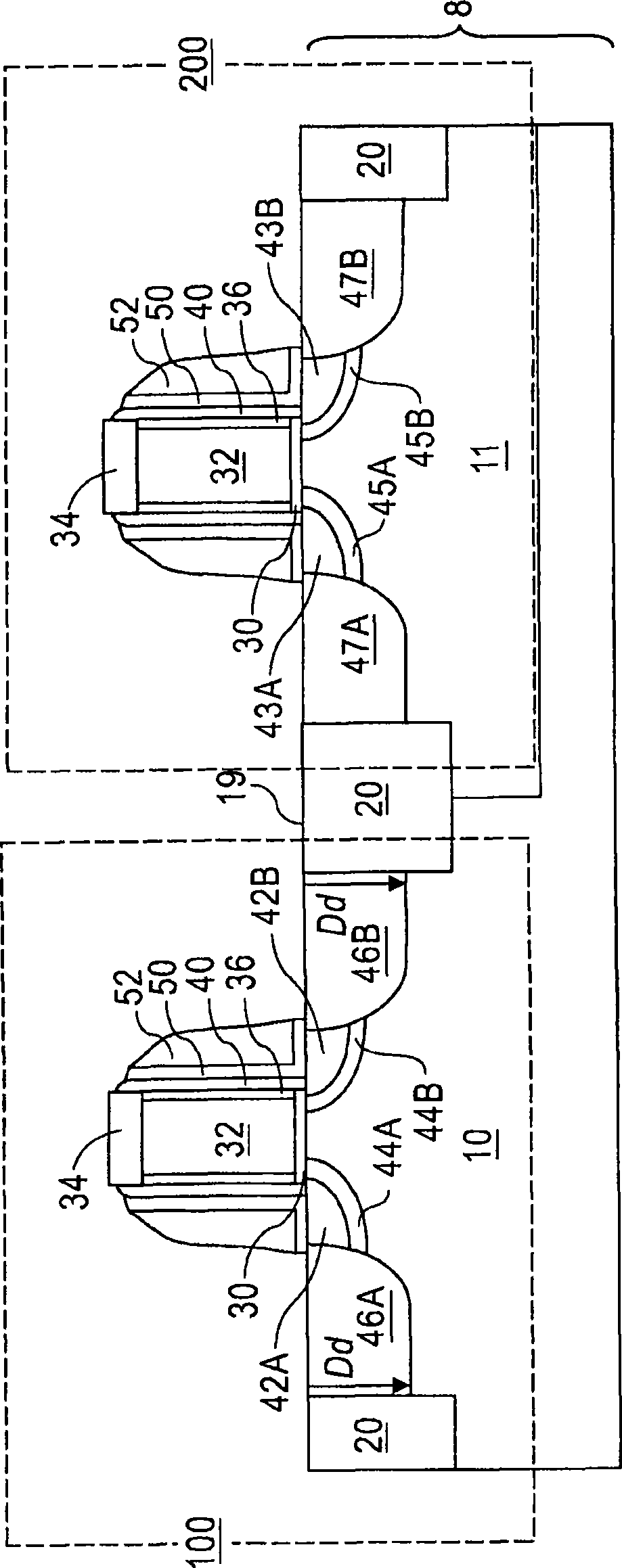

[0075] (0038) As noted above, the present invention relates to stressed CMOS devices having stress-inducing materials embedded in source and drain extension regions and methods of fabrication thereof, thereby enabling heterojunctions and p-n junctions between two semiconductor materials Coincidentally, it will be described in detail with reference to the accompanying drawings. It should be noted that identical and corresponding elements are marked with the same reference numerals.

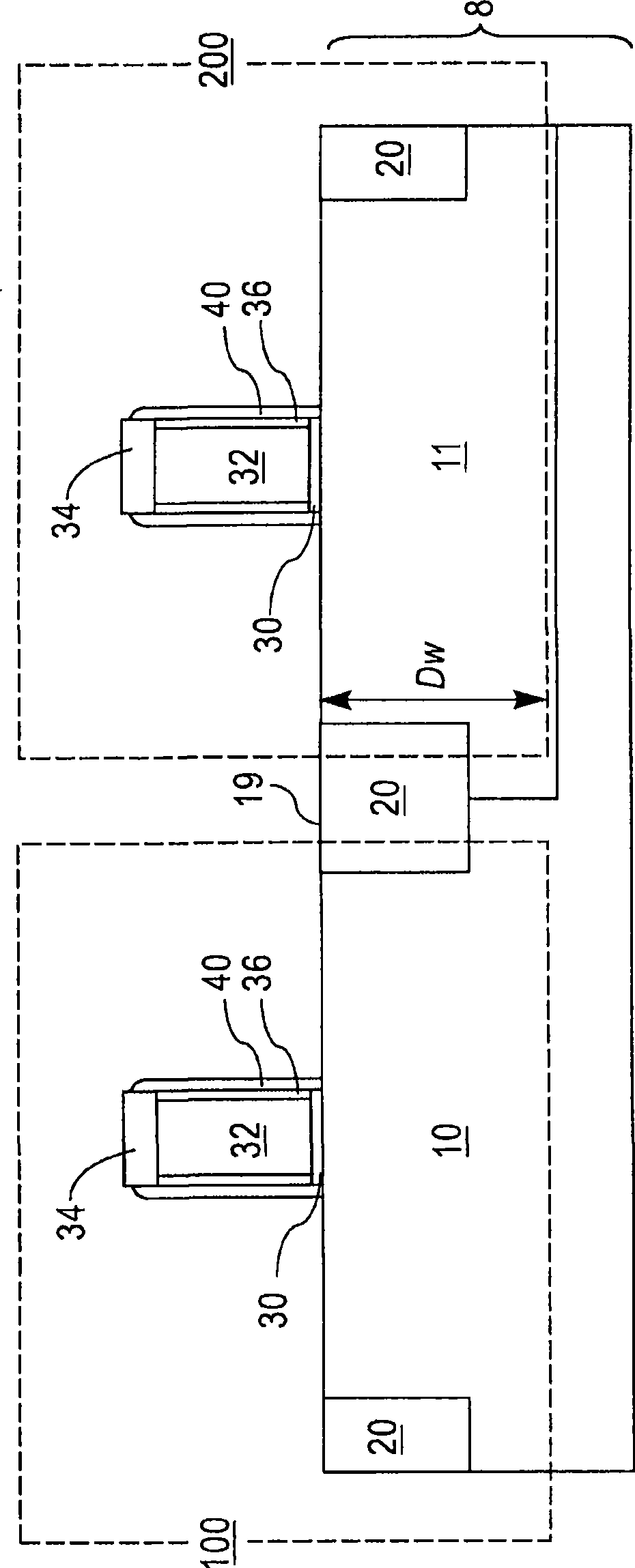

[0076] (0039) Reference figure 1 , shows a first exemplary semiconductor structure according to the first embodiment of the present invention, which includes a semiconductor substrate 8 including a first semiconductor region 10 and a shallow trench isolation 20 . The first semiconductor region 10 comprises a first semiconductor material having a doping of the first conductivity type with a first dopant concentration. The semiconductor substrate 8 may further comprise a second semiconductor regio...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More