Optimization method and apparatus for verification vectors

An optimization method and a technology for optimizing devices, which are applied in the directions of measuring devices, measuring electricity, and measuring electrical variables, etc., can solve problems such as unsatisfactory simulation speed of simulation verification technology, inability to know the contribution of test programs, and redundancy of verification vectors, etc., to achieve Effects of shortening simulation time, accelerating verification convergence, and improving verification efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] In order to make the purpose, technical solution and advantages of the present invention clearer, a verification vector optimization method and device of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

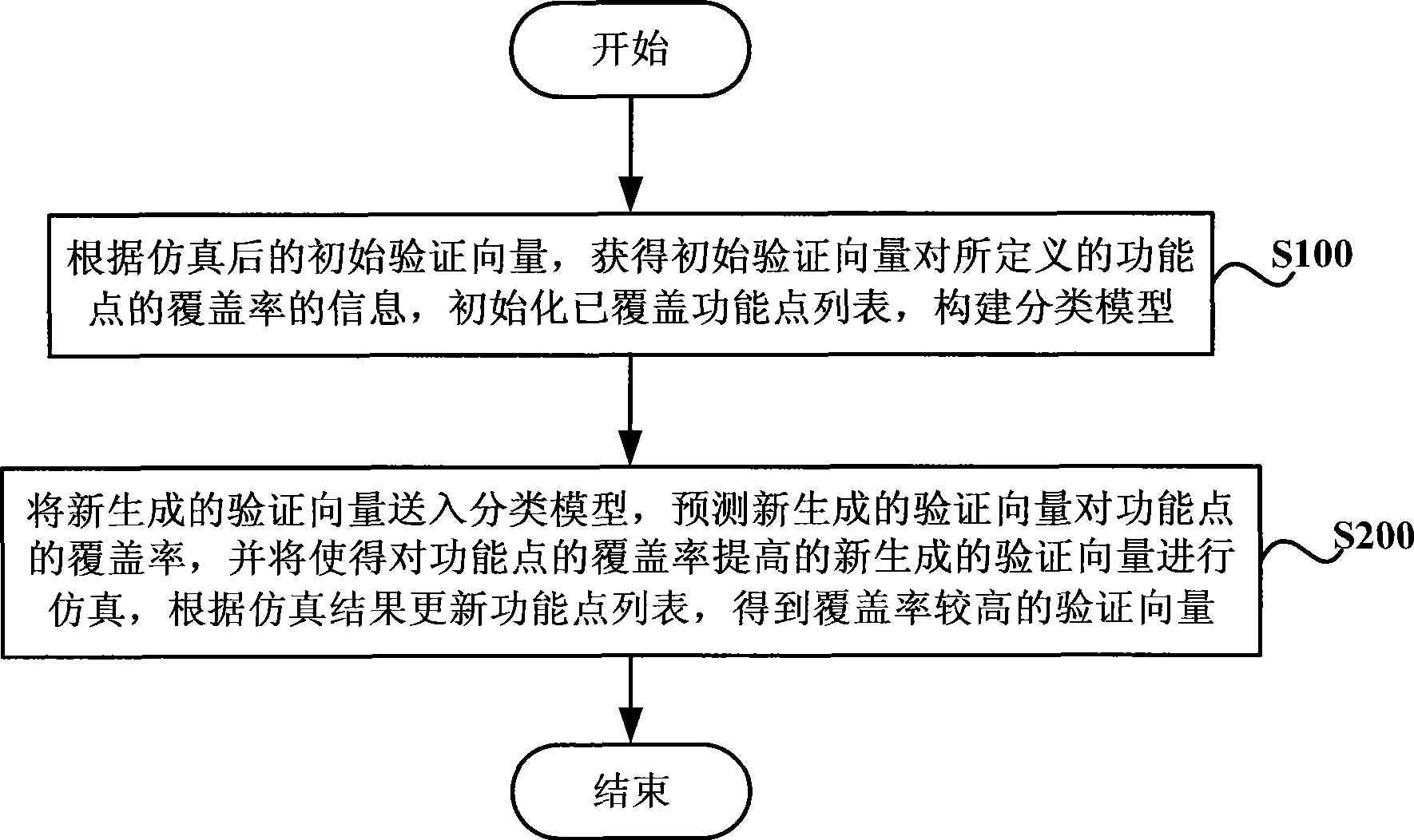

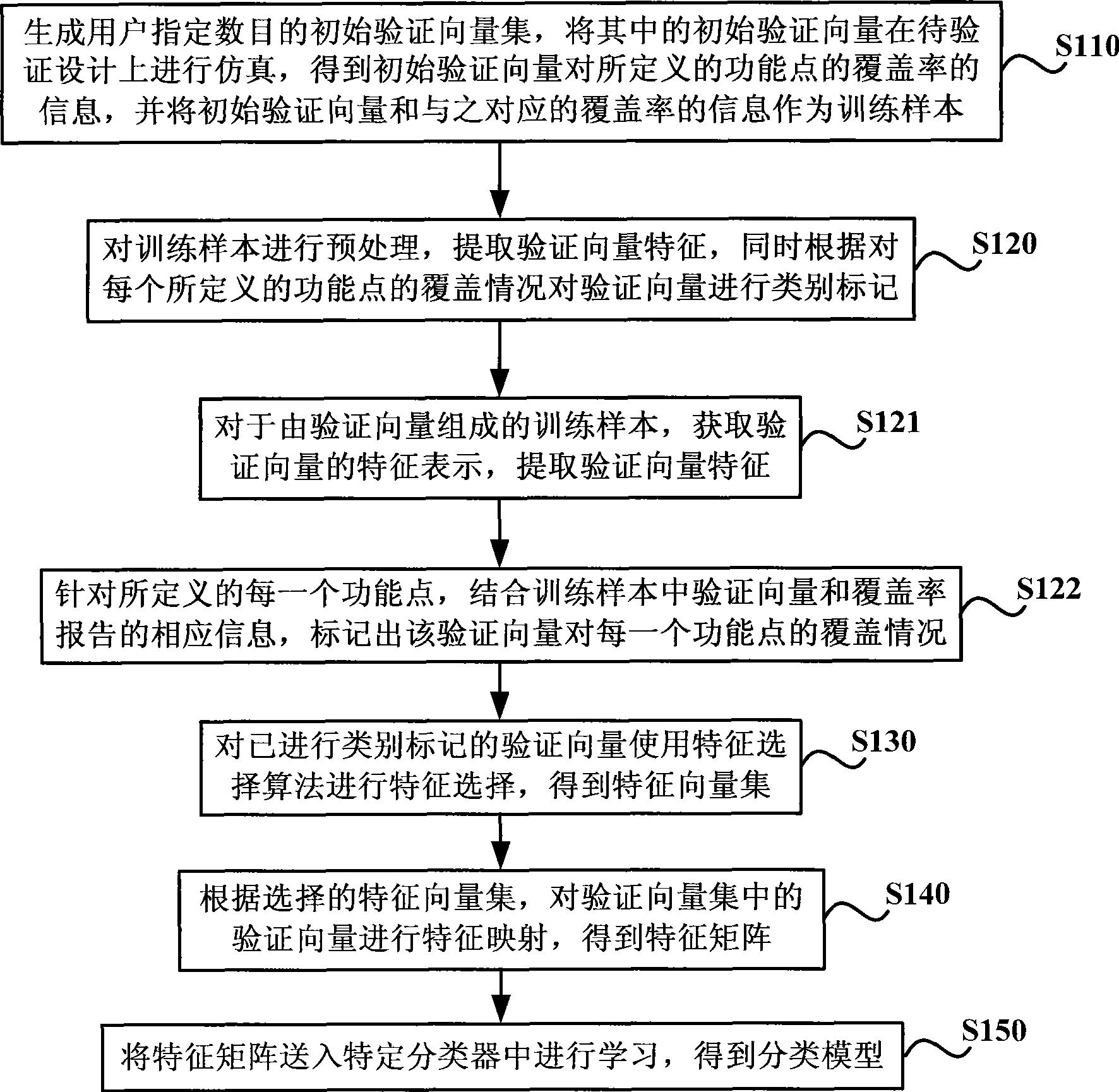

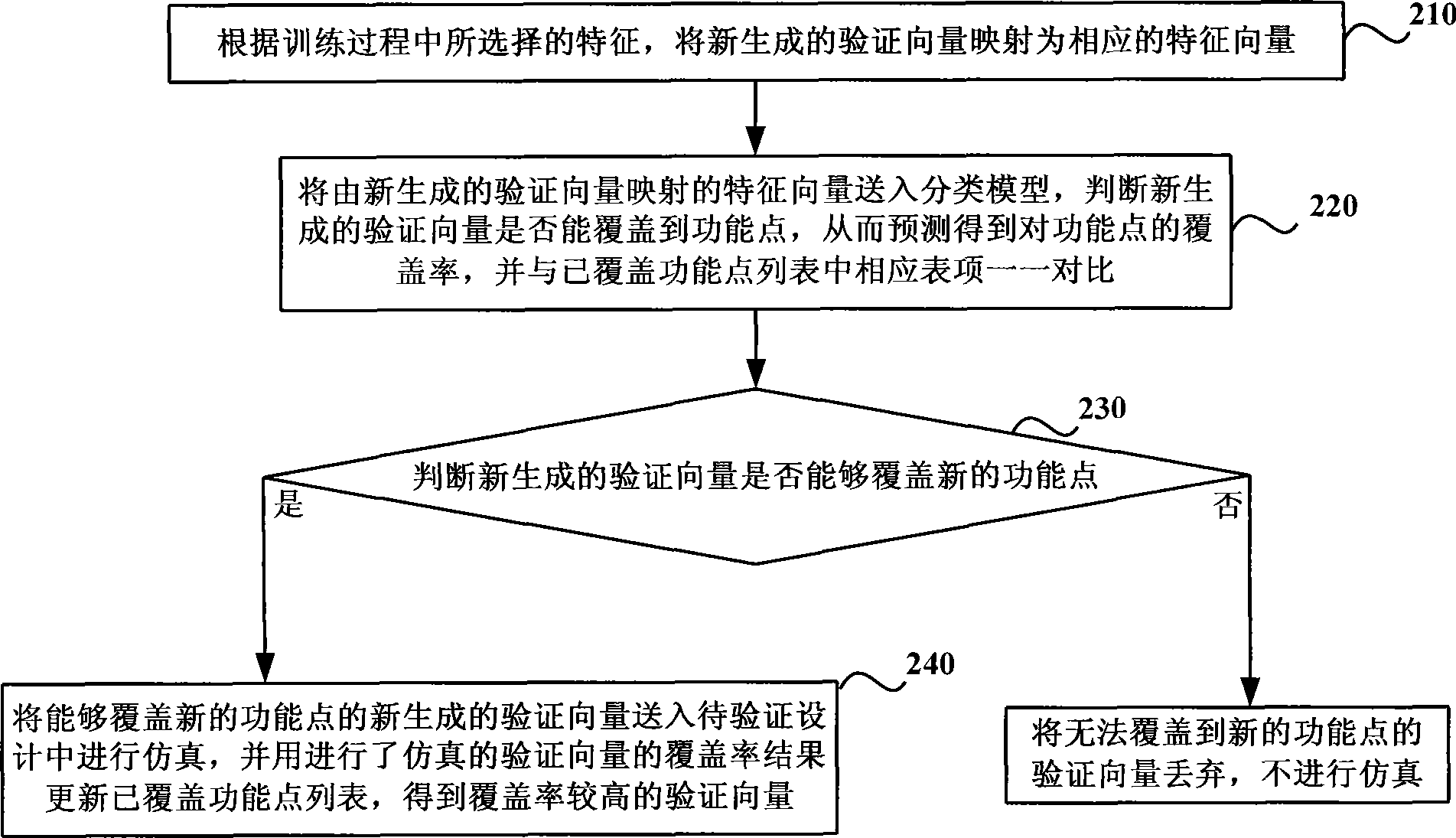

[0047]A verification vector optimization method and device of the present invention is to predict the coverage rate information of the newly generated verification vector according to the simulation information of the verified vector, and judge in advance whether it is possible to improve the current coverage rate. If it can be sent Enter the design to be verified to perform simulation operations, otherwise it is considered as a redundant verification vector and regenerated. It can reduce the use of verification vectors as much as possible an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More