Memory circuit

A technology for storing circuits and voltages, applied in the field of memory arrays

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

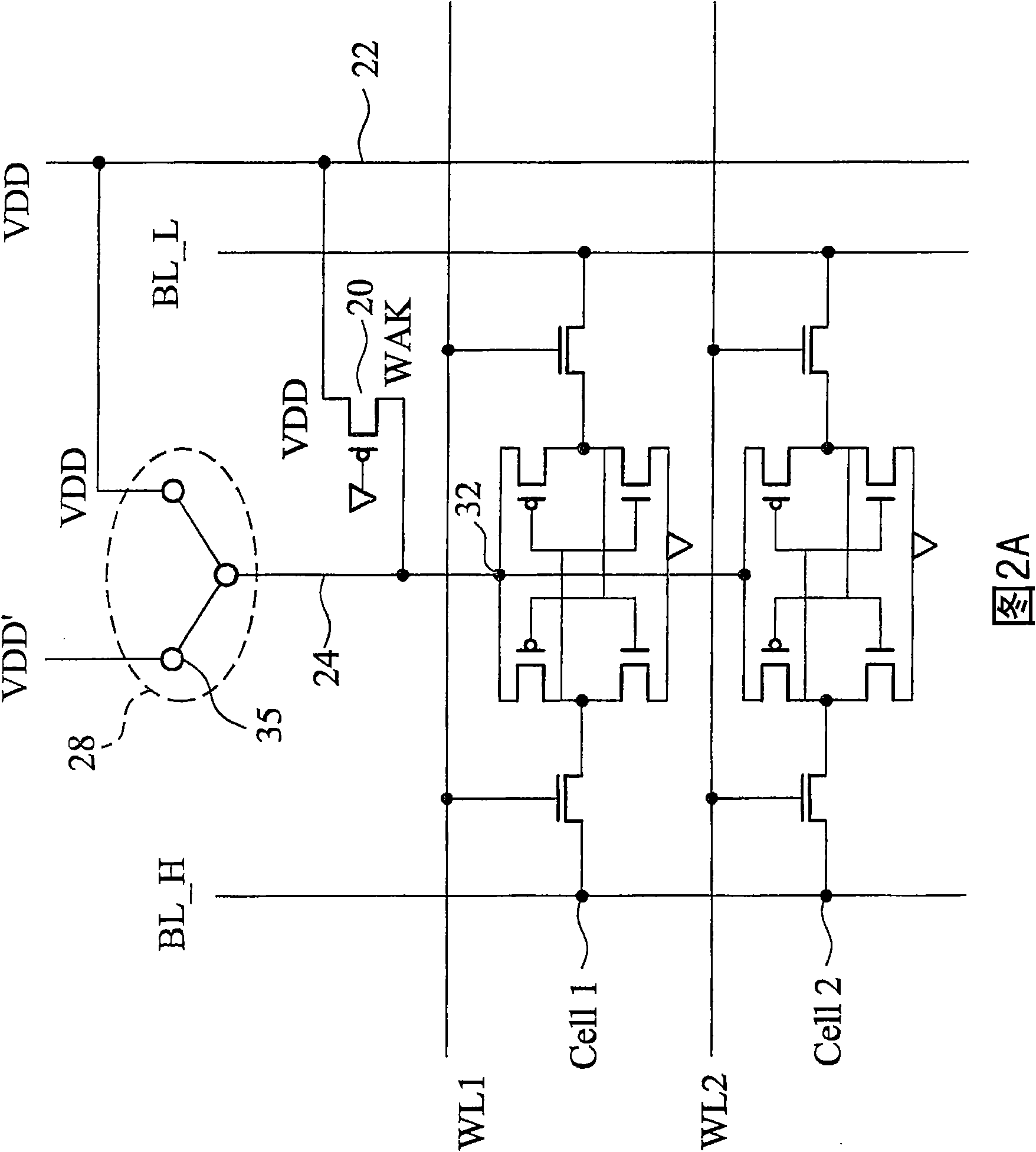

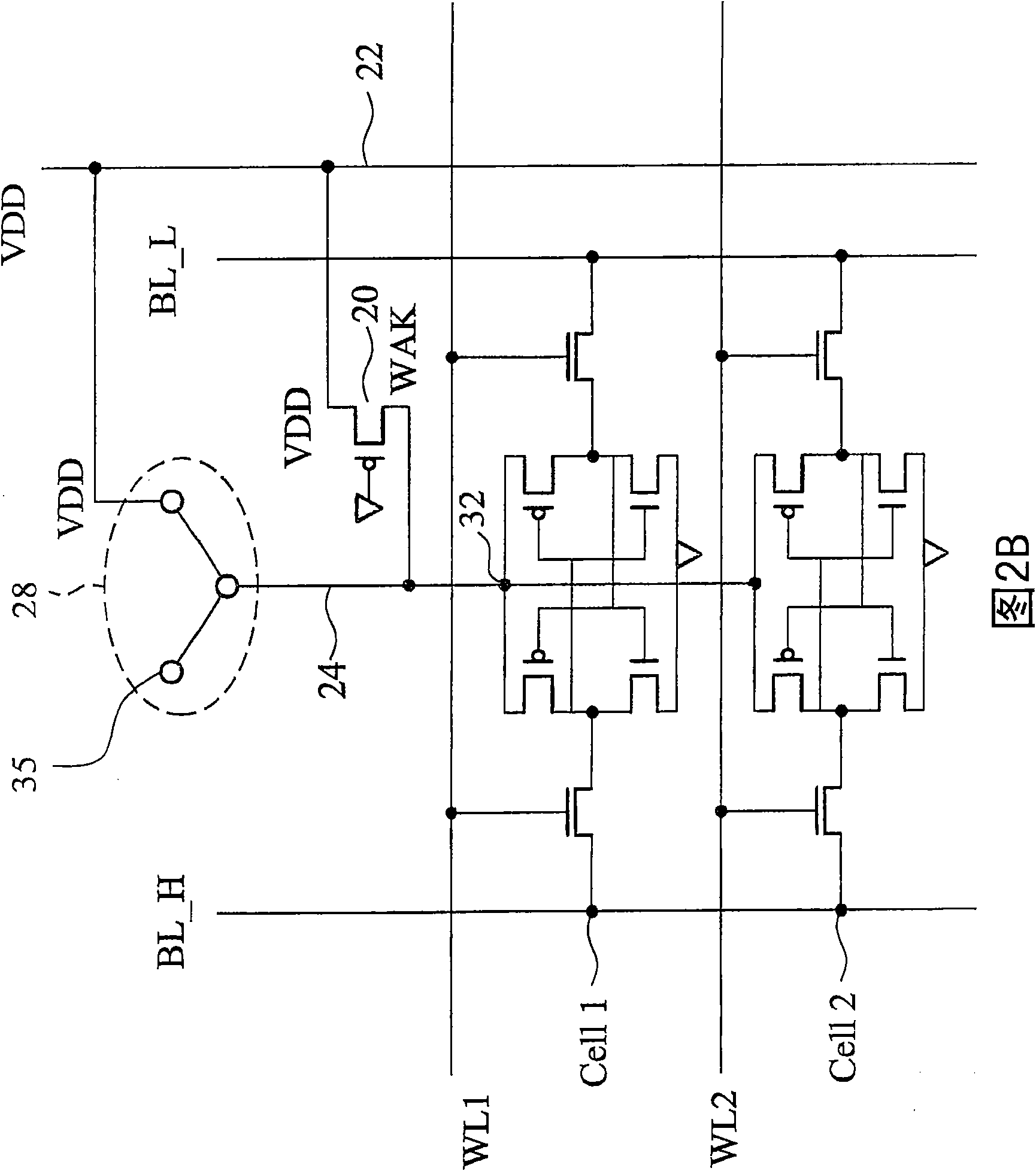

[0019] Figure 2A An example of the present invention is shown. The SRAM cells Cell1 and Cell2 form a pair and share a write-assist-keeper (WAK) device 20 . The SRAM cells Cell1 and Cell2 are respectively connected to word lines WL and WL', and share a pair of bit lines BL_H and BL_L. In the following figures, although each SRAM cell only includes 6 transistors (6T), however, the concept of the present invention can be easily applied to SRAM cells with different numbers of transistors (eg, 8T, 12T, etc.).

[0020] In a preferred embodiment, the WAK device 20 is a P-type metal oxide semiconductor (PMOS) transistor. In other embodiments, the WAK device can also be an N-type metal oxide semiconductor (NMOS) transistor, or other devices with a regulating current. In the best case, the WAK device is a conductor when the supply voltage is applied. Thus, in Figure 2A and Figure 2B In certain embodiments, the gate of the WAK device 20 is connected to VSS (or ground), or to ano...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More