Two-port SRAM having improved write operation

一种电源端、输出端的技术,应用在存储器领域,能够解决降低读取和写入性能等问题,达到写入操作更的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

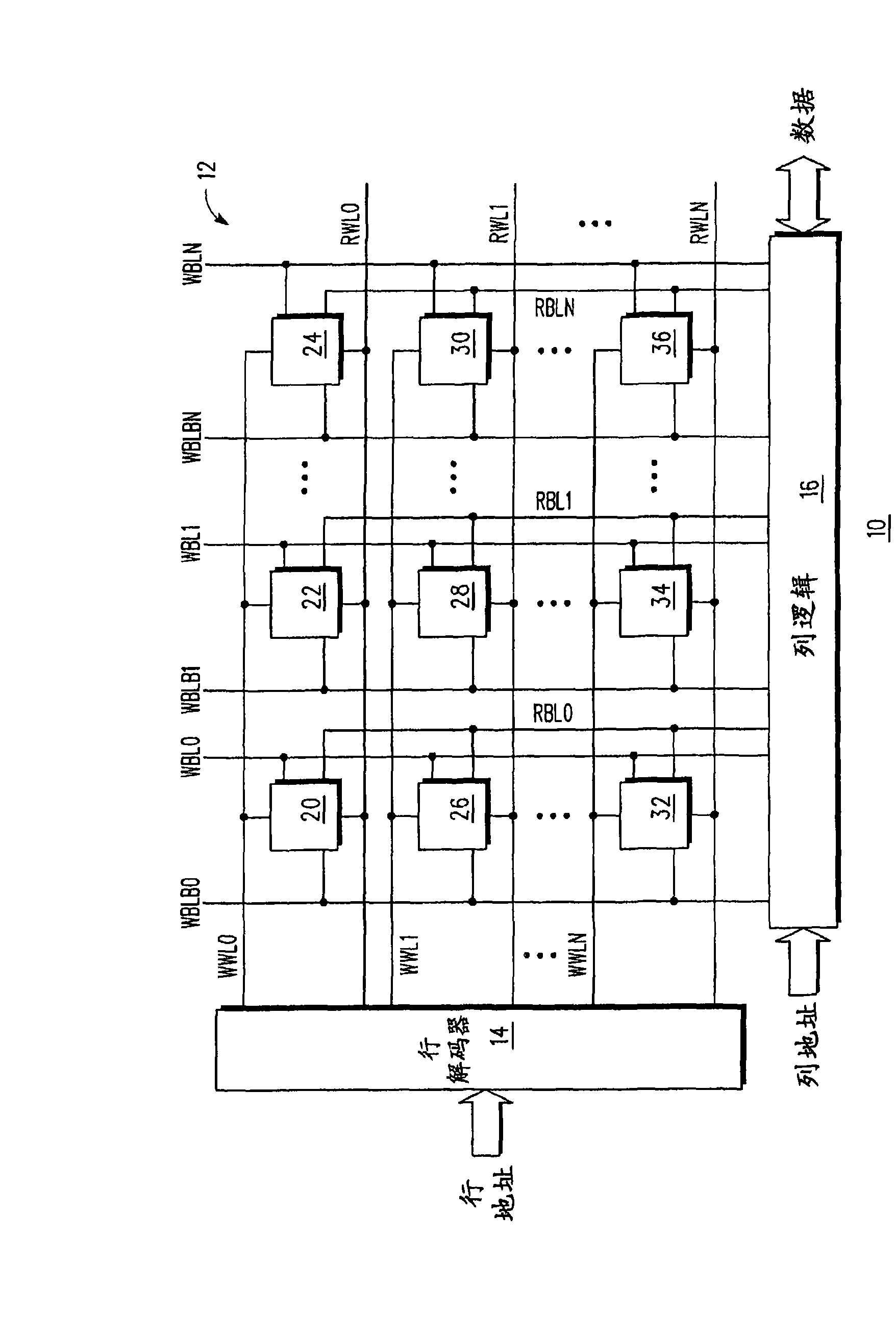

[0018] figure 1 A two-port integrated circuit memory 10 according to an embodiment of the present invention is shown in block diagram form. Generally, memory 10 includes a plurality of memory cells 12 , row decoders 14 , and column logic 16 . The plurality of memory cells 12 includes representative memory cells 20 , 22 , 24 , 26 , 28 , 30 , 32 , 34 , and 36 . Such as figure 1 As shown, each memory cell is coupled to one of a plurality of write word lines labeled "WWL0" through "WWLN", one of a plurality of pairs of write bit lines labeled "WBL0 / WBLB0" through "WBLN / WBLBN" A pair, one of a plurality of read word lines labeled "RWL0" through "RWLN," and one of a plurality of read bit lines labeled "RBL0" through "RBLN." The plurality of memory cells 12 are implemented in rows and columns. For example, memory cells 20, 22, and 24 and word line WWL0 form a row of memory cells. Likewise, memory cells 20, 26, and 32 form a column of memory cells.

[0019] Row decoder 14 has an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com