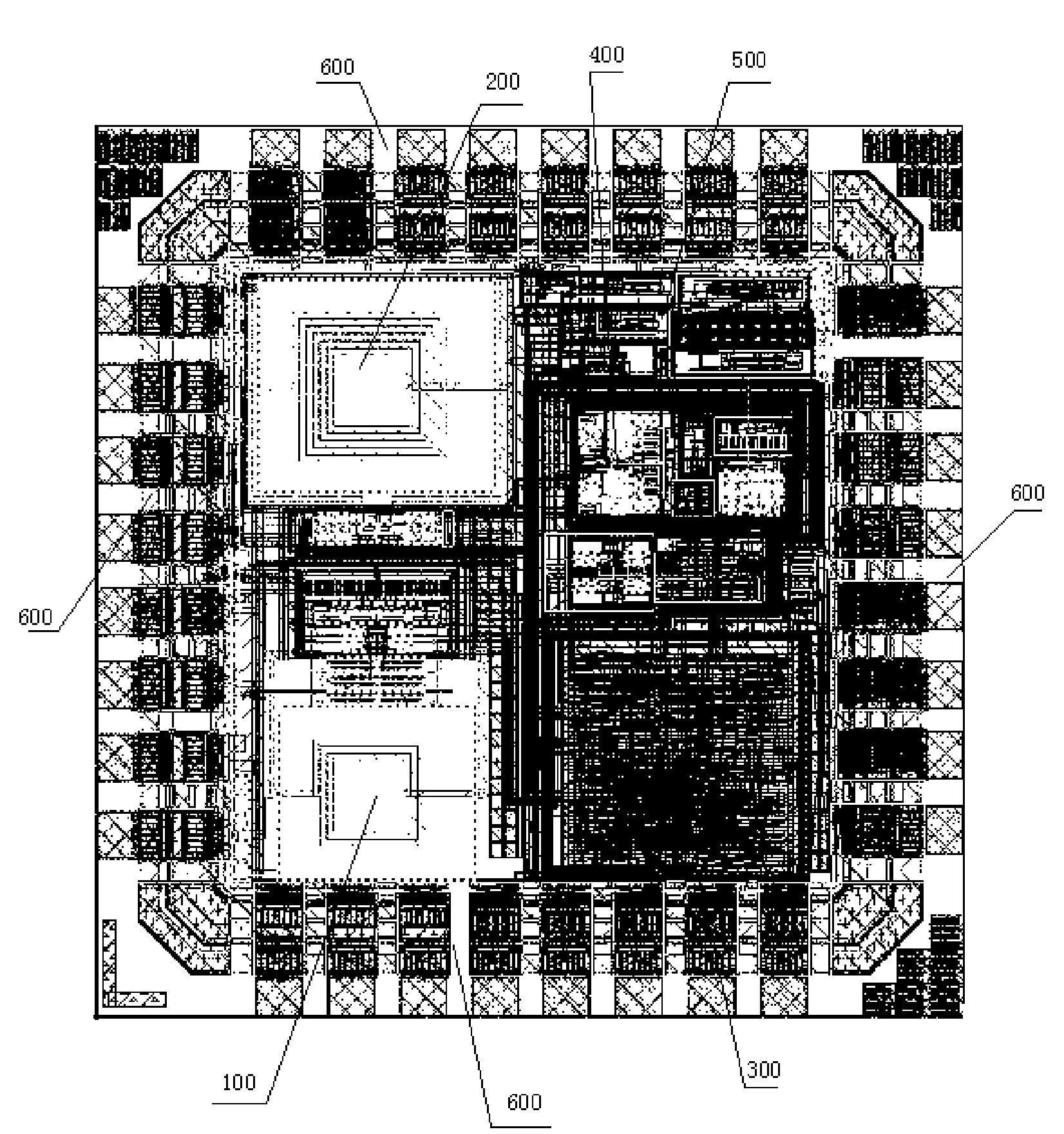

Domain structure of frequency synthesizer chip

A technology of frequency synthesizer and layout structure, applied in instruments, semiconductor devices, electric solid-state devices, etc., can solve the problems of frequency synthesizer chip design failure, unreasonable layout design, etc., to achieve optimized design, reasonable location layout, and reduced size the effect of interference

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0012] In order to make the object, technical solution and advantages of the present invention clearer, the implementation manner of the present invention will be further described in detail below in conjunction with the accompanying drawings.

[0013] see figure 1 , this embodiment takes the S-band Fractional-N frequency synthesizer as an example to illustrate the frequency synthesizer chip layout structure provided by the embodiment of the present invention. The frequency synthesizer chip layout consists of a first layout area 100, a second layout area 200, The third layout area 300, the fourth layout area 400, the fifth layout area 500 and the sixth layout area 600; the first layout area 100, the second layout area 200, the third layout area 300, the fourth layout area 400 and the sixth layout area The fifth layout area 500 is located in the center of the frequency synthesizer chip layout; the first layout area 100 is connected to the second layout area 200, the second layo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com