MOS transistor noise model formation method, device and circuit simulation method

A MOS transistor and noise model technology, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve the problems that affect the accuracy of circuit design, do not consider the effect of temperature change of MOS transistors, and affect circuit performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

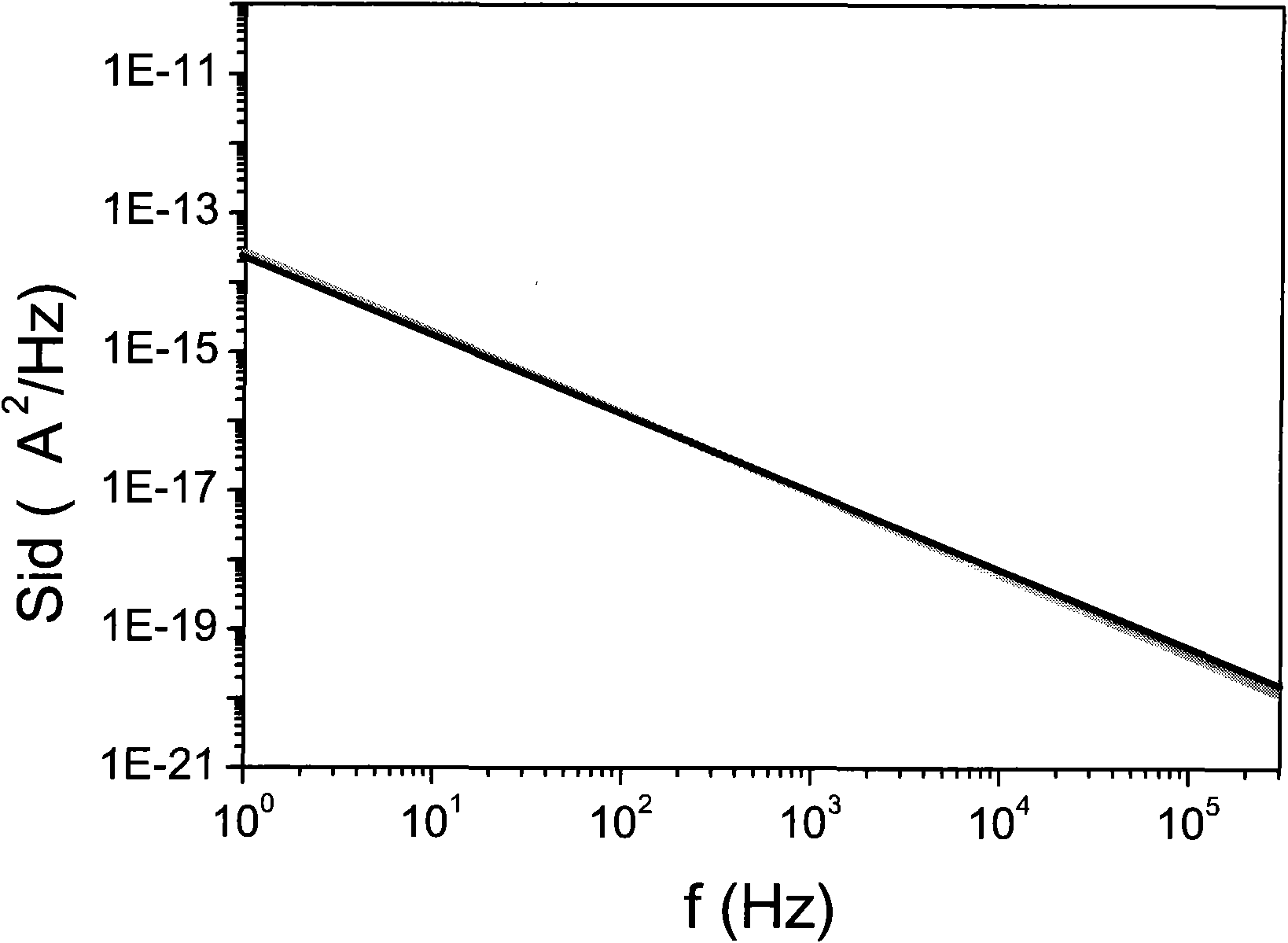

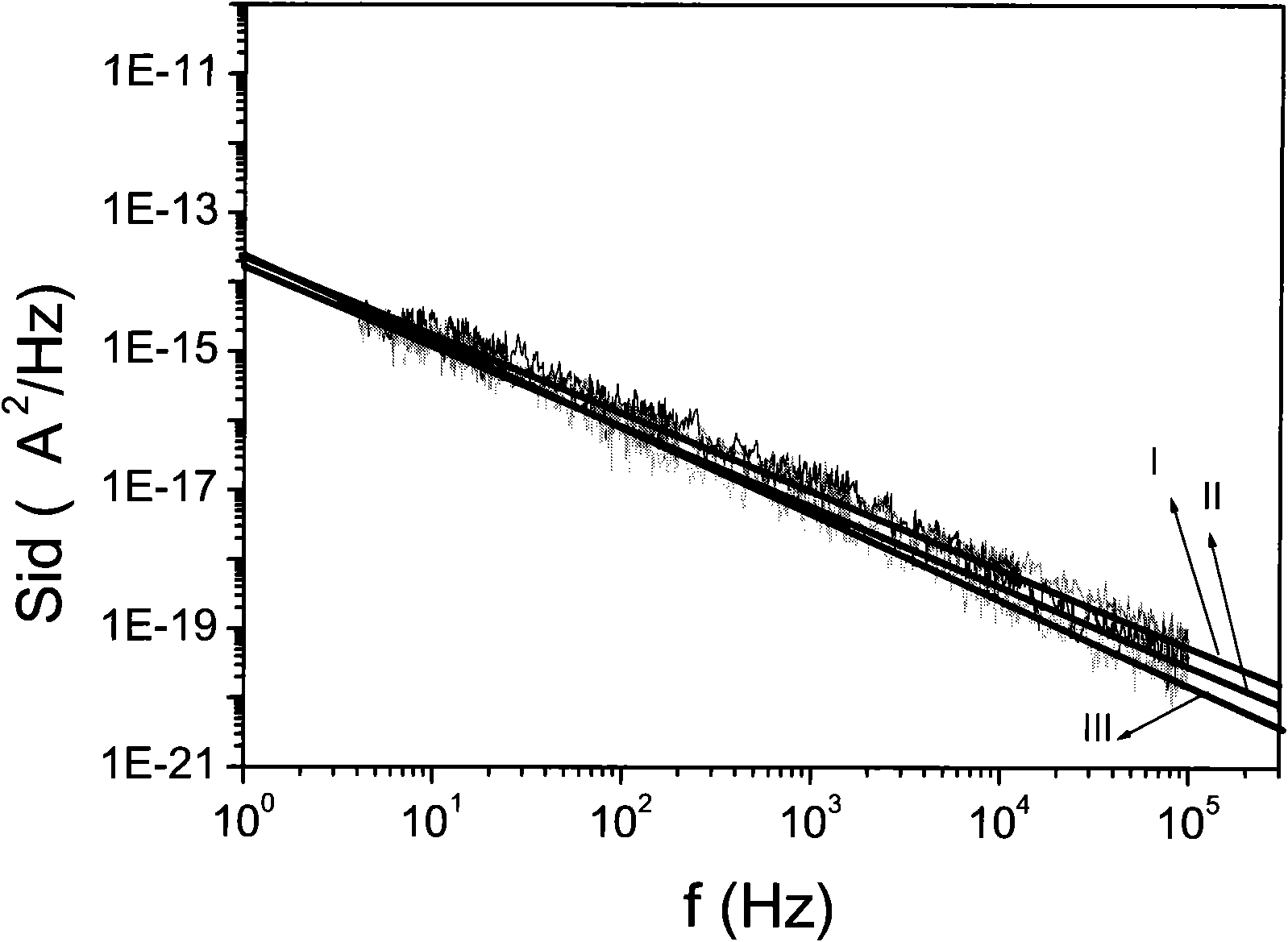

[0033] The present invention obtains normal temperature coefficient K by obtaining f0 and A f0 and the values of parameters A and B, adding the influence of temperature to the noise model of the MOS transistor makes the noise model of the MOS transistor more accurate. The relationship between current noise figure (Sid) and frequency (f) in operation is more consistent.

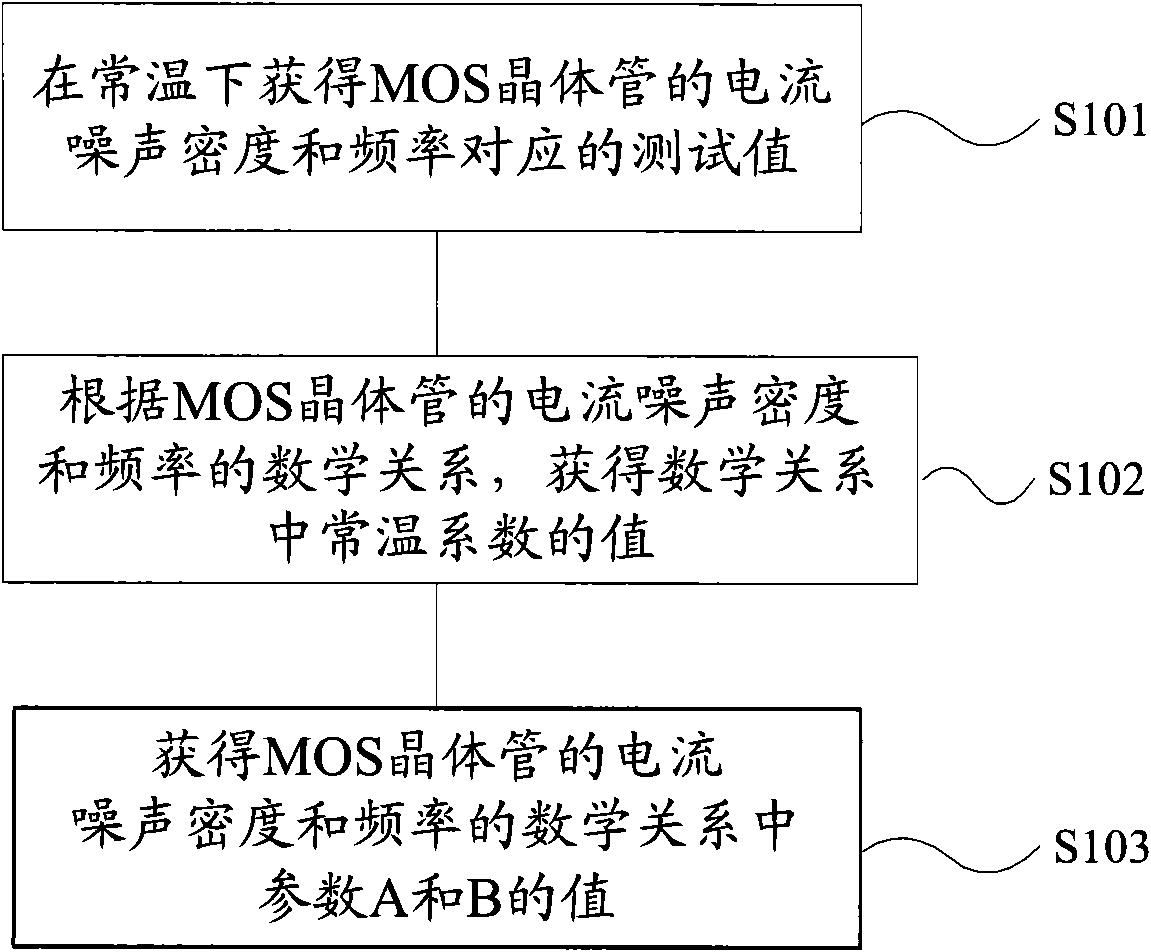

[0034] First, the present invention provides a schematic flow chart of a specific embodiment of a method for forming a noise model of a MOS transistor, referring to image 3 , including the following steps:

[0035] Step S101 is executed to obtain test values corresponding to the current noise density Sid and the frequency f of the MOS transistor at room temperature.

[0036] Execute step S102, according to the mathematical relationship between the current noise density Sid of the MOS transistor and the frequency f Sid = { ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More