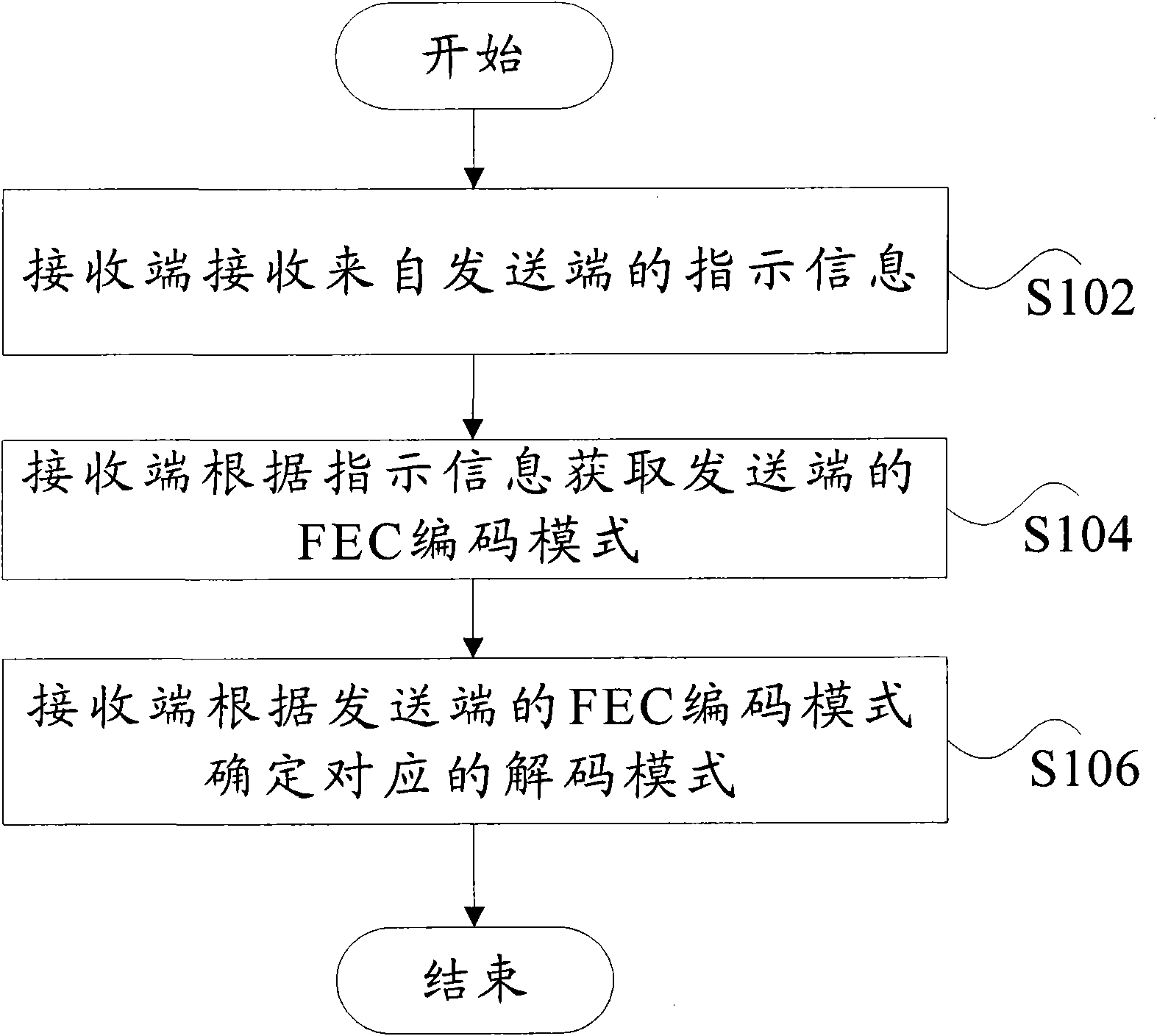

Method and device for synchronizing forward error correction coding and decoding modes

A forward error correction coding and forward error correction technology, which is applied in the field of synchronization methods and devices for forward error correction coding and decoding modes, can solve problems such as different coding and decoding modes and business interruption, and achieve the goal of reducing the probability of business interruption Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

[0051] In this example, pure software is used to process FEC codec synchronization. image 3 It is a flow chart of the pure software synchronization method processing of the OTN overhead reserved byte mode receiving end FEC coding mode according to the embodiment of the present invention, as image 3 As shown, the process includes the following steps:

[0052] Step S301, the FEC uncorrectable error exceeds the limit? If the judgment result is yes, execute step S302. It should be noted that there are two situations in which an uncorrectable error exceeds the limit of FEC, the first is caused by a different FEC codec mode, and the second is caused by an error during transmission. Steps S302 to S305 are used to determine whether the FEC uncorrectable error exceeds the limit due to the replacement of the FEC code. Steps S306 and S307 are when the FEC uncorrectable error exceeds the limit and is not caused by the difference in the codec mode. The next processing.

[0053] Step ...

example 2

[0062] Figure 4 It is a structural block diagram of a device that combines software and hardware in an OTN overhead reserved byte mode receiving end FEC coding mode and a synchronization method according to an embodiment of the present invention, as shown in Figure 4 As shown, the reception processing module 40 is an existing OTN reception processing unit, the extraction module 50 is an FEC encoding type ID extraction unit, and the control module 60 is a control unit. After the optical path OTN signal is photoelectrically converted, two parallel outputs are output, and one input receives The processing module 40 has one input to the extraction module 50. After the signal input to the extraction module 50 is descrambled, FEC error correction is not performed, but under the control of the control module 60, the FEC encoding type is directly extracted from the overhead reserved bytes according to the row and column information. ID, the control module 60 controls the receiving p...

example 3

[0064] Figure 5 It is a structural block diagram of a device for implementing FEC encoding mode synchronization using a pure ASIC logic chip according to an embodiment of the present invention, such as Figure 5 As shown, the first extraction module 100 is a frame extraction module, the processing module 200 is a frame processing module, and the first extraction module 100 includes three processing units: a first processing unit 70, a second processing unit 80, and a third processing unit 90, Wherein, the first processing unit 70 implements descrambling processing, the second processing unit 80 extracts the FEC encoding mode ID from the reserved bytes of the current OTN frame, and the second processing unit 80 controls the third processing unit 90 according to the extracted FEC encoding mode ID Decode and correct the next OTN frame to achieve synchronization with the FEC coding mode at the sending end.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com