Thread dispatching implementation method based on on-chip multiprocessor

A technology of on-chip multiprocessors and implementation methods, applied in the field of thread scheduling implementation based on on-chip multiprocessors, can solve the problems of huge operating system code, thread scheduling efficiency, low real-time performance, and not suitable for hard real-time systems, etc. Achieve good real-time performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

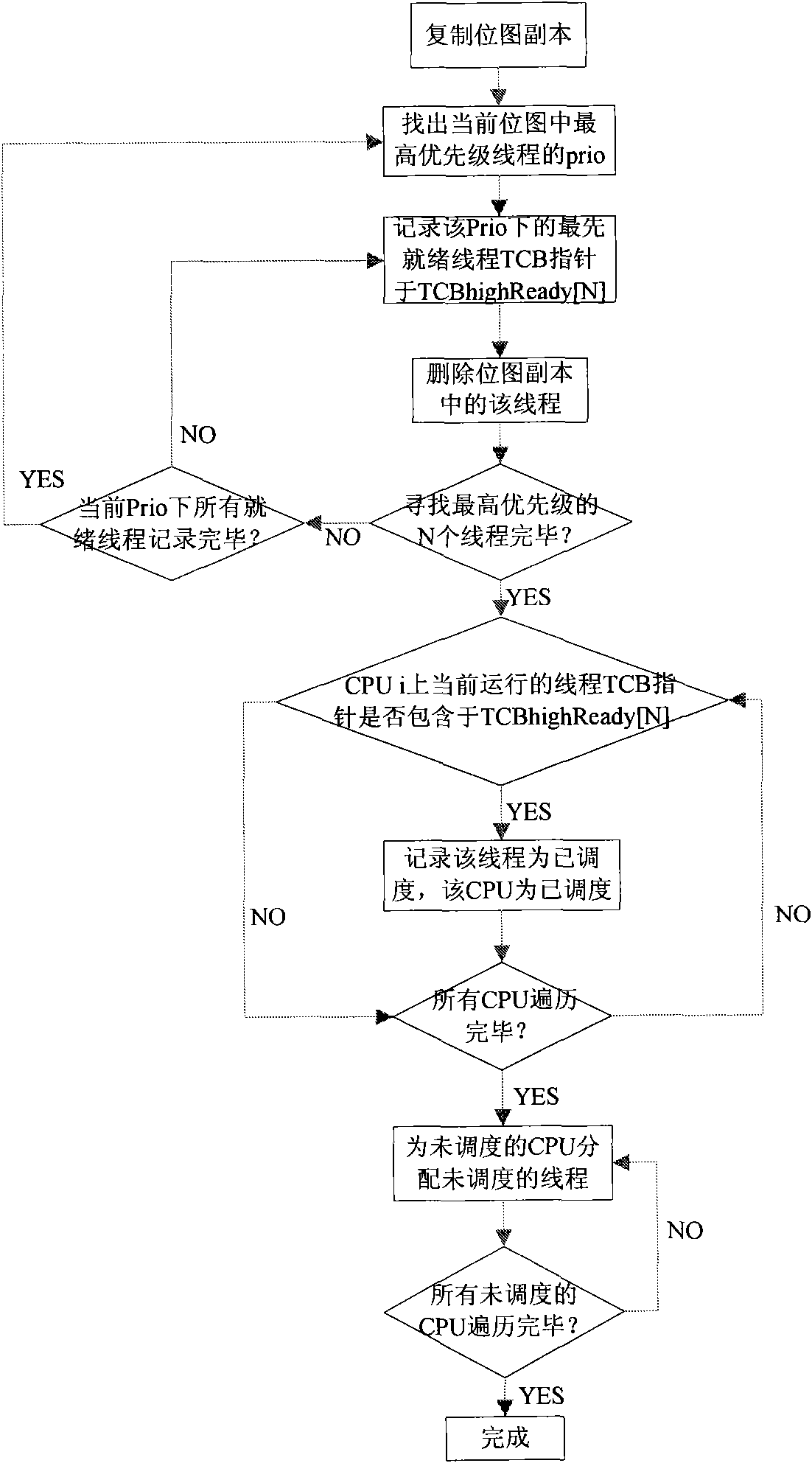

[0022] The implementation method of thread scheduling based on on-chip multiprocessor includes the following processes:

[0023] 1) Definition of thread control block.

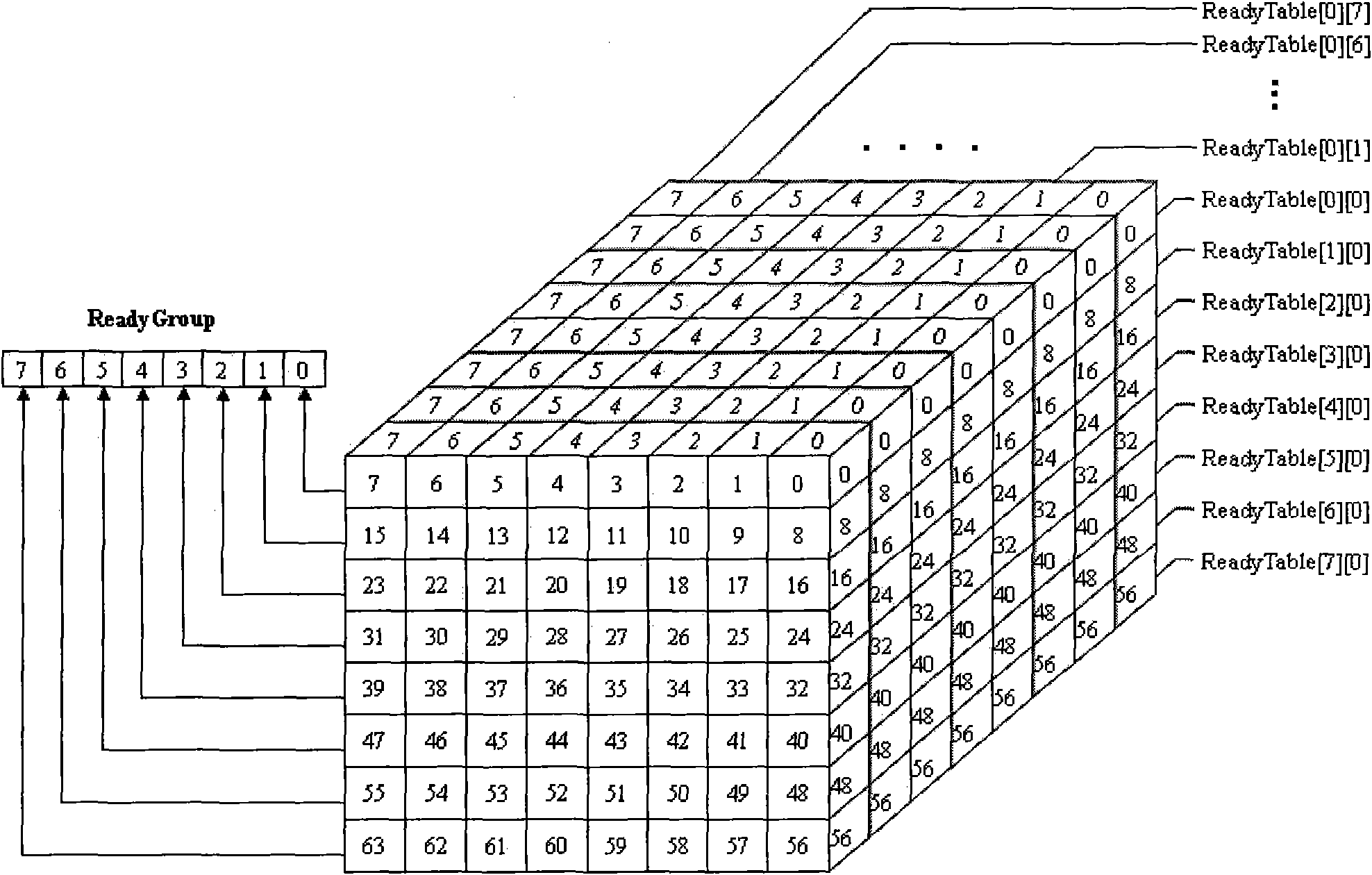

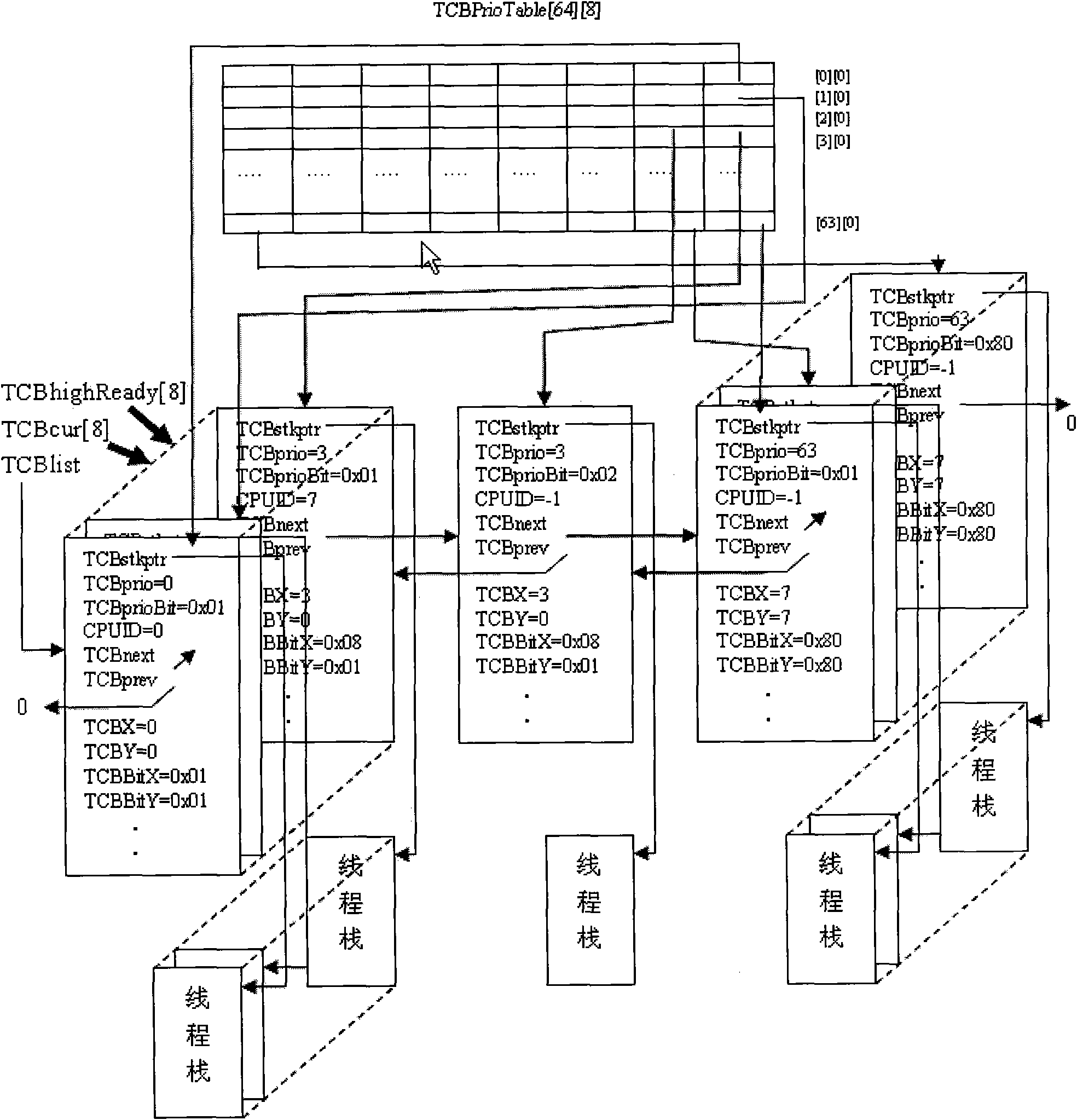

[0024] A thread control block (Thread Control Block, TCB) is a data structure containing thread-related information, including all the information required during thread execution. Its member variables include: pointer to the thread stack (TCBstkptr), thread priority (TCBprio), thread priority bit, record the position of the same priority thread in the bitmap (TCBprioBit), record whether the thread is scheduled and is Scheduled CPU number, unscheduled is -1 (CPUID), the front and rear thread control blocks (TCBnext, TCBprev) pointing to the thread in the doubly linked list, the position of the thread control block (TCBX, TCBY, TCBBitX, TCBBitY) (these four items are used To accelerate the thread to enter the ready state, assign values when the thread is created and initialized) and other variables.

[00...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More