Configurable on-chip testing module supporting encapsulation of different pins of chip

A technology of testing modules and pins, which is applied in the field of testing modules, can solve problems such as testing compatibility issues, and achieve the effects of wide testing range, flexible and targeted development, and strong versatility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

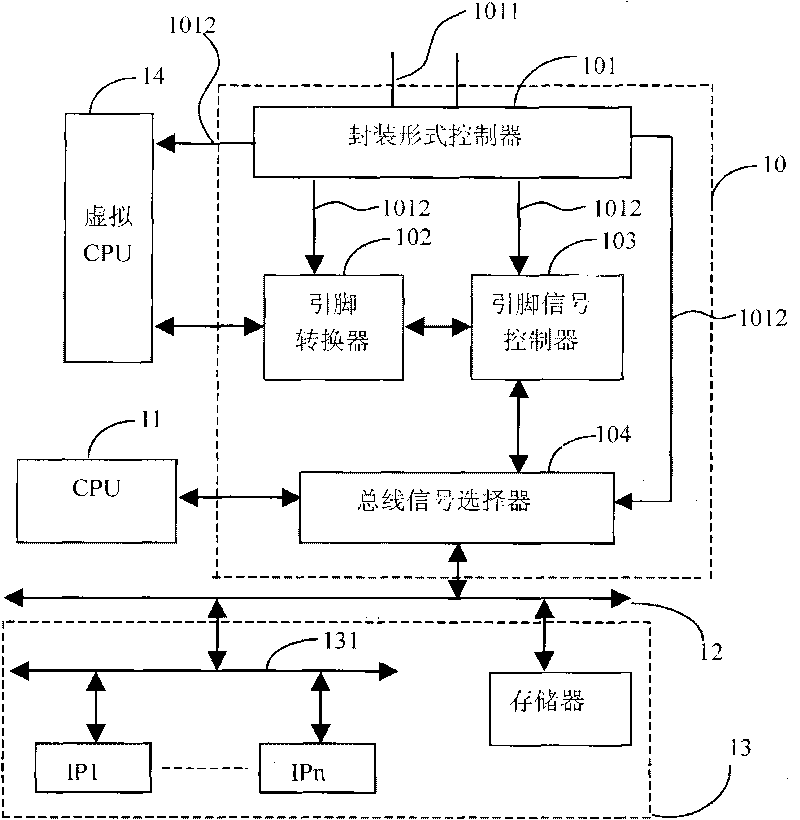

[0038] Embodiment: A configurable on-chip test module that supports packaging of different pins of the chip

[0039] figure 1 It is a block diagram of the principle of the present invention. It can be seen from the figure that the chip is composed of CPU 11, bus 12, test module 10 and module group 13. Module group 13 includes memory, IP1~IPn application modules, and IP1~IPn application modules pass IP The bus 131 is connected to the bus 13 . The virtual CPU 14 is an incentive controller for reading and writing operations in the simulation test outside the chip.

[0040] The test module 10 will be described in detail below:

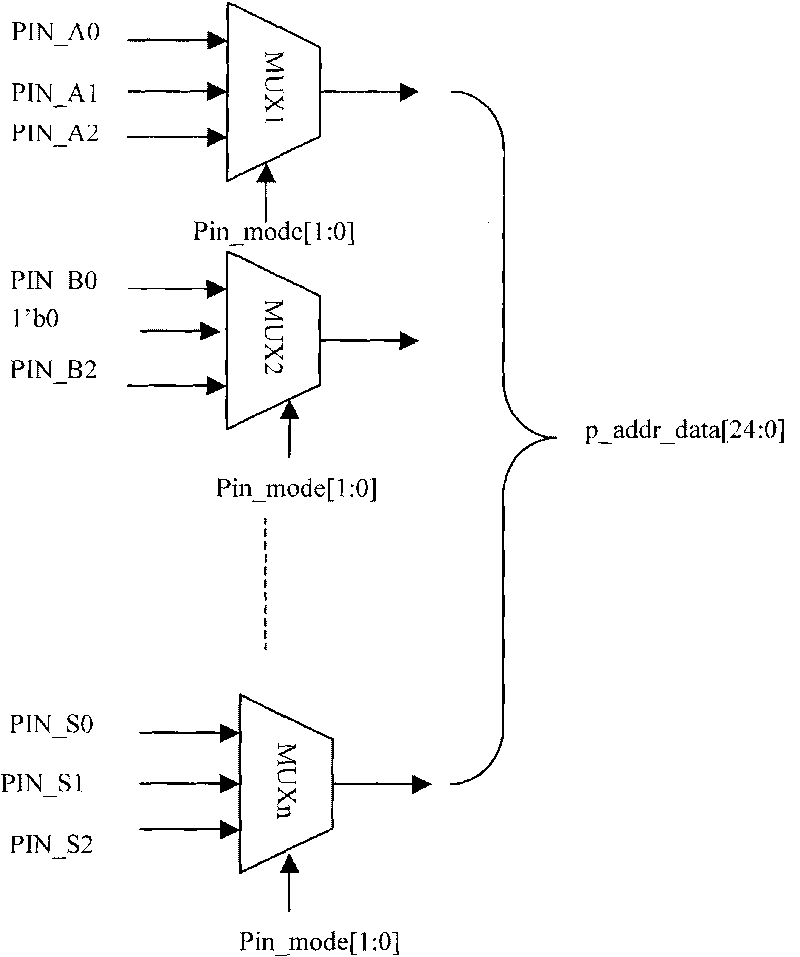

[0041] Such as figure 1 As shown, the test module 10 of the present invention is composed of a package type controller 101 , a pin converter 102 , a pin signal controller 103 and a bus signal selector 104 . The details of each component are as follows:

[0042] 1. Package type controller 101

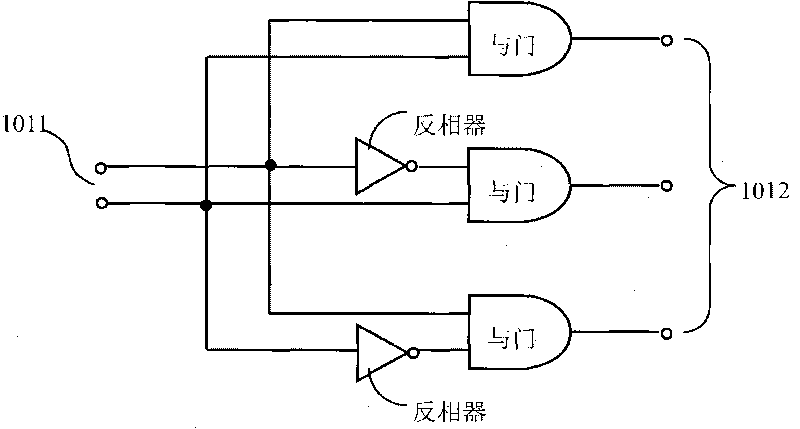

[0043] Package form controller 101 is provided by input p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More