MOS (Metal Oxide Semiconductor) transistor and fabricating method thereof

A technology of a MOS transistor and a manufacturing method, which is applied to the field of MOS transistors and their manufacturing, can solve the problems of control and matching affecting the threshold voltage of the transistor, and enhance the diffusion of impurities, and achieve the effects of suppressing transients and enhancing the diffusion effect.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] Below by describing specific embodiment in detail according to accompanying drawing, above-mentioned object and advantage of the present invention will be clearer:

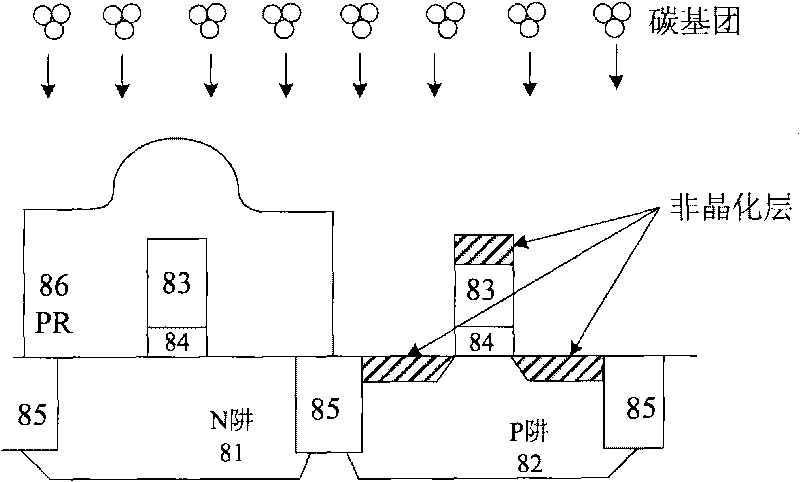

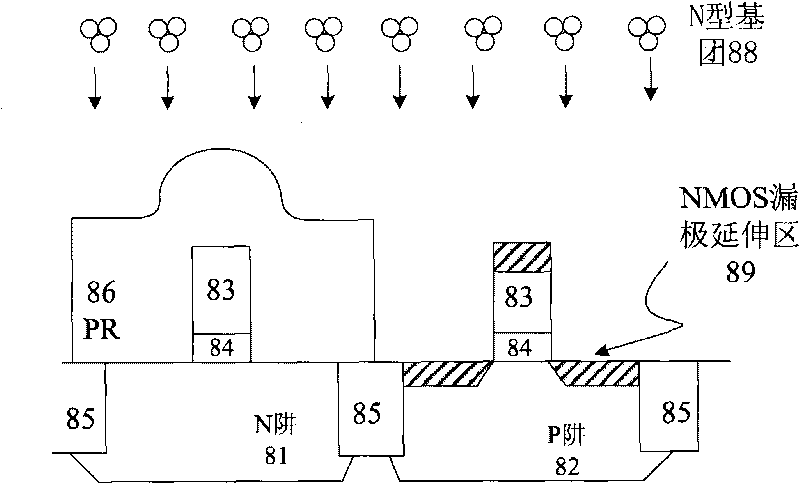

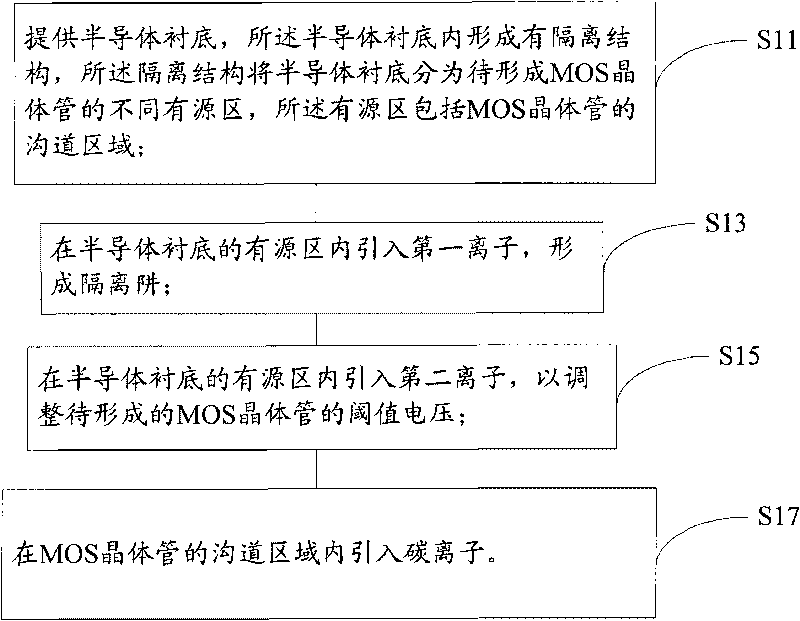

[0036] The present invention firstly provides a manufacturing method of a MOS transistor, please refer to figure 1 , including: performing step S11, providing a semiconductor substrate, an isolation structure is formed in the semiconductor substrate, and the isolation structure divides the semiconductor substrate into different active regions where MOS transistors are to be formed, and the active regions include MOS The channel region of the transistor; perform step S13, introduce the first ion in the active region of the semiconductor substrate to form an isolation well; perform step S15, introduce the second ion in the active region of the semiconductor substrate, to adjust the threshold voltage of the MOS transistor; execute step S17 to introduce carbon ions into the channel region of the MOS transistor...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap