Design method of NES (Nintendo Entertainment System) emulator used on TV set top box

A design method and simulator technology, applied to color TV parts, TV system parts, TVs, etc., to achieve the effects of low hardware configuration requirements, high execution efficiency, and convenient transplantation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

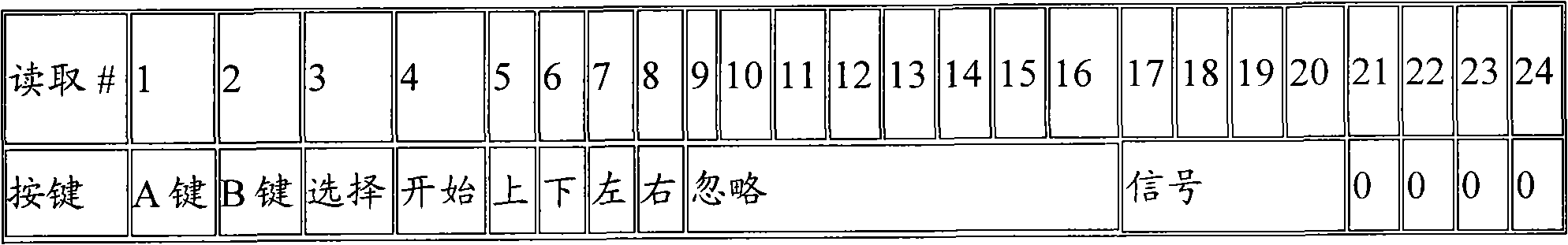

[0029] The design method of the NES emulator that the present invention uses on the TV set-top box comprises: one, the simulation to the instruction of 6502cpu; Two, the simulation to NES core component PPU graphics processor; Three, the optimization process to graphics buffer mechanism; Four, The simulation of the sound processor; five, the simulation of the handle controller; and, six, the analysis of the NES game file format.

[0030] 1. Simulation of 6502cpu: In this part, pure C language is used to simulate 131 different instructions of 6502. The purpose of not using assembly language related to the processing chip of the set-top box is to further improve the portability of the whole simulator. Although pure C language is slower than the 6502 simulator written in assembly language in terms of running speed, it can be effectively and quickly ported to different set-top box platforms (different set-top box platforms have different CPU types and different instruction sets) ....

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com