Reliability test method

A test method and reliability technology, applied in static memory, instruments, etc., can solve the problems of time delay, long total time, and impact on chip production in mass production of chips

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

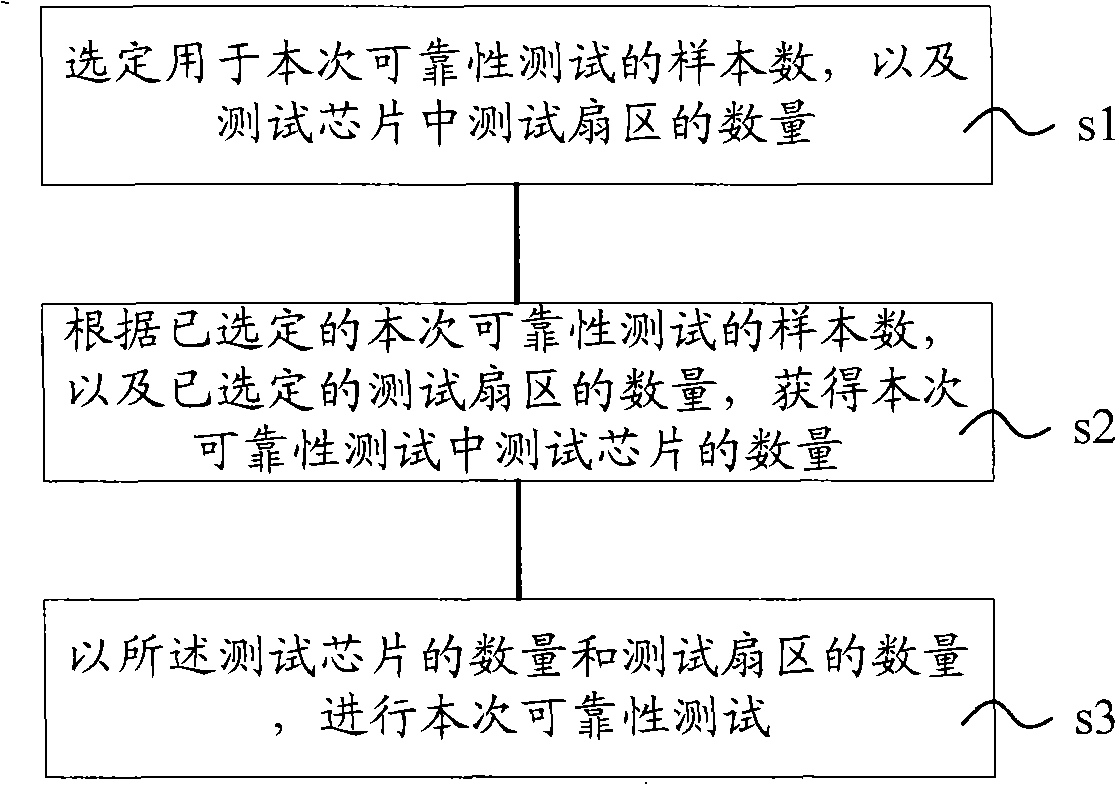

[0017] refer to figure 2 Shown, a kind of embodiment of reliability testing method of the present invention comprises:

[0018] Step s1, selecting the number of samples for this reliability test and the number of test sectors in the test chip;

[0019] Step s2, according to the number of samples selected for this reliability test and the number of selected test sectors, the number of chips tested in this reliability test is obtained;

[0020] Step s3, performing this reliability test with the number of test chips and the number of test sectors,

[0021] Wherein, the number of samples of the reliability test is directly proportional to the product of the number of test chips in the reliability test and the number of test sectors in the test chip.

[0022] In the above reliability testing method, the number of samples of this reliability test is directly proportional to the product of the number of test chips in this reliability test and the number of test sectors in the test...

example 1

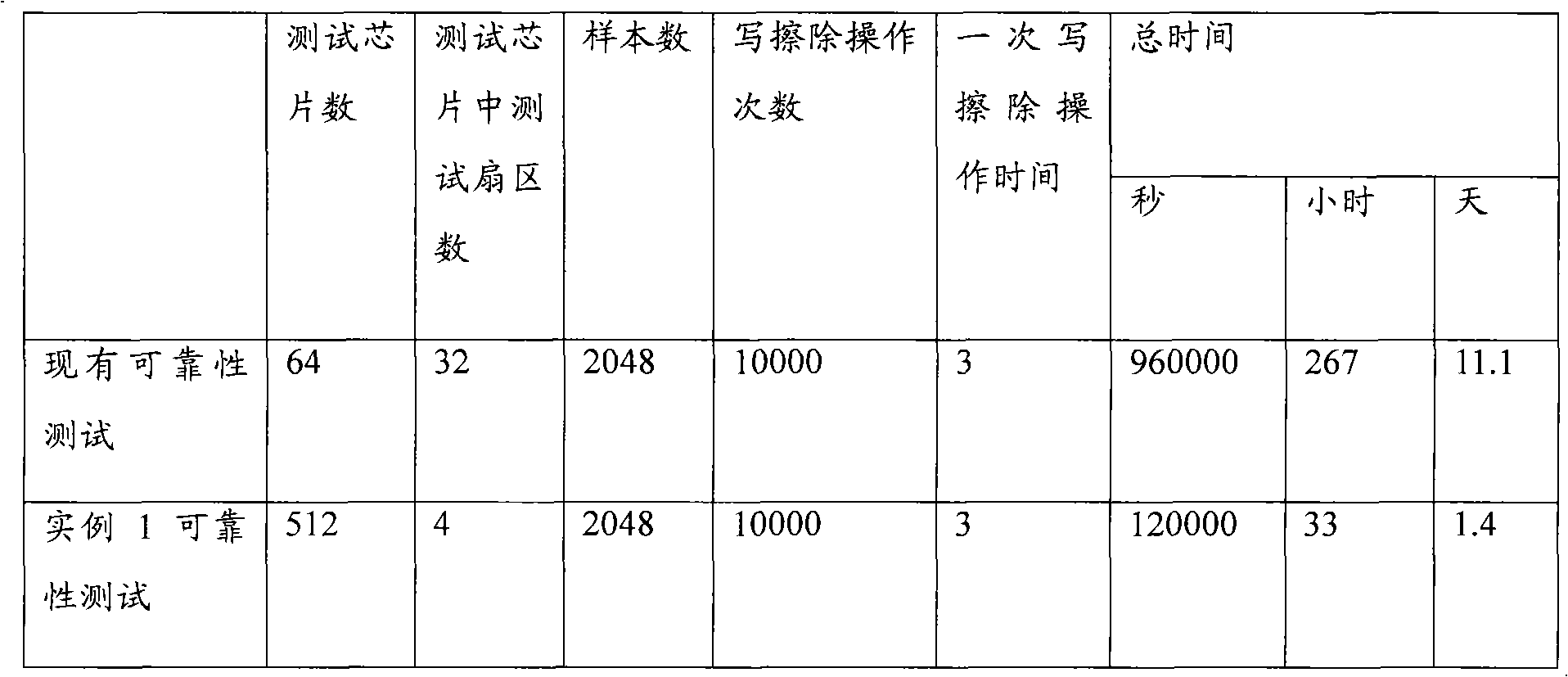

[0026] In this example, the existing reliability test mentioned above is used as a comparison. For the convenience of description, the number of non-volatile memory test chips selected in the existing reliability test method is N, and the number of test sectors in the corresponding test chip is n, while the non-volatile memory selected in the reliability test method of this example The number of memory test chips is M, and the number of test sectors in the corresponding test chip is m. According to the description of the reliability test method in the embodiment of the present invention, and assuming that in the reliability test of this example, the factors affecting the test results are exactly the same as those of the existing reliability test, for example, the test results are only affected by the performance of the memory cell array, then Have:

[0027] S=n×N=m×M (1)

[0028] In the conventional reliability test mentioned above, 64 non-volatile memory chips are selected ...

example 2

[0034] In Example 1, formula (1) is based on the assumption that the factors affecting the test results are exactly the same as the existing reliability tests. In some cases, the factors affecting the test results are not exactly the same with the number of test sectors. For example, for a non-volatile memory chip, it is not only the performance of the memory cell array that affects the test results, but also the performance of peripheral circuits. For example, in the process of cyclic writing and erasing operations on a non-volatile memory chip, both the memory cell array and peripheral circuits will be affected by stress. Therefore, the test sector is different, and the number of times of stress on the peripheral circuit is also different. Since the degradation of the performance of the peripheral circuit will also cause the failure of the test chip, the change of the number of test sectors will also lead to the change of the failure probability of the test chip.

[0035] ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More