Dual-loop tuning method for low-vibration high frequency difference frequency and phase locking and electrical architecture thereof

An adjustment method and low-jitter technology, applied in the electrical field, can solve the problems of increasing the high-frequency jitter of the recovered clock, large loop gain, etc., and achieve the effect of avoiding the increase of high-frequency jitter

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

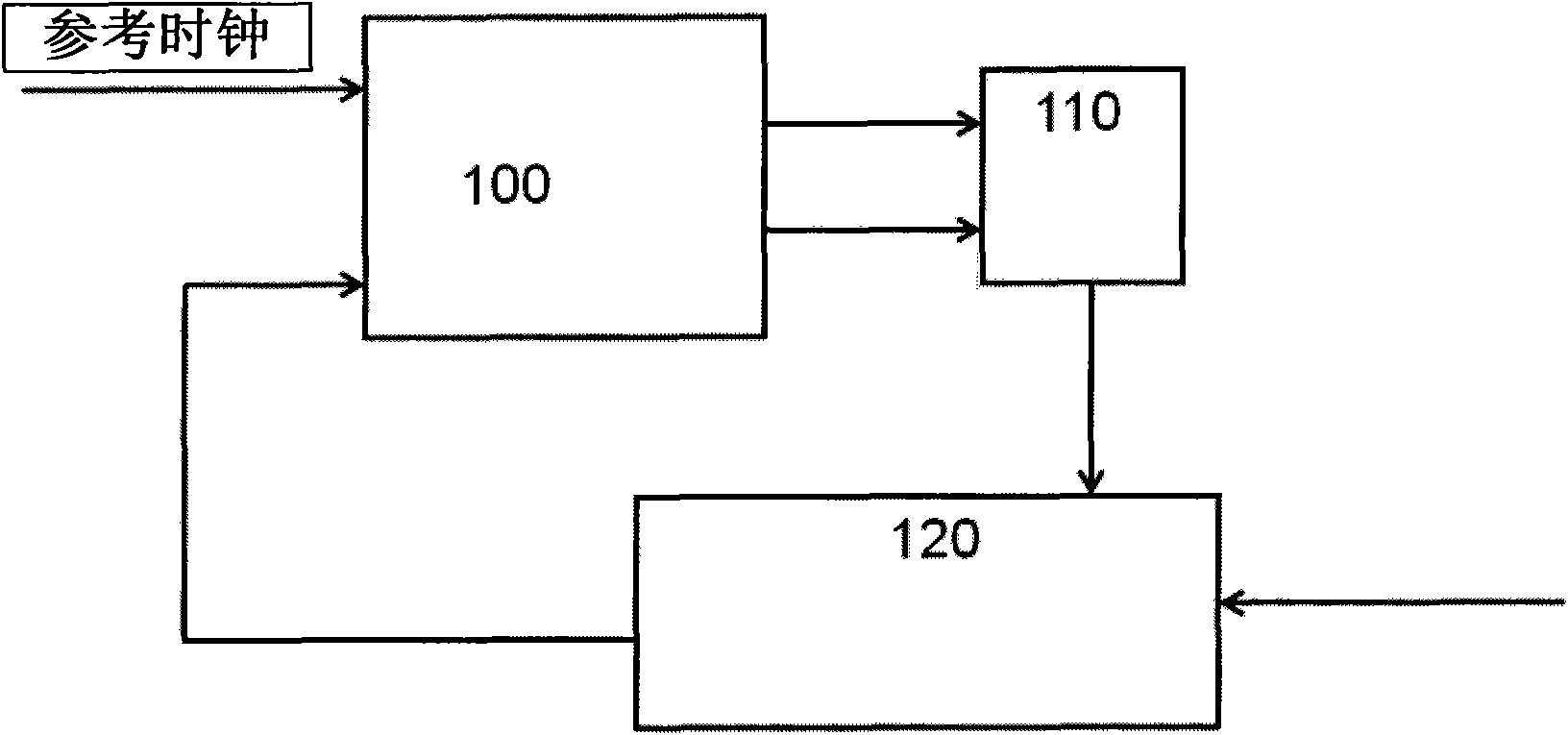

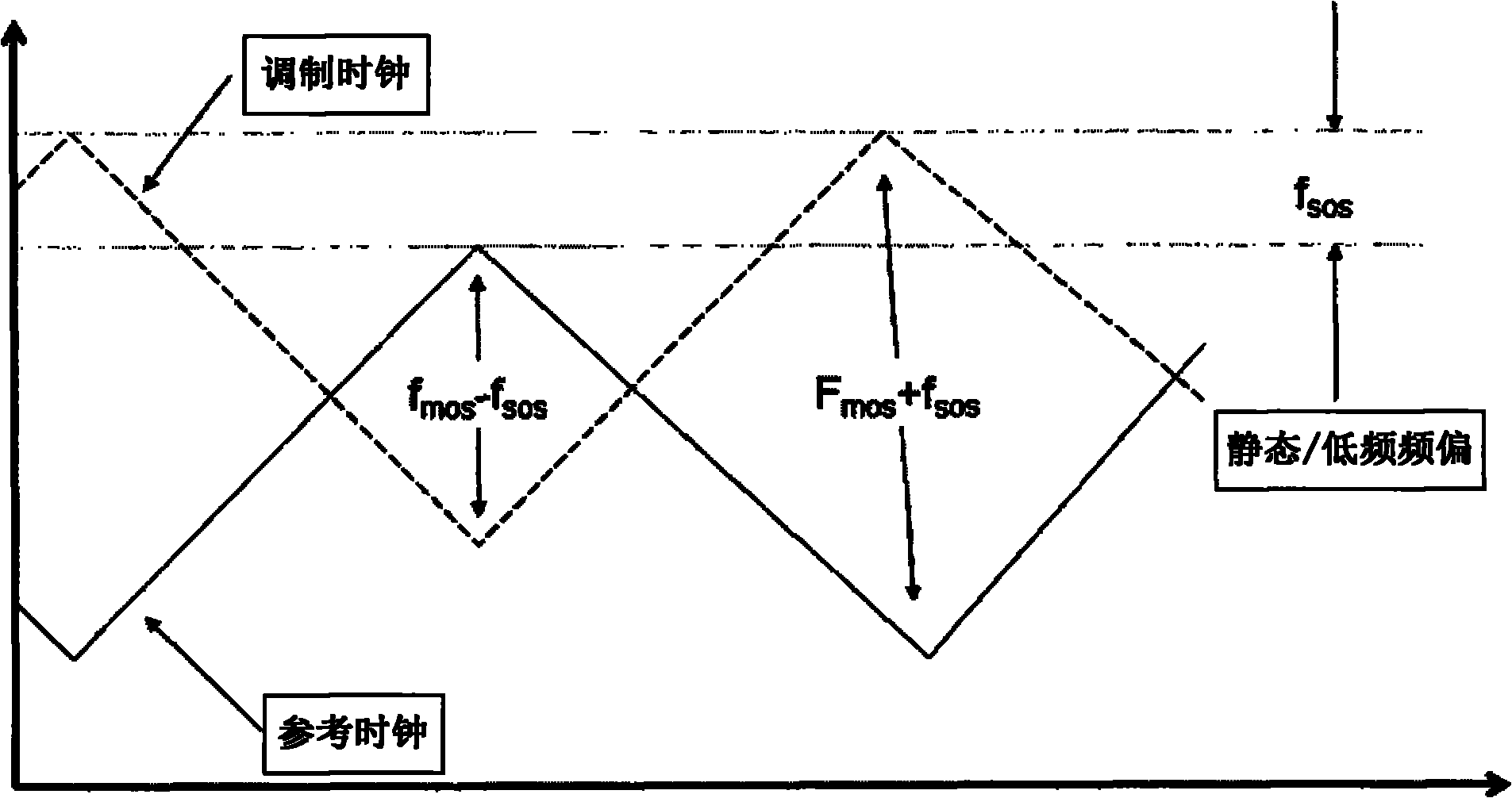

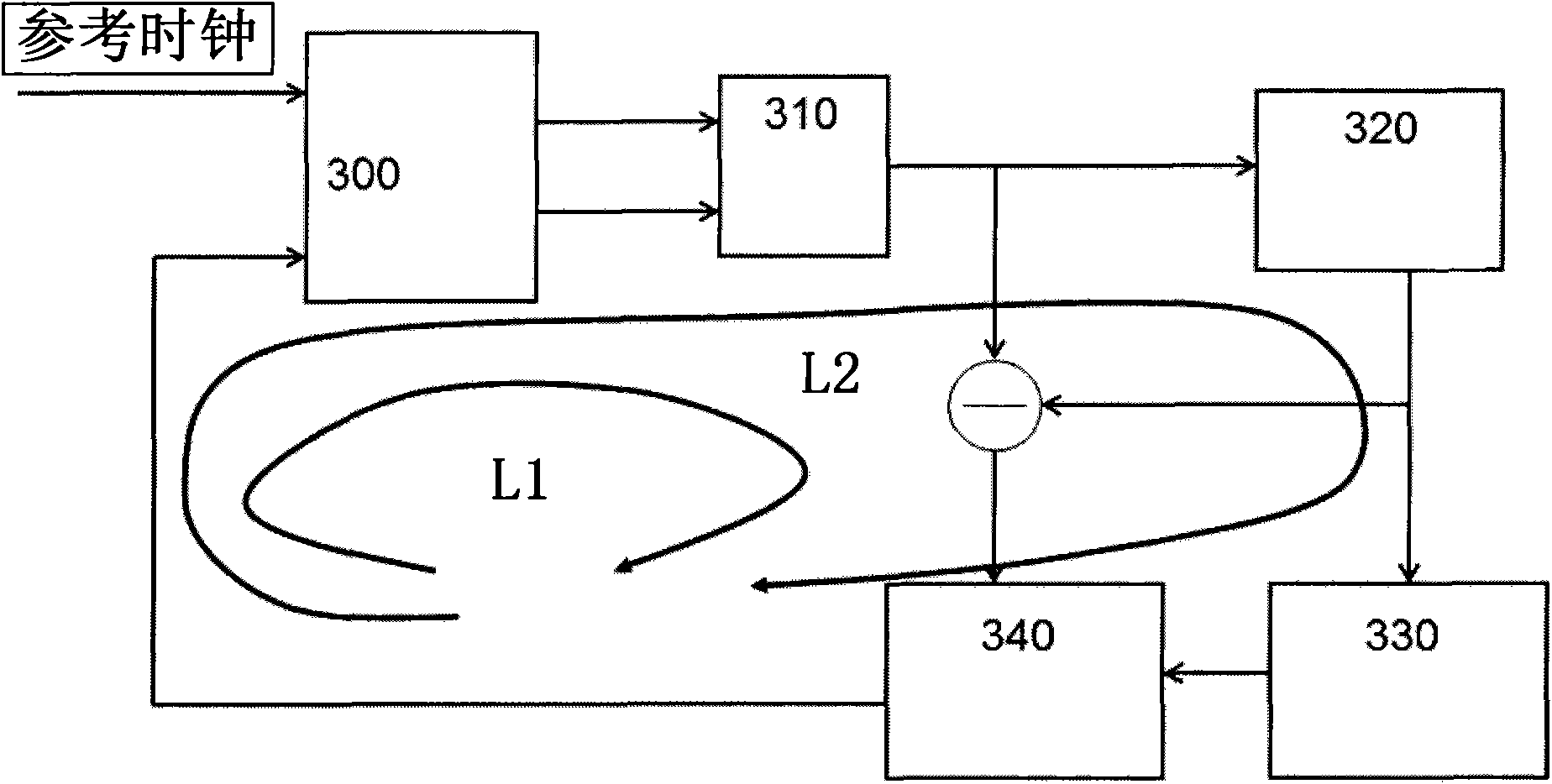

[0023] The specific implementation of the present invention will be described in further detail below in conjunction with the accompanying drawings of the embodiments, so that the details of the technical solution of the present invention can be displayed more comprehensively, and its essential features are easier to understand and grasp. It should be reminded that: the following narrations about the embodiments are not limiting, and those skilled in the art use other approaches to complete the same creations, although they are not specifically described, they are also included within the protection scope of the patent application for the present invention . The method of the present invention is I, determine the total real-time phase error between the reference clock and the feedback clock by an interpolator and a frequency detector; II, separate and extract the total real-time phase error into static / low-frequency frequency offset and The instant phase error of the two frequ...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap