Semiconductor shallow trench isolation method

A semiconductor and shallow trench technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as corner damage in the active area, device failure, and stress effects in the active area, and achieve the goal of reducing the impact Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

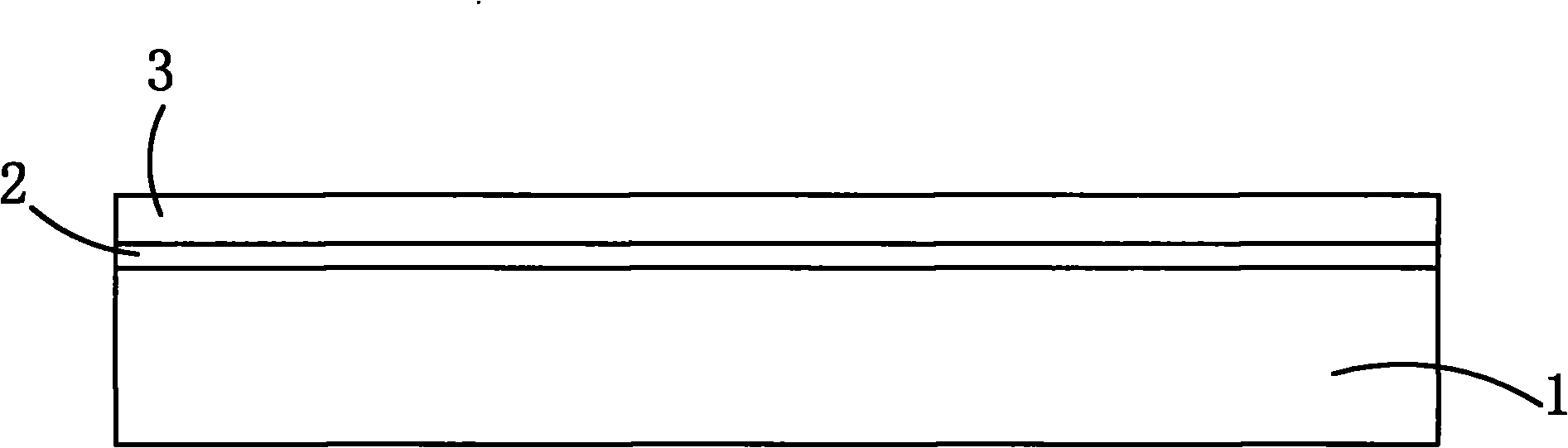

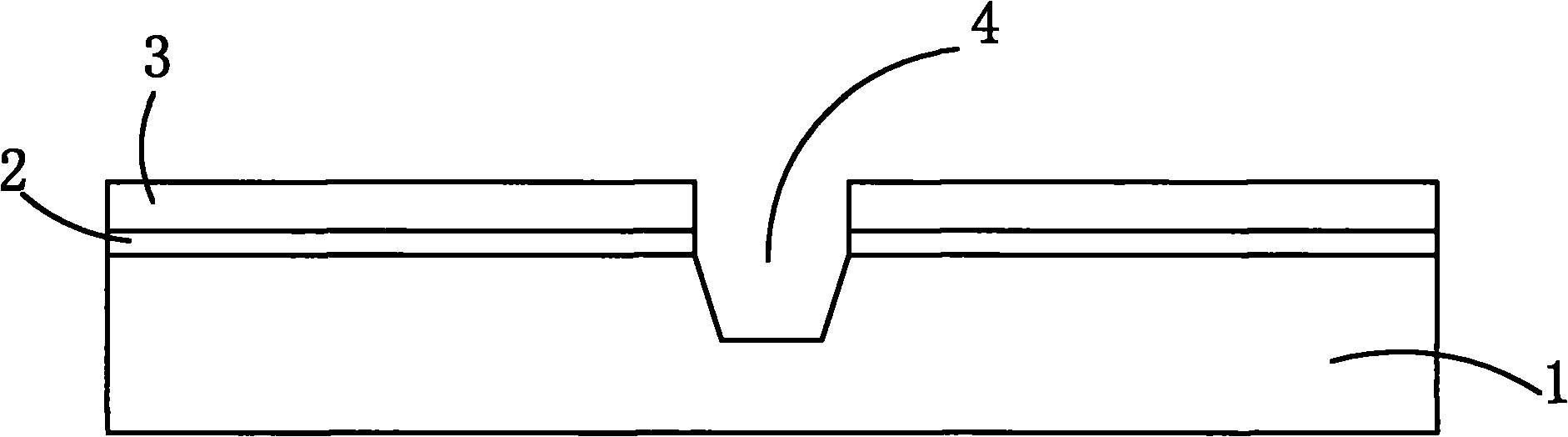

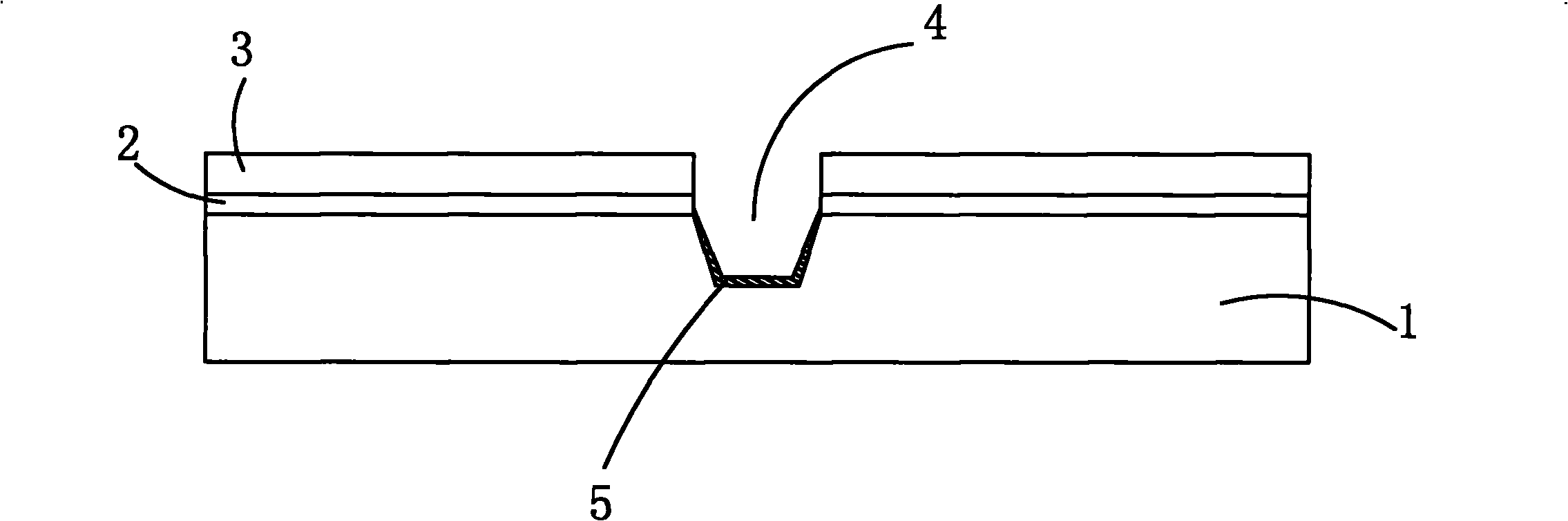

[0015] Those who are familiar with the field of semiconductor manufacturing process should know that in the manufacturing process of a semiconductor chip, it usually goes through many repeated steps of masking, photolithography, etching and ion implantation to form different semiconductor devices and interconnection structures between devices. Wait. The method involved in the present invention is one of the steps in the semiconductor chip manufacturing process, that is, a method for device isolation by using shallow trenches. Therefore, the steps of forming other components in the semiconductor manufacturing process will not be described in detail in this specification.

[0016] In addition, specific and detailed operation methods for various steps in the shallow trench isolation process, such as how to deposit an oxide layer or a silicon nitride layer, or how to etch a silicon oxide layer and a silicon nitride layer, etc. The operation method and other content are the same a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More