Integrated circuit structure and formation method thereof

An integrated circuit, gate dielectric technology, applied in circuits, electrical components, semiconductor devices, etc., to reduce the current crowding effect, increase tension and compressive stress

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] Several different embodiments are provided due to different features of the invention. The specific elements and arrangements in the present invention are for simplicity, but the present invention is not limited to these embodiments. For example, a description of forming a first element on a second element may include embodiments in which the first element is in direct contact with the second element, as well as embodiments having additional elements formed between the first element and the second element such that the second element An embodiment in which one element is not in direct contact with a second element.

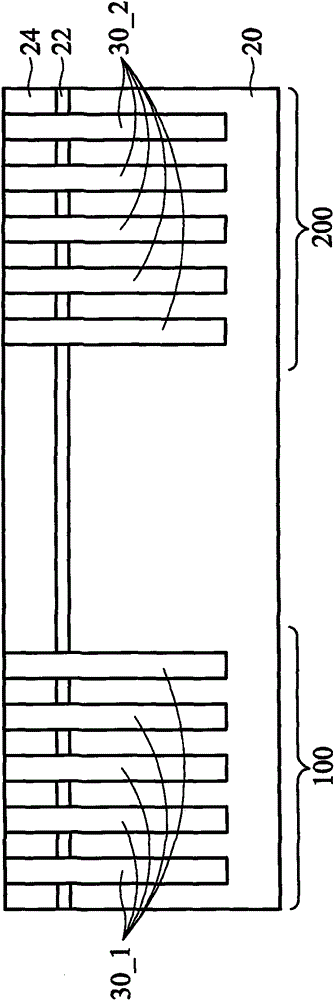

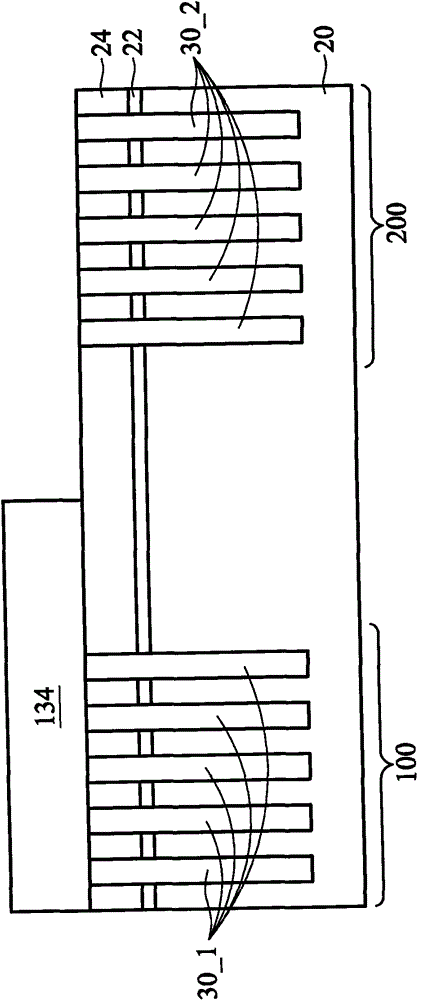

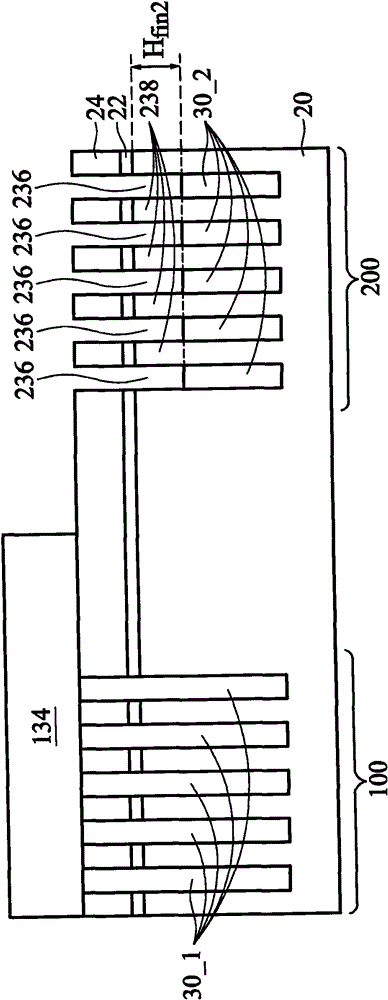

[0033] The present invention provides a novel method to form semiconductor fins and FinFETs with different fin heights. This disclosure illustrates intermediate steps in the manufacture of embodiments and discusses various embodiments. In the illustrations and descriptions of the respective embodiments, similar elements are denoted by similar reference nu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More