Improved power semiconductor device and preparation method thereof

An improved technology for power semiconductors, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of high device turn-on voltage, high production cost, complex process, etc., and achieve the effect of avoiding device damage and improving latch-up resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] In order to make the object, technical solution and advantages of the present invention more clear, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0015] In the description of the present invention, it should be understood that the terms "first" and "second" are used for description purposes only, and cannot be interpreted as indicating or implying relative importance or implicitly indicating the quantity of indicated technical features. Thus, a feature defined as "first" and "second" may explicitly or implicitly include one or more of these features.

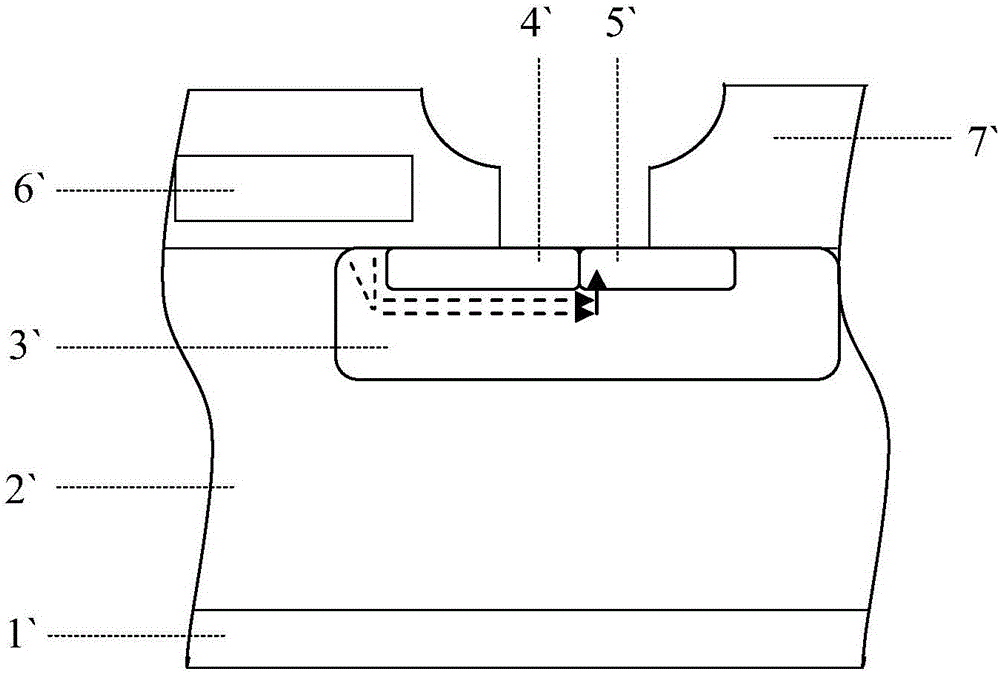

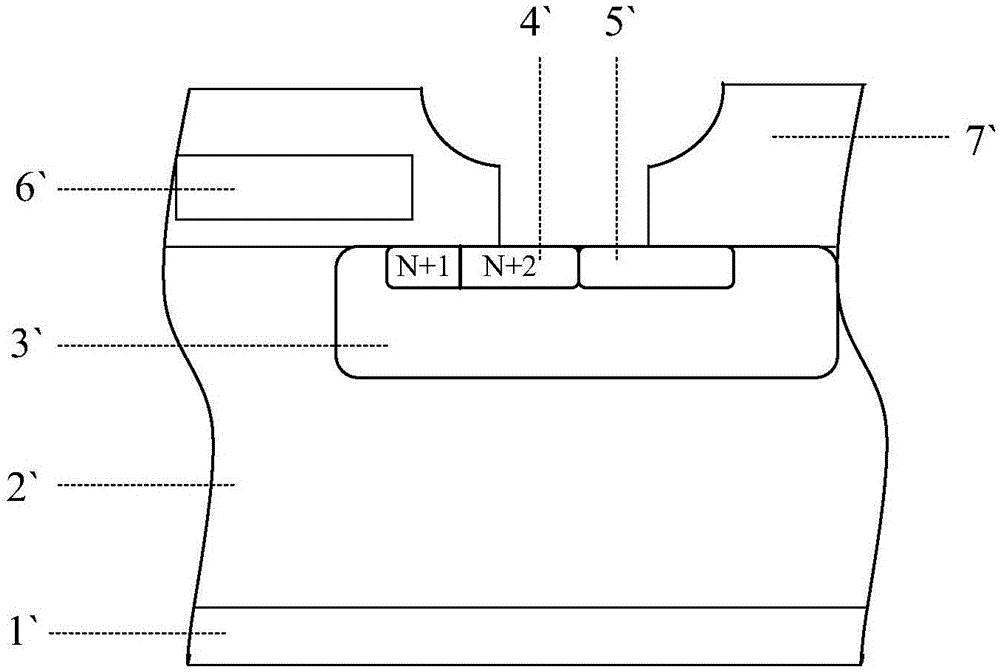

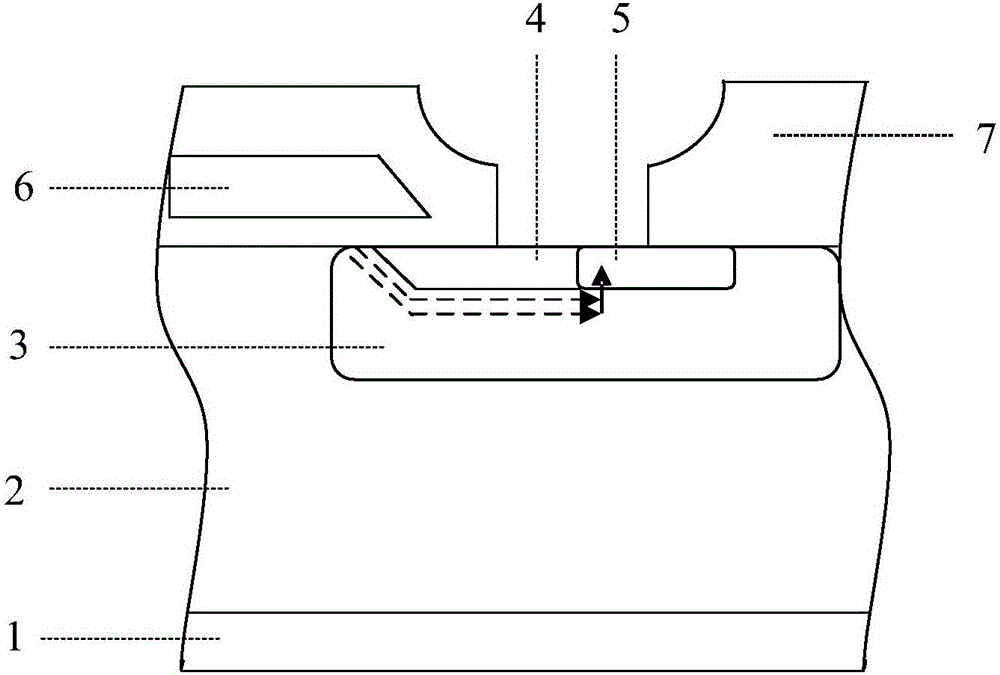

[0016] Such as image 3 As shown, one embodiment of the present invention provides an improved power semiconductor device, including a plurality of cellular MOS devices, the polycrystallin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More