Patents

Literature

162 results about "Fin height" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

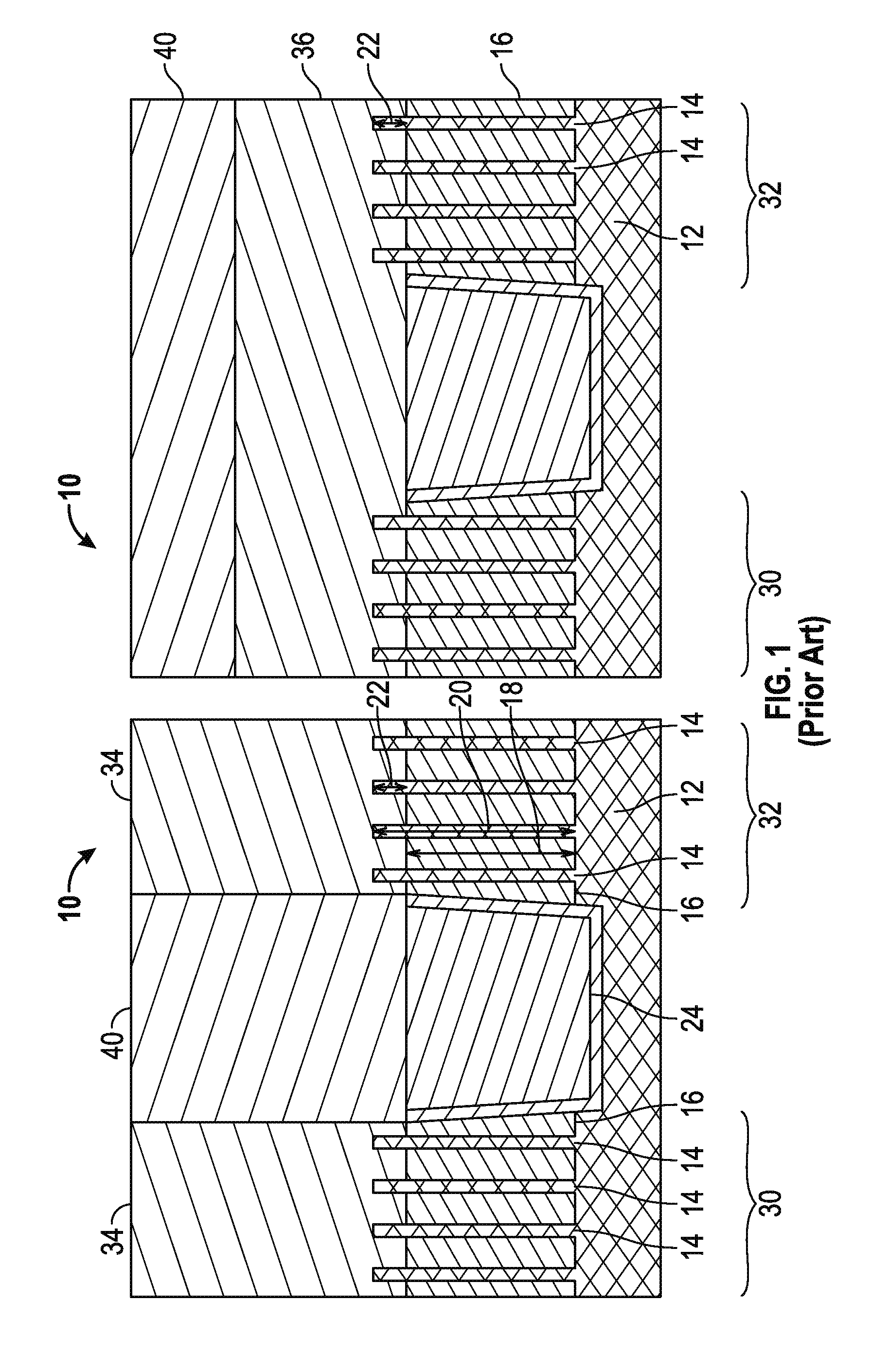

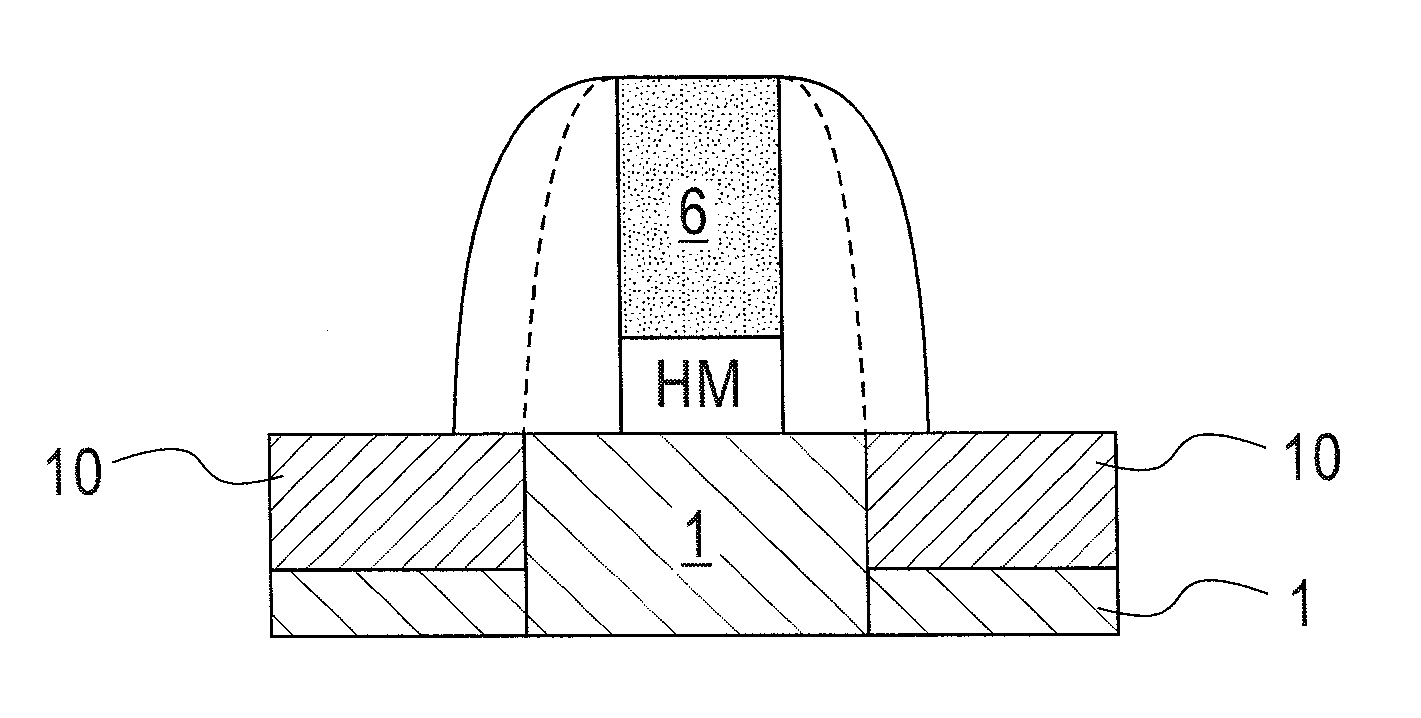

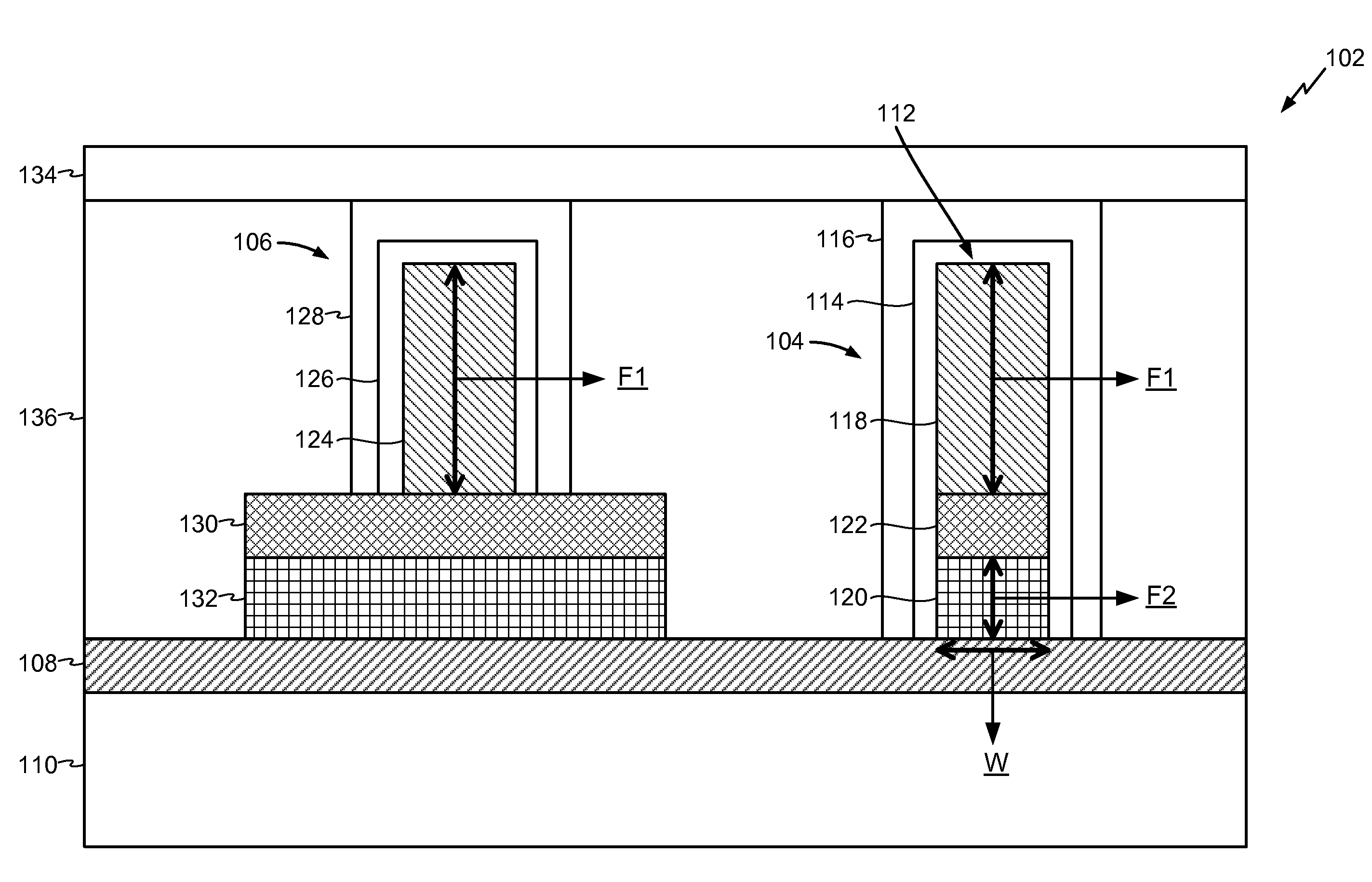

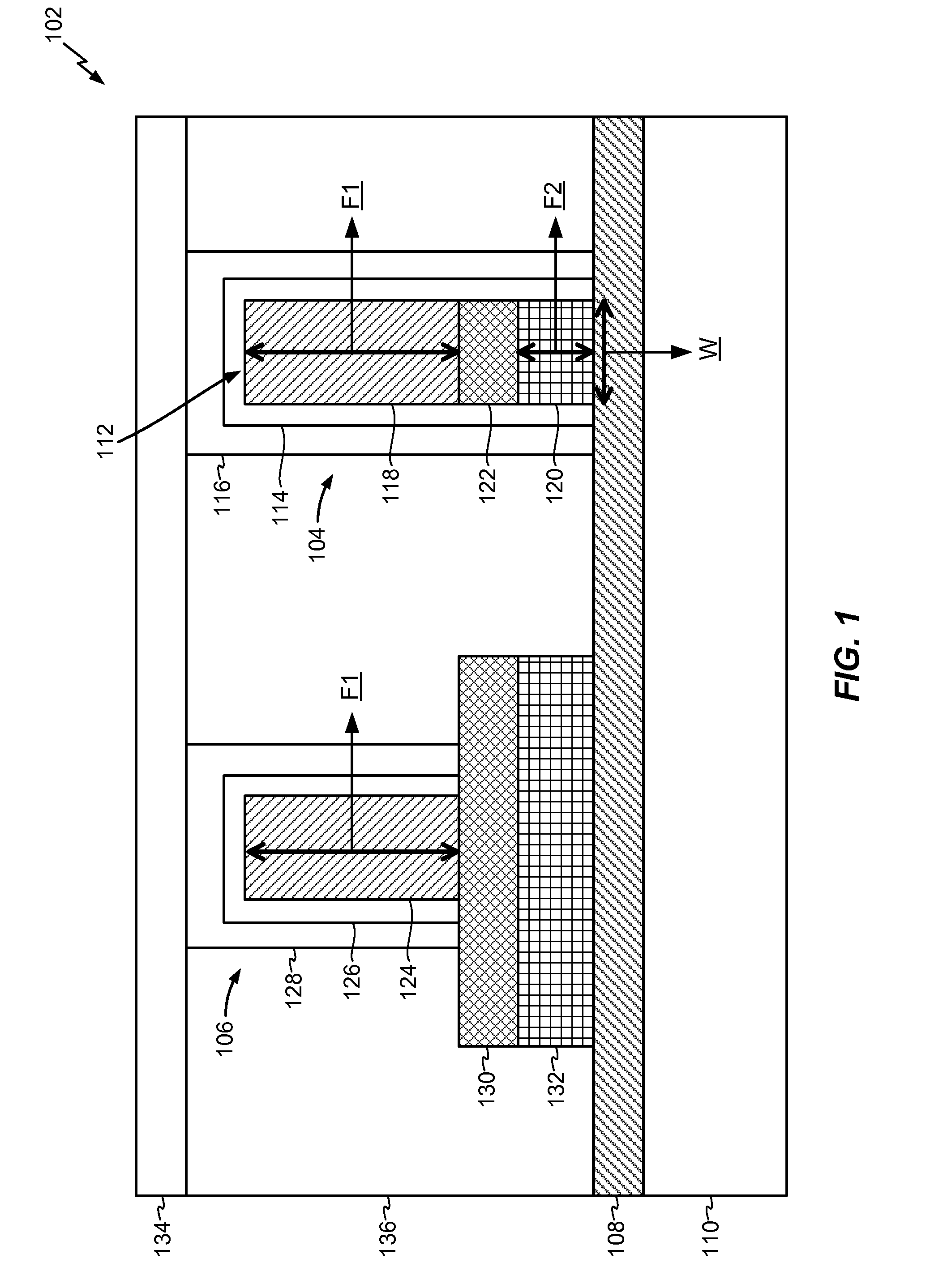

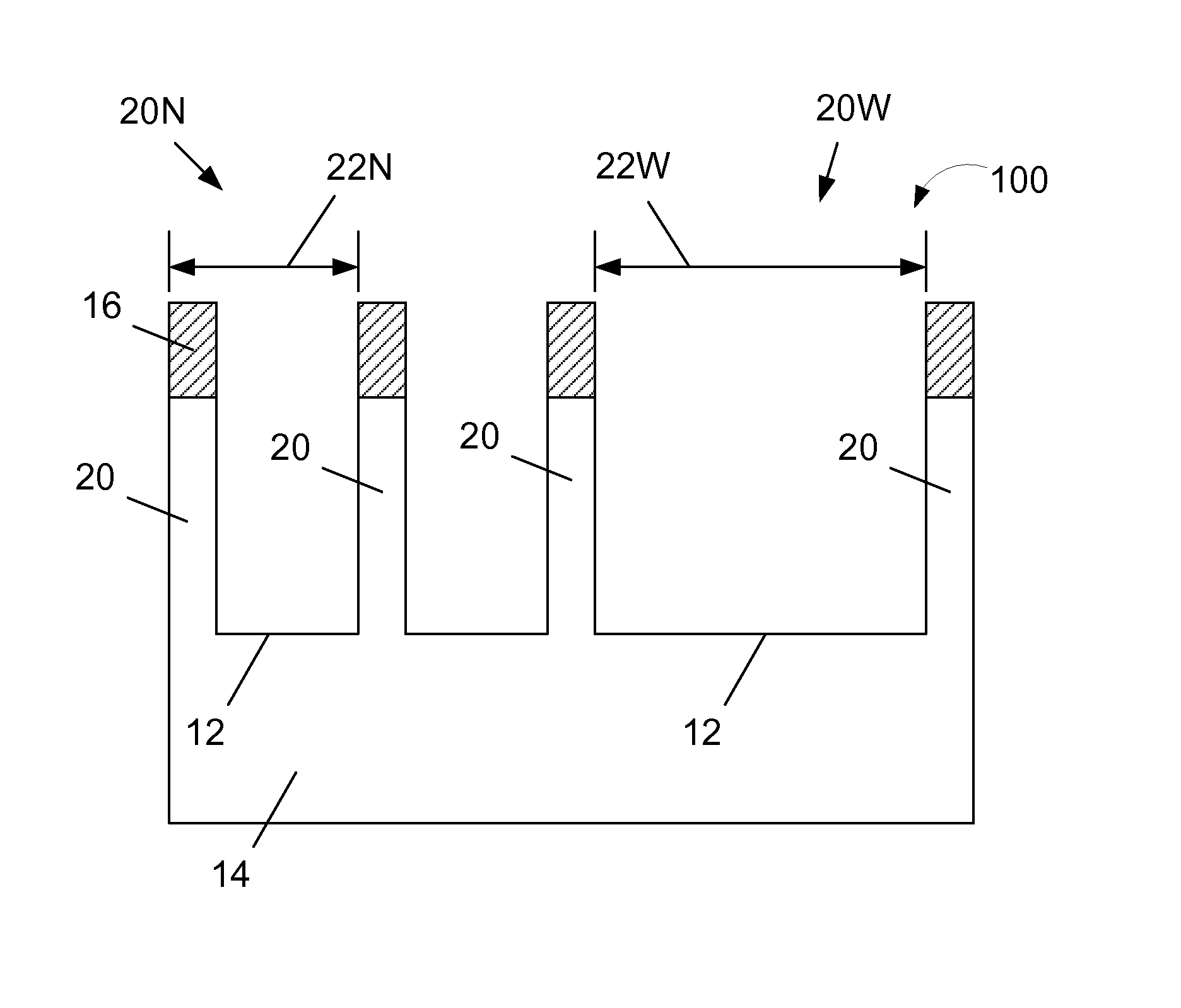

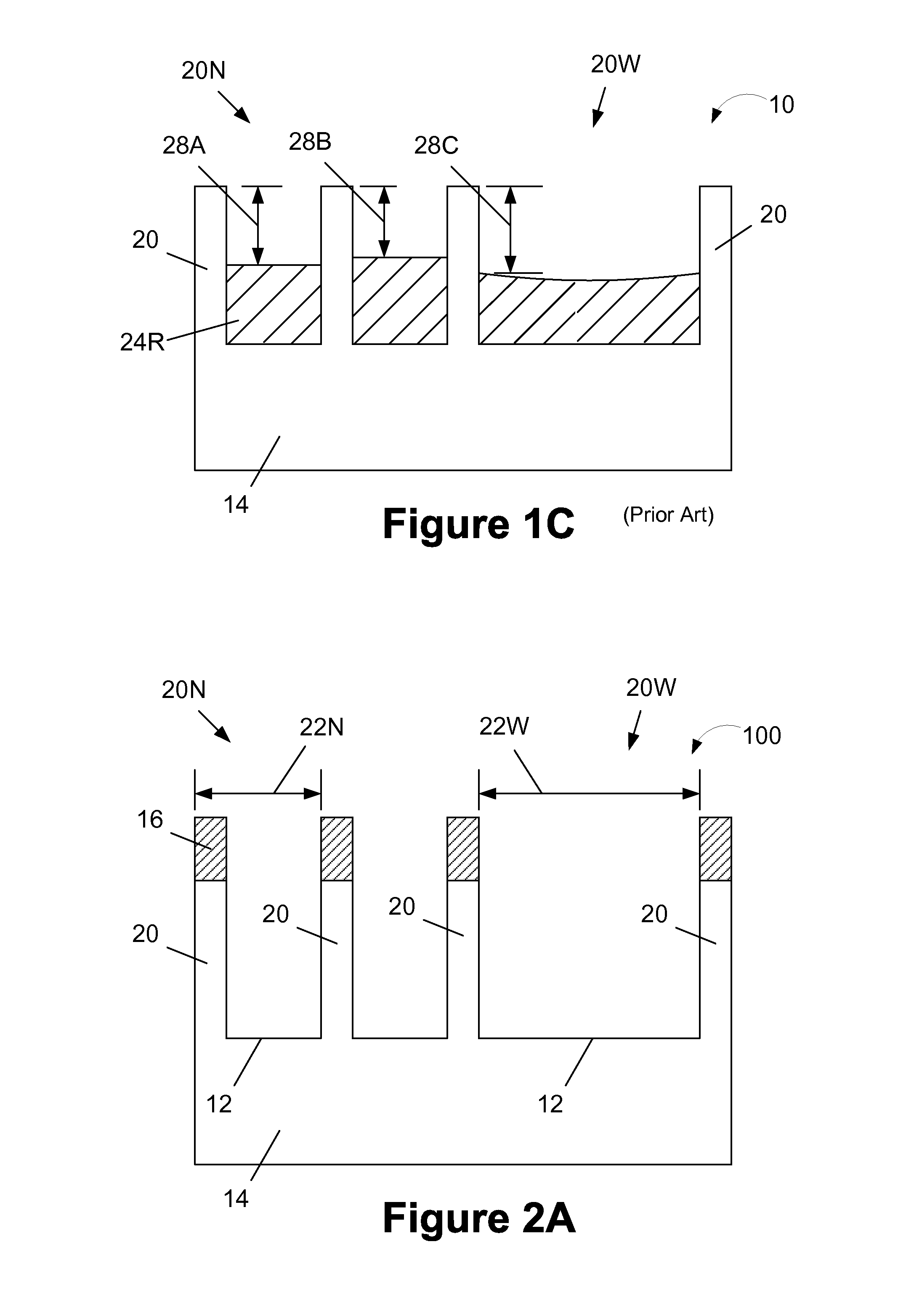

Dielectric Punch-Through Stoppers for Forming FinFETs Having Dual Fin Heights

ActiveUS20100163971A1Improved accuracy in formationTotal current dropTransistorSolid-state devicesDielectricSemiconductor structure

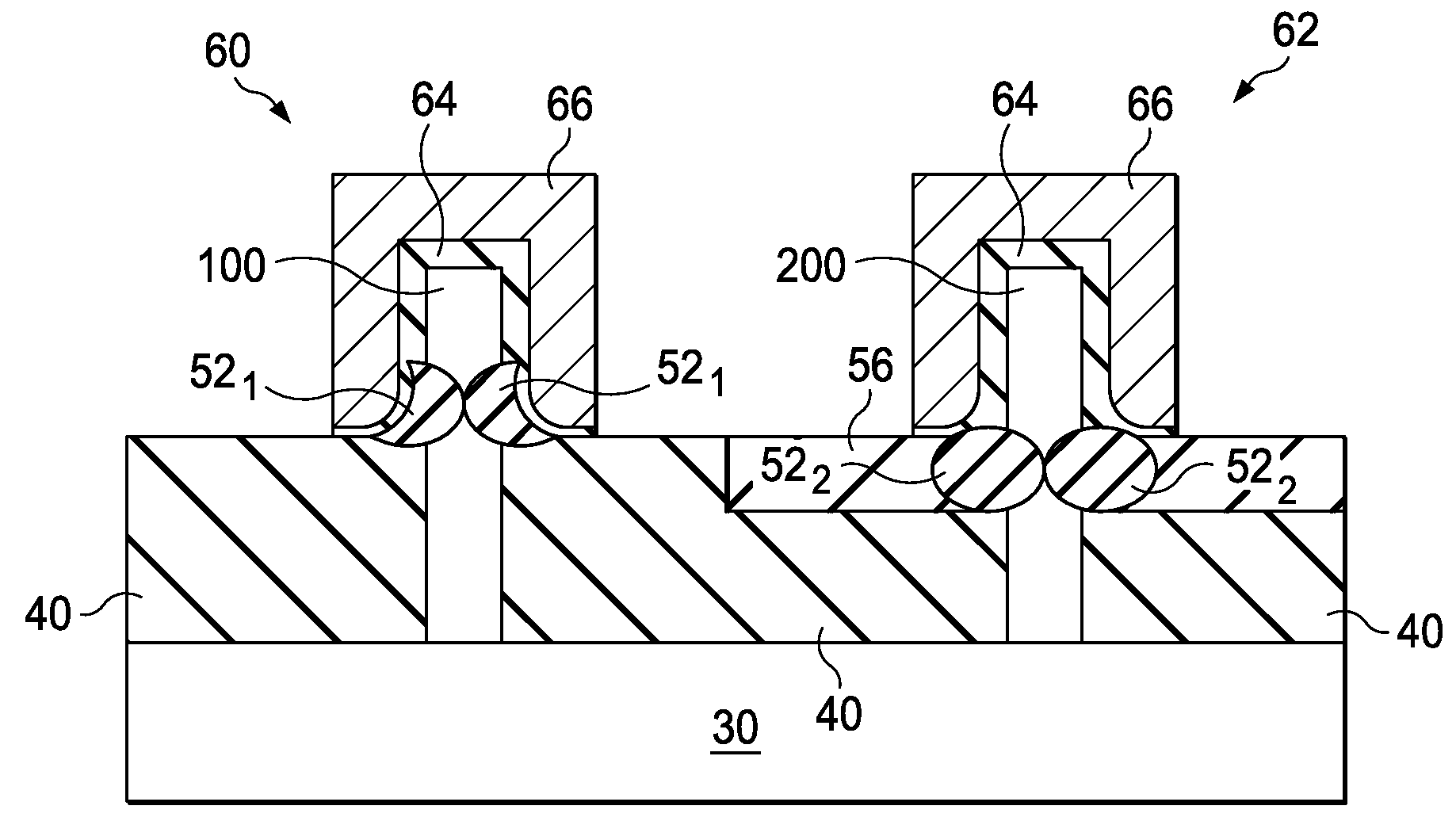

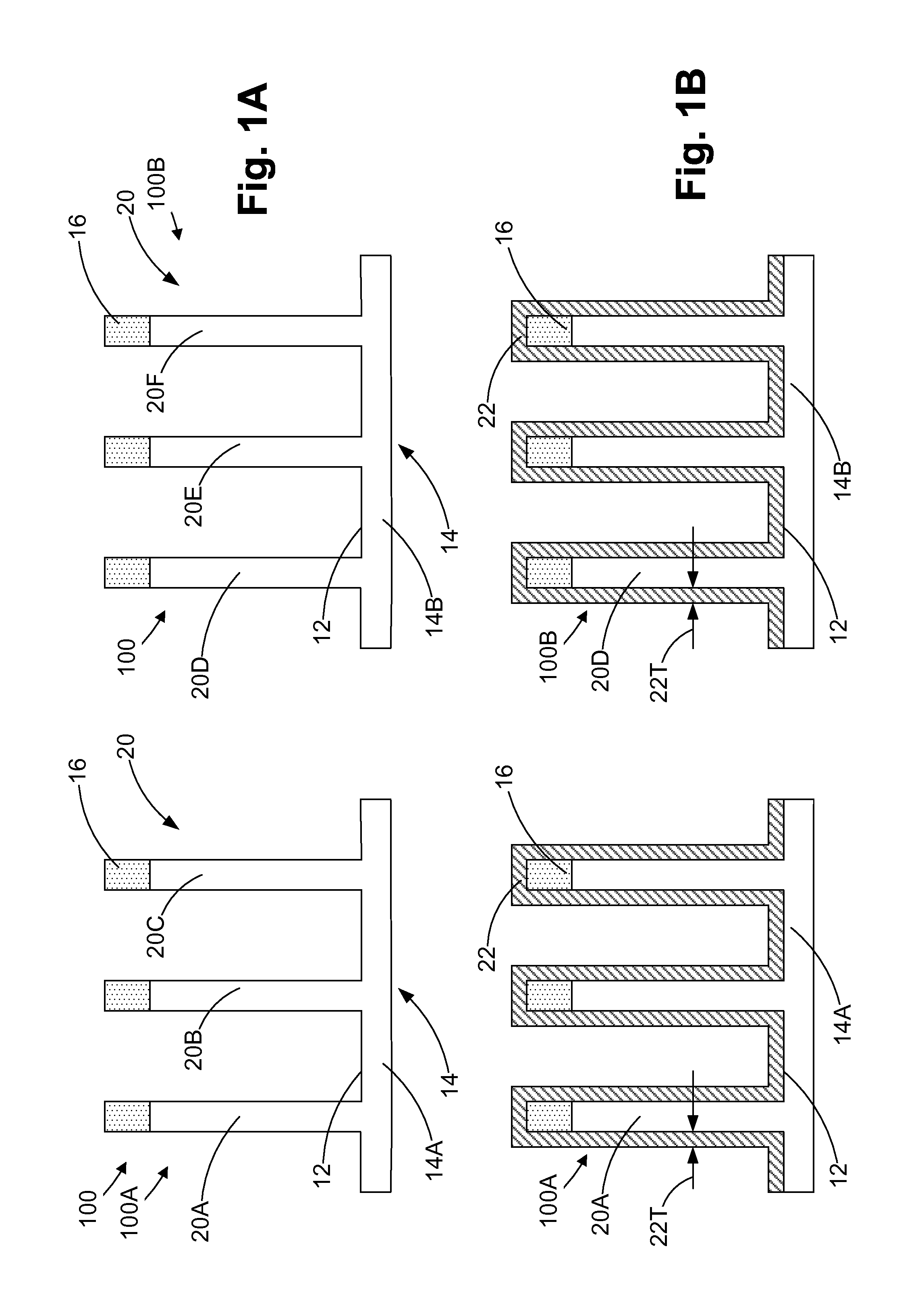

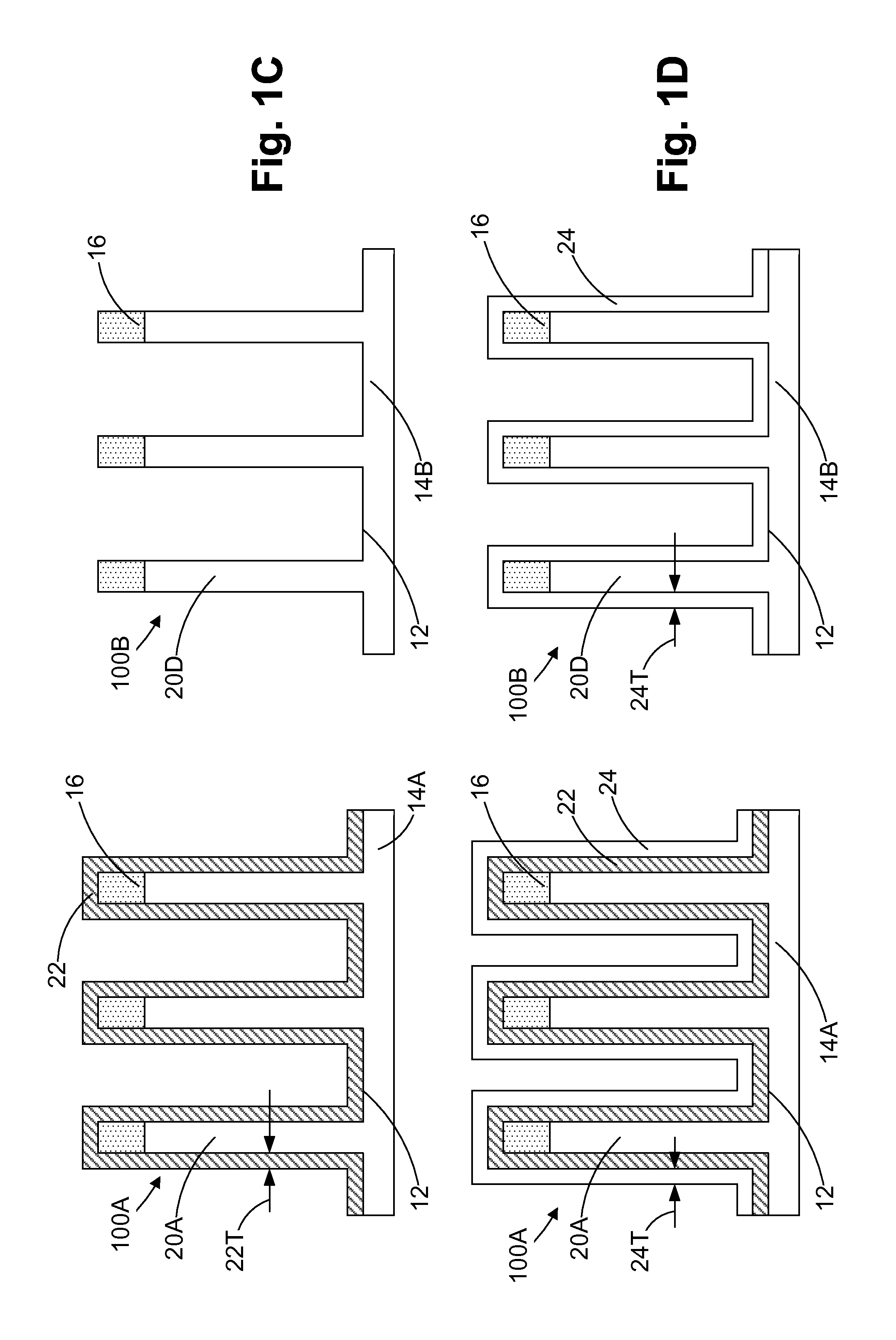

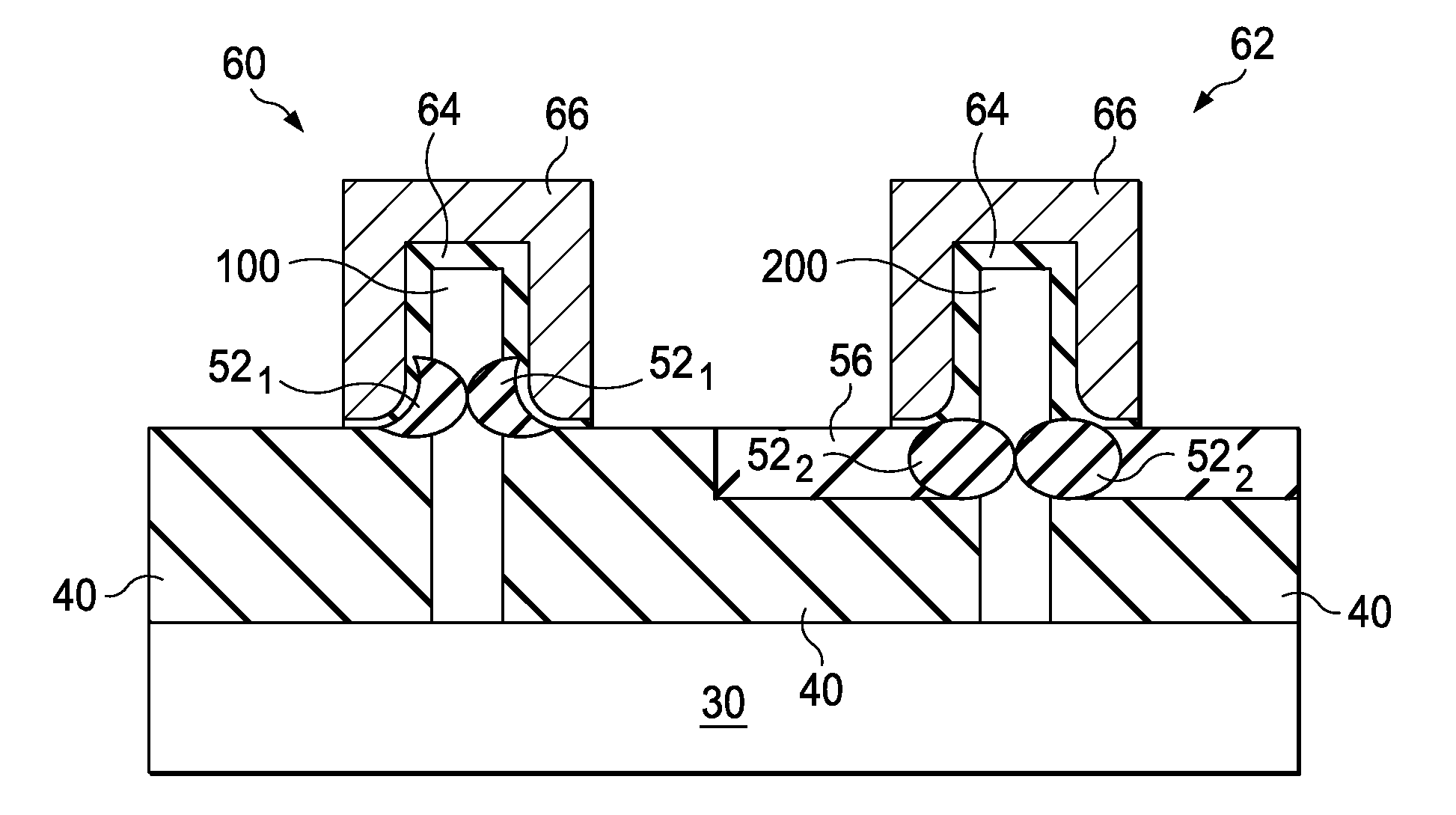

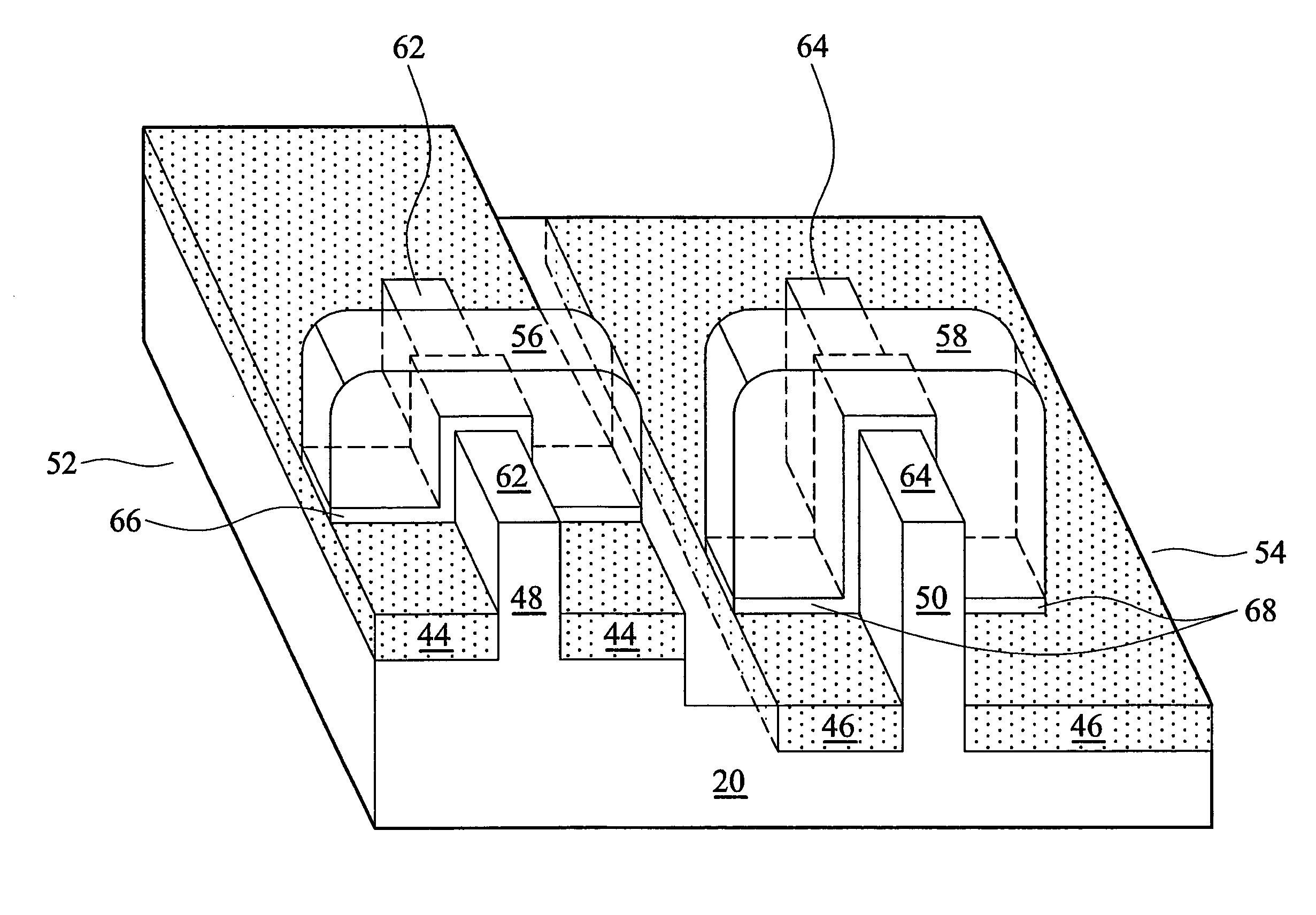

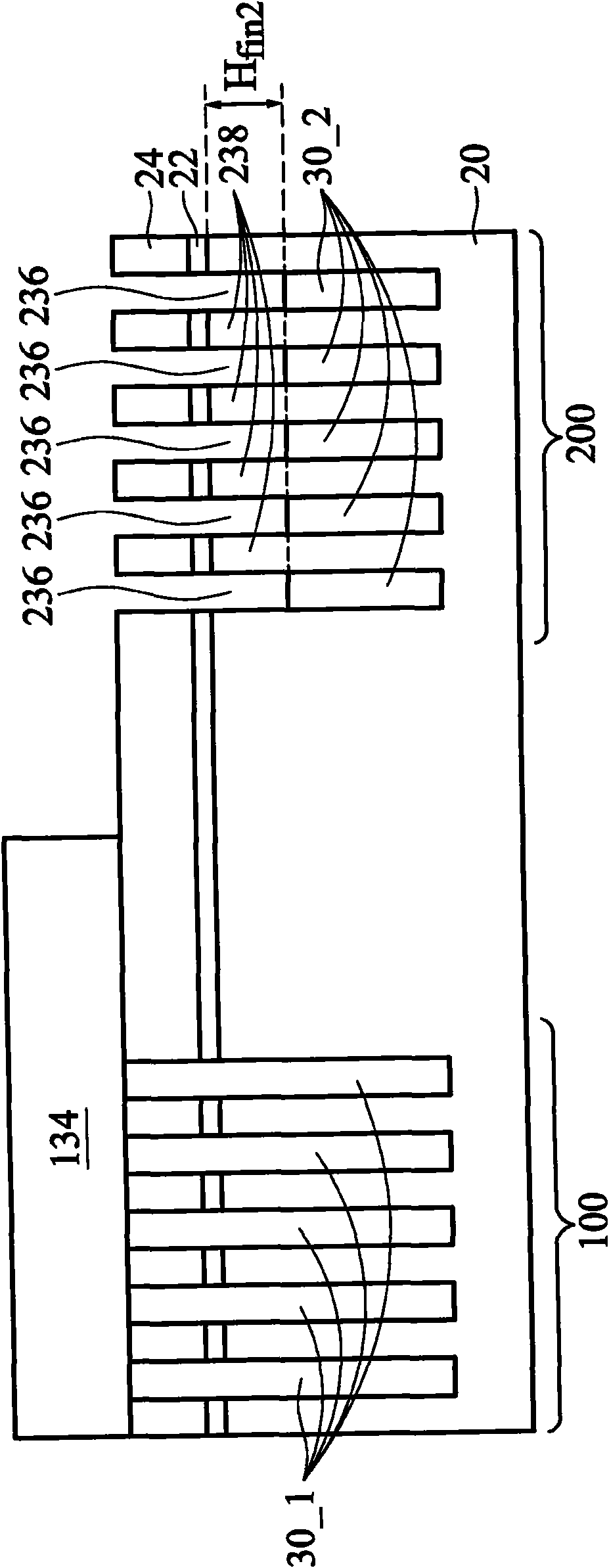

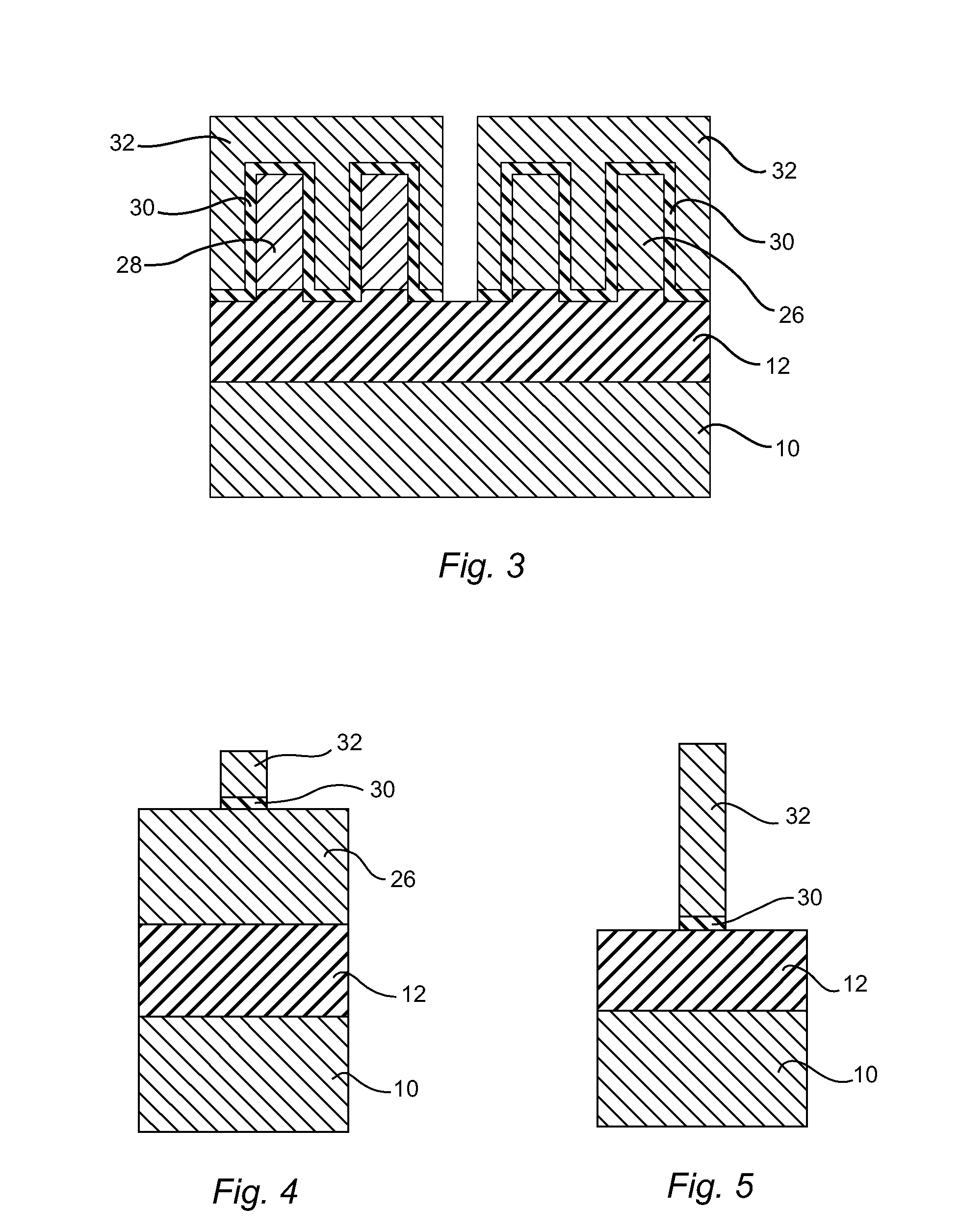

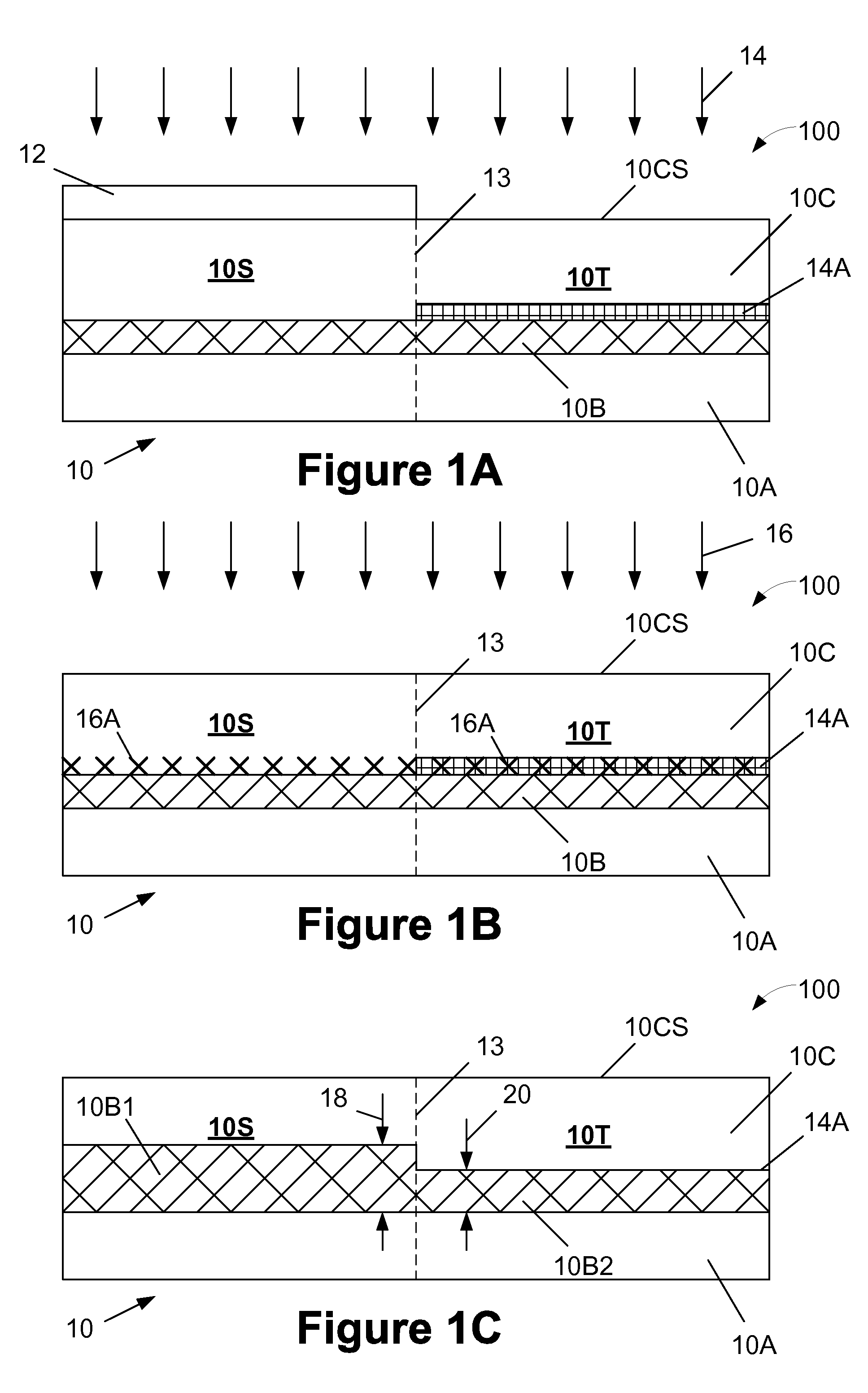

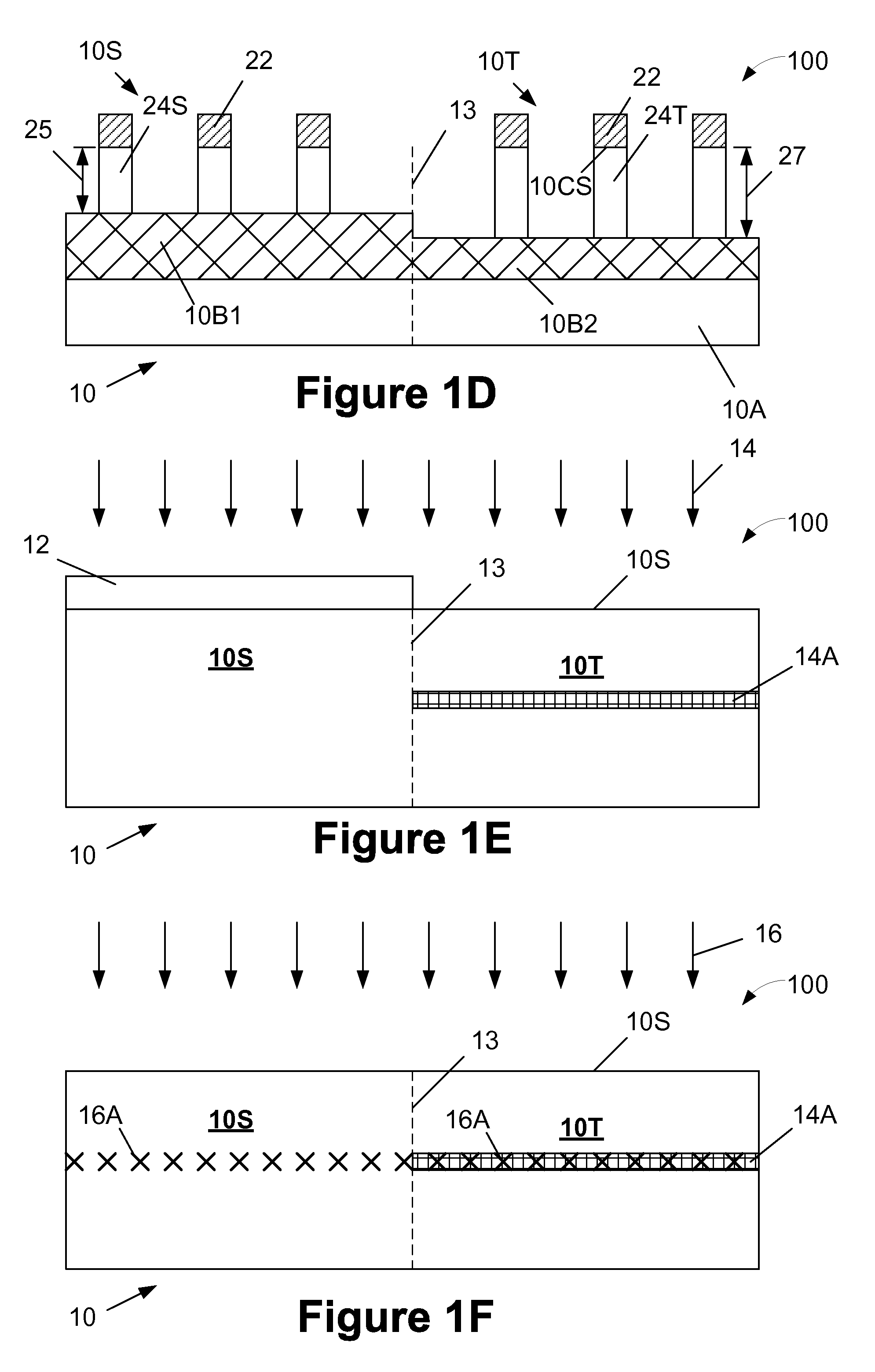

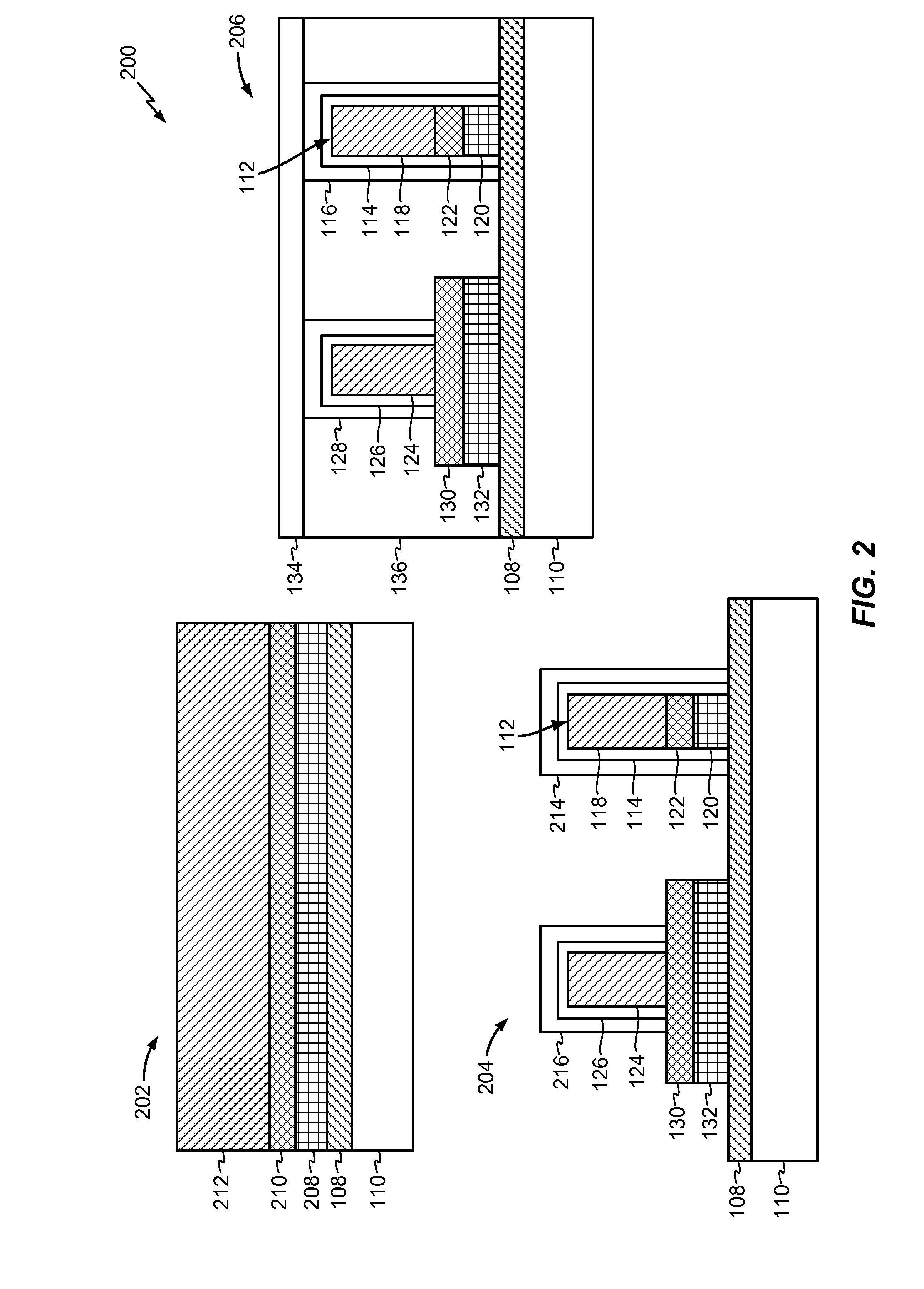

A semiconductor structure includes a semiconductor substrate having a first portion and a second portion. A first Fin field-effect transistor (FinFET) is formed over the first portion of the semiconductor substrate, wherein the first FinFET includes a first fin having a first fin height. A second FinFET is formed over the second portion of the semiconductor substrate, wherein the second FinFET includes a second fin having a second fin height different from the first fin height. A top surface of the first fin is substantially level with a top surface of the second fin. A punch-through stopper is underlying and adjoining the first FinFET, wherein the punch-through stopper isolates the first fin from the first portion of the semiconductor substrate.

Owner:TAIWAN SEMICON MFG CO LTD

Fabrication of FinFETs with multiple fin heights

A semiconductor structure includes a first semiconductor strip extending from a top surface of the semiconductor substrate into the semiconductor substrate, wherein the first semiconductor strip has a first height. A first insulating region is formed in the semiconductor substrate and surrounding a bottom portion of the first semiconductor strip, wherein the first insulating region has a first top surface lower than a top surface of the first semiconductor strip. A second semiconductor strip extends from a top surface of the semiconductor substrate into the semiconductor substrate, wherein the second semiconductor strip has a second height greater than the first height. A second insulating region is formed in the semiconductor substrate and surrounding a bottom portion of the second semiconductor strip, wherein the second insulating region has a second top surface lower than the first top surface, and wherein the first and the second insulating regions have substantially same thicknesses.

Owner:TAIWAN SEMICON MFG CO LTD

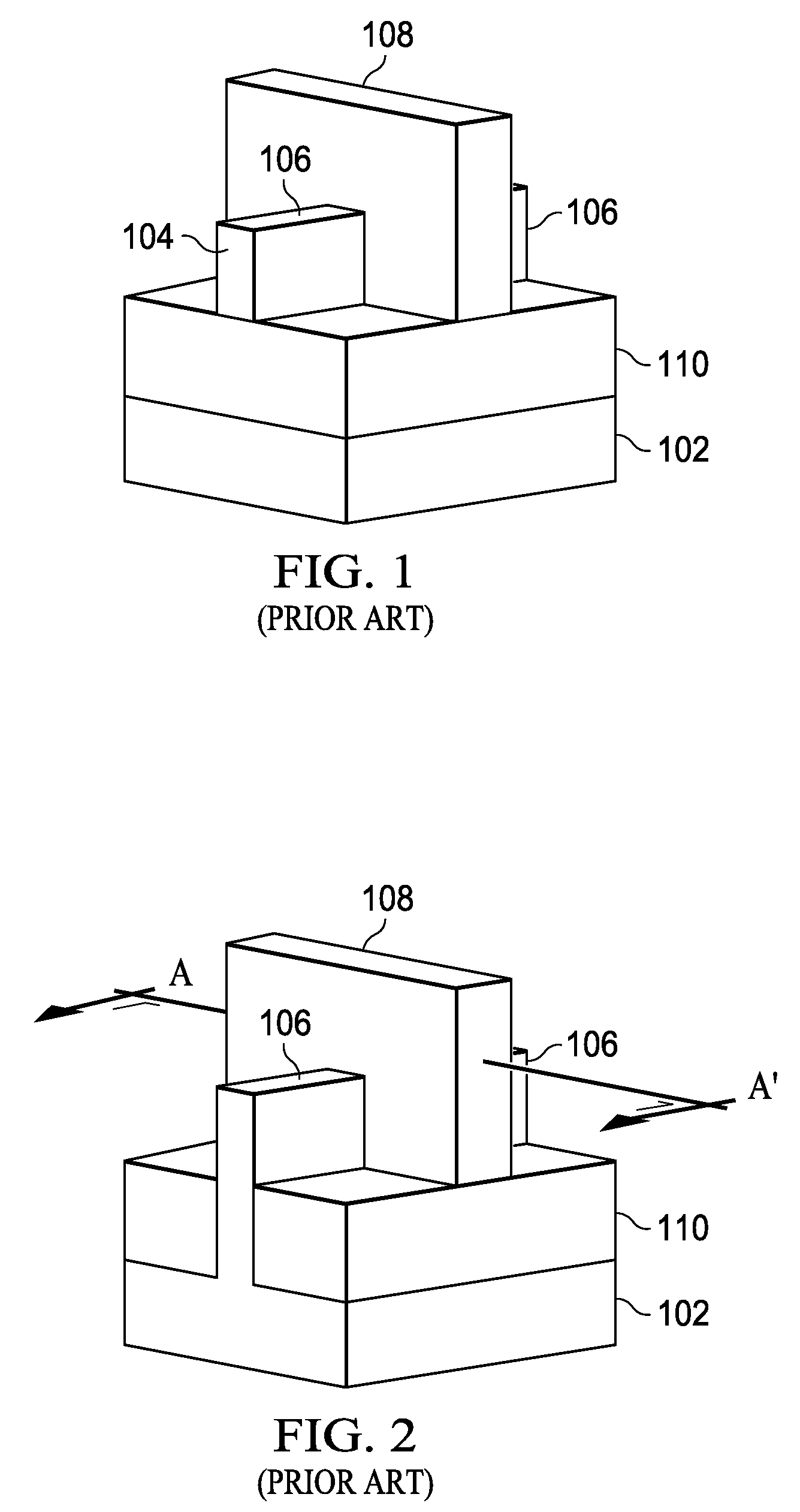

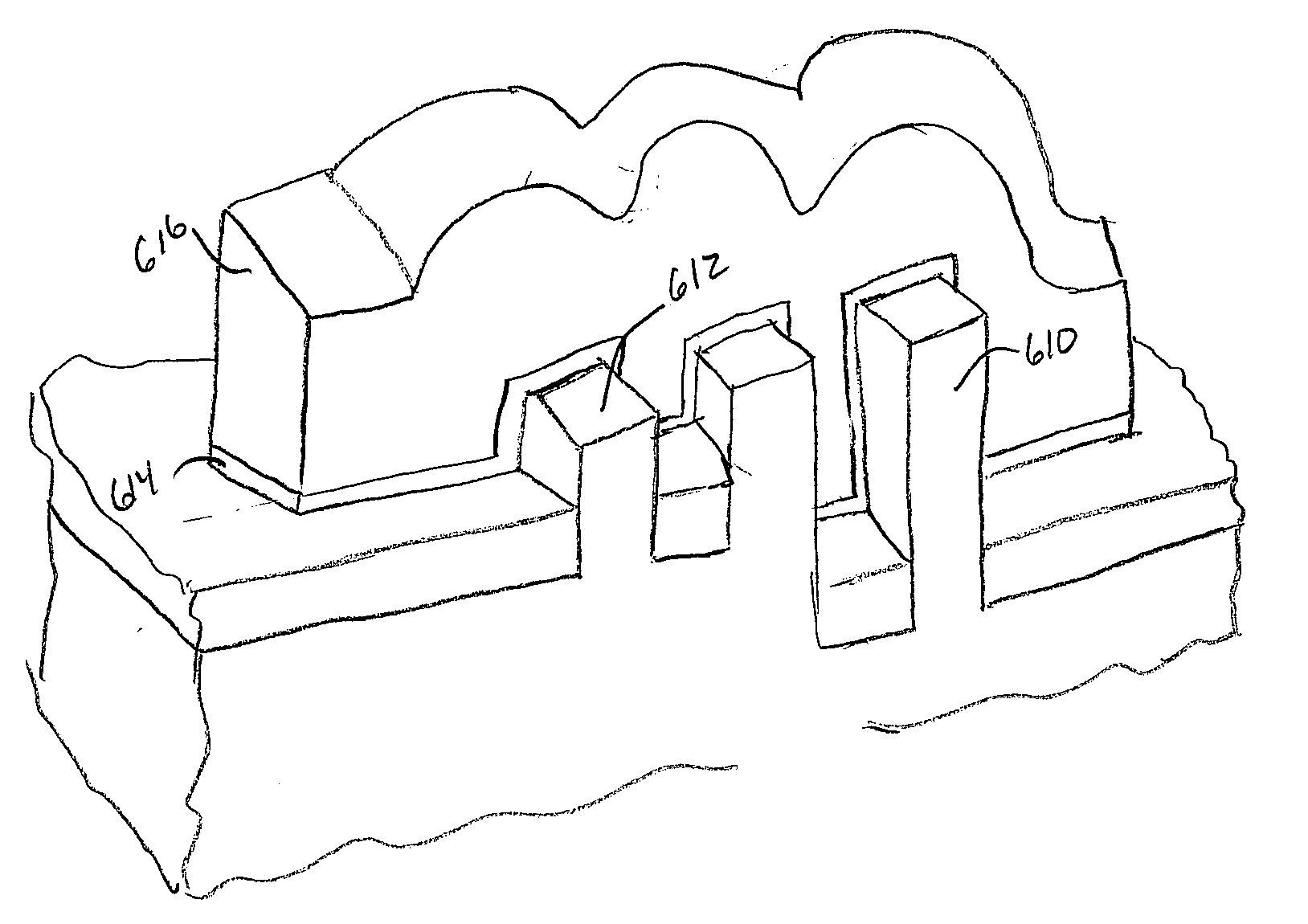

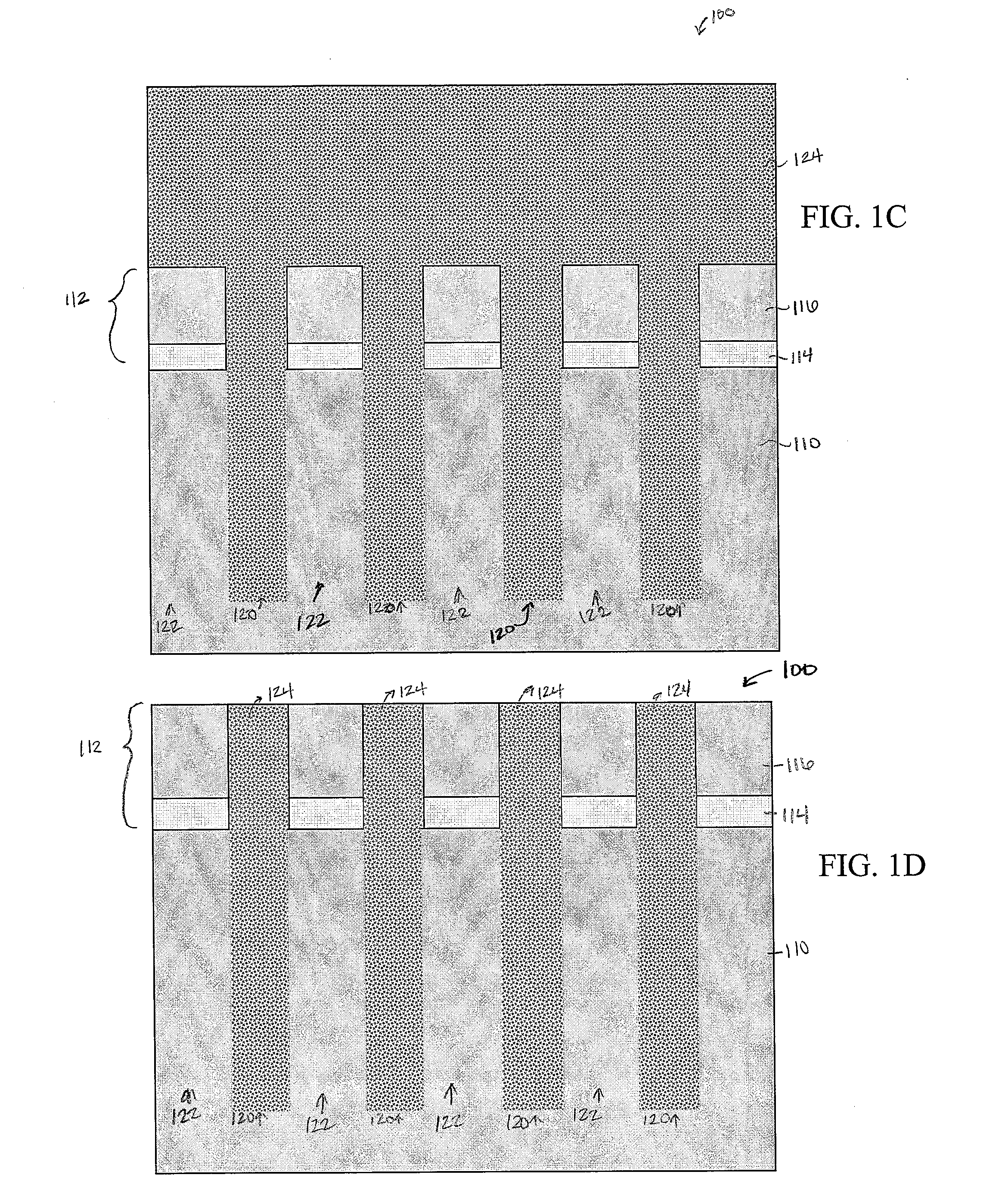

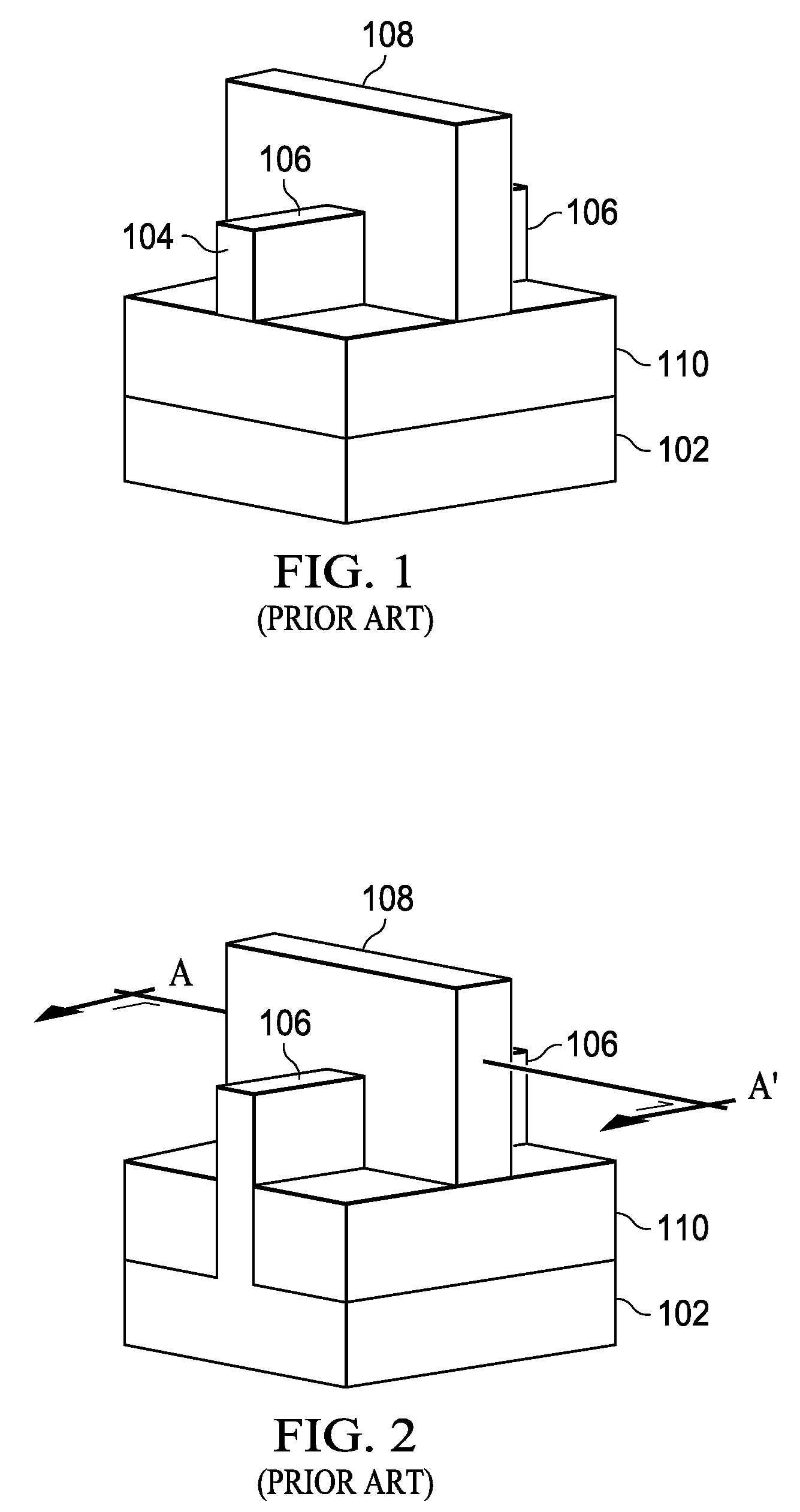

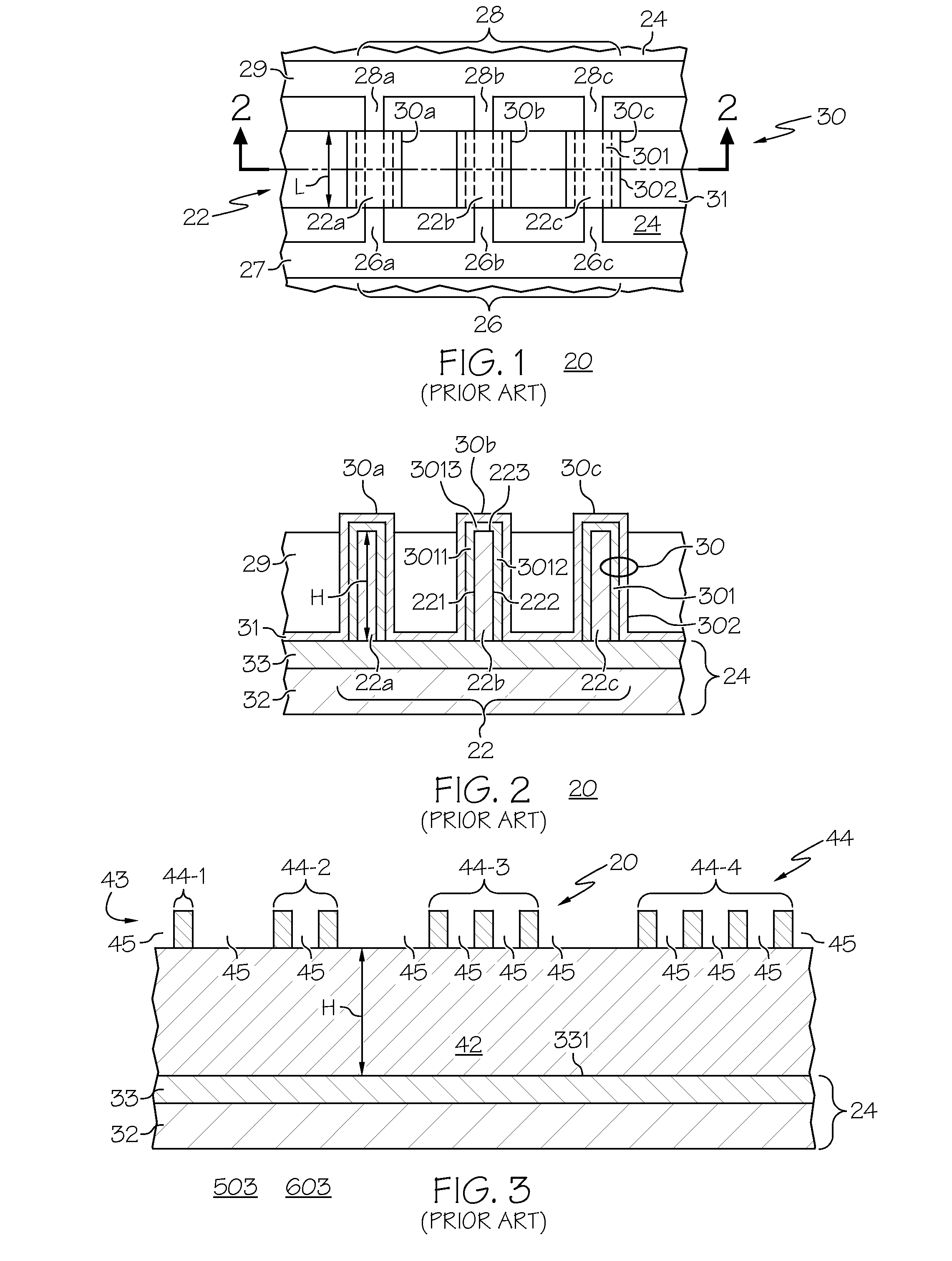

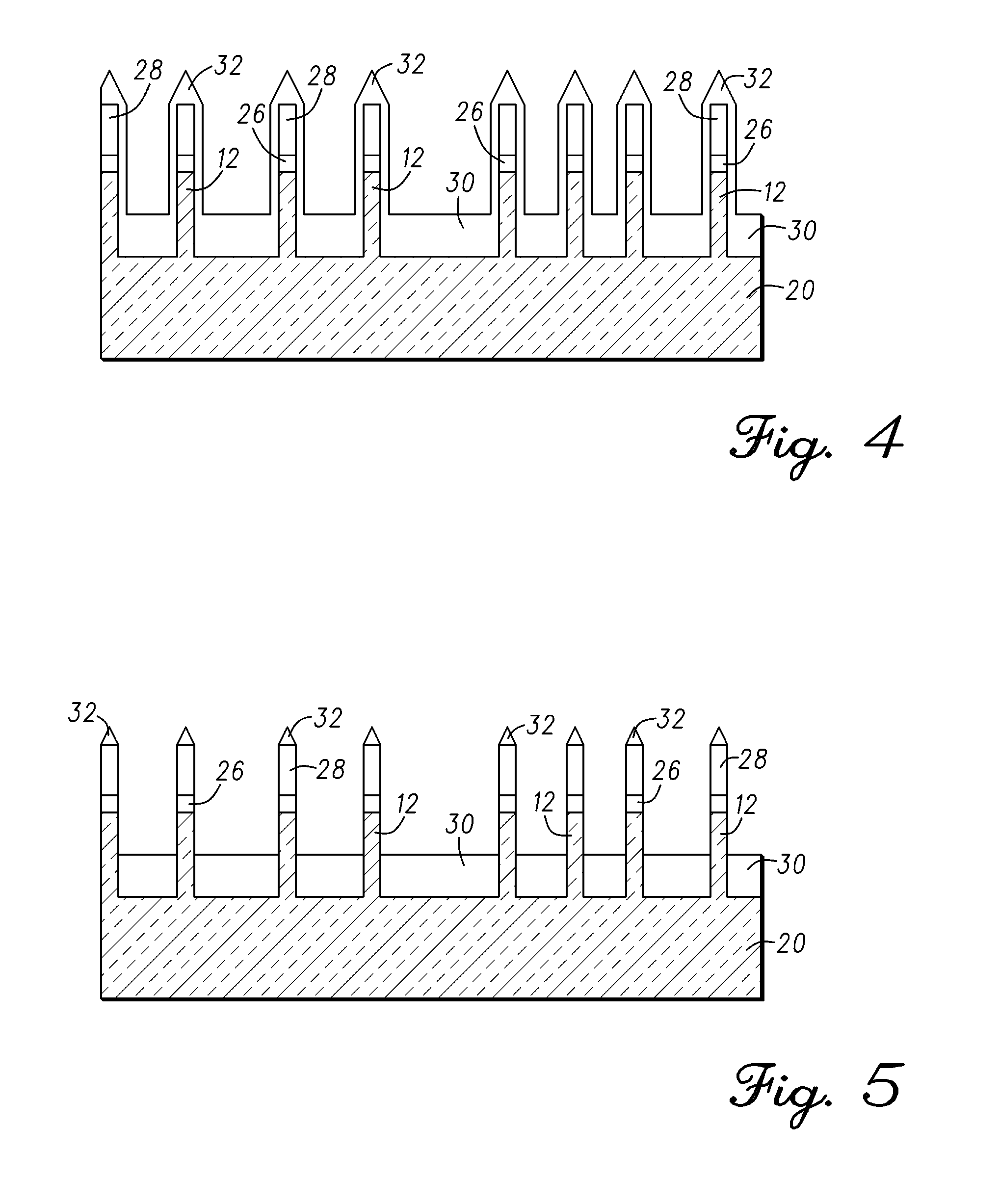

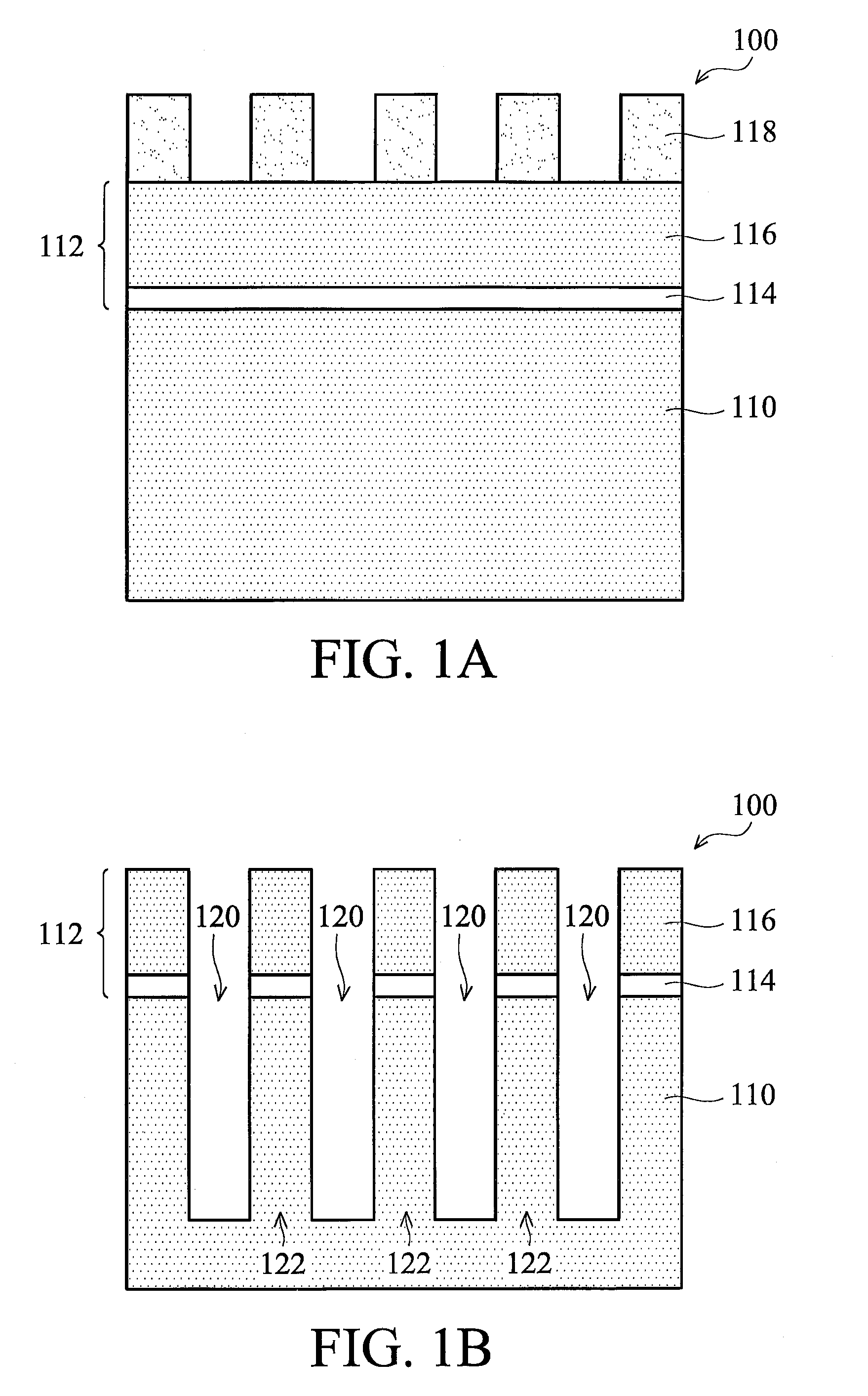

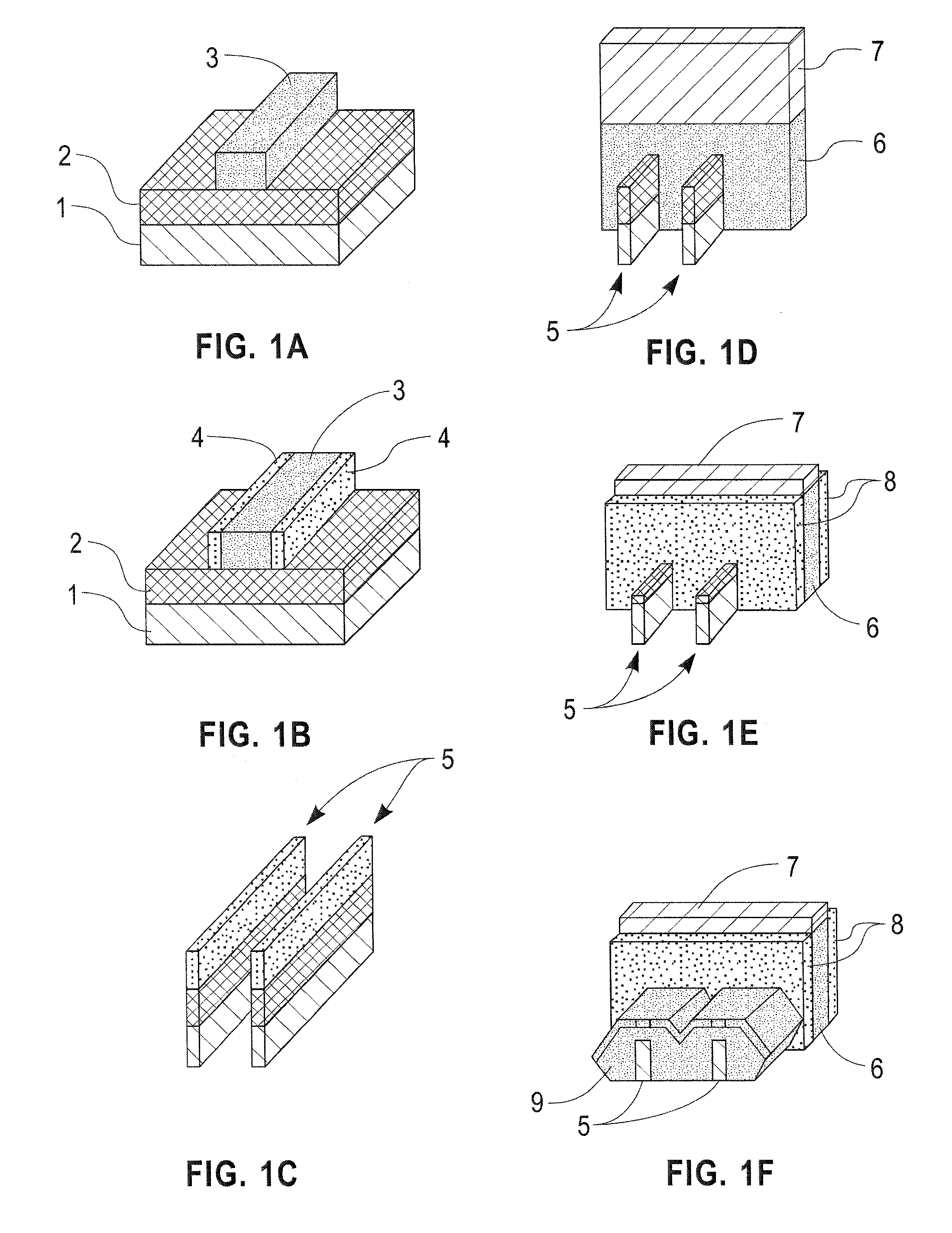

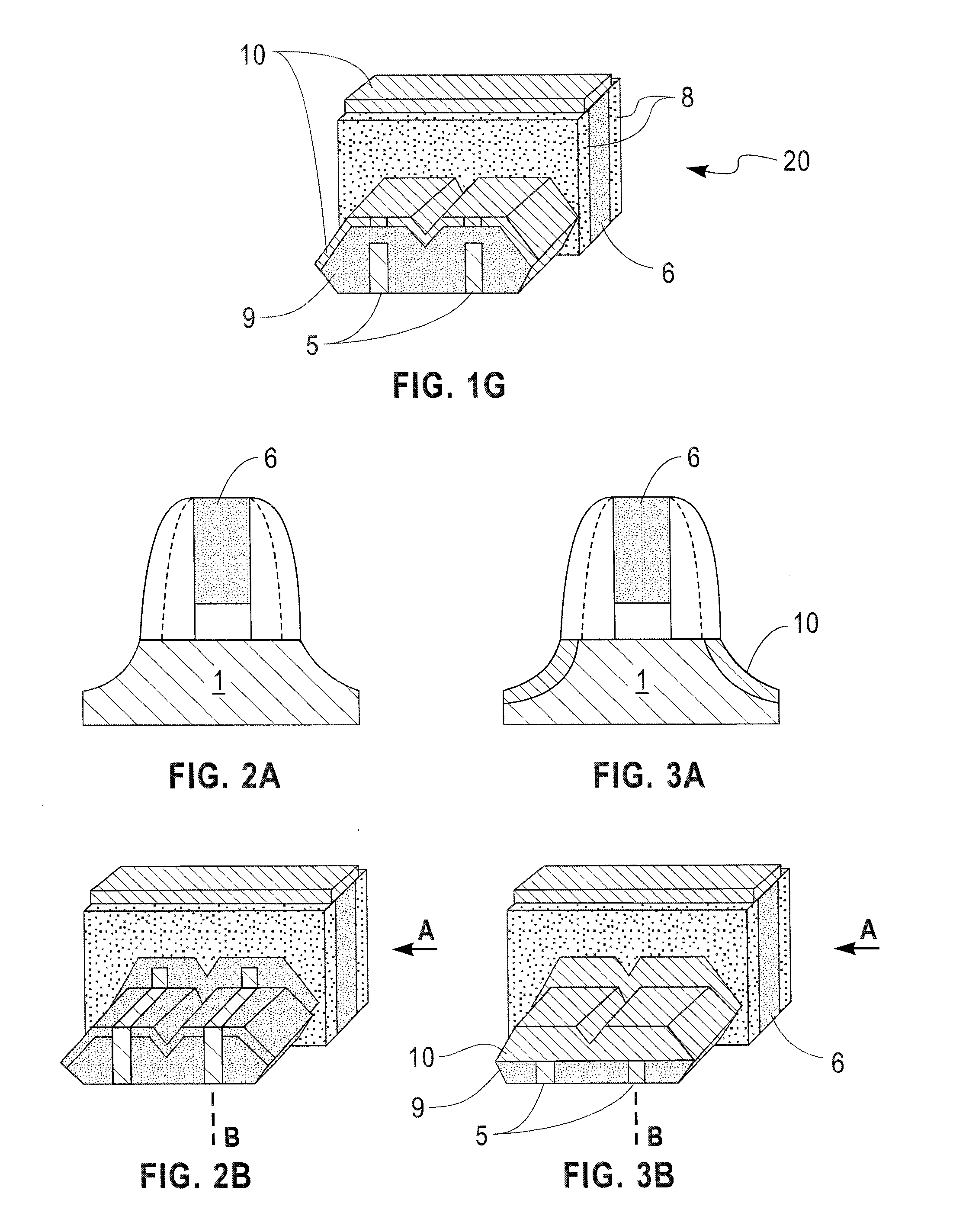

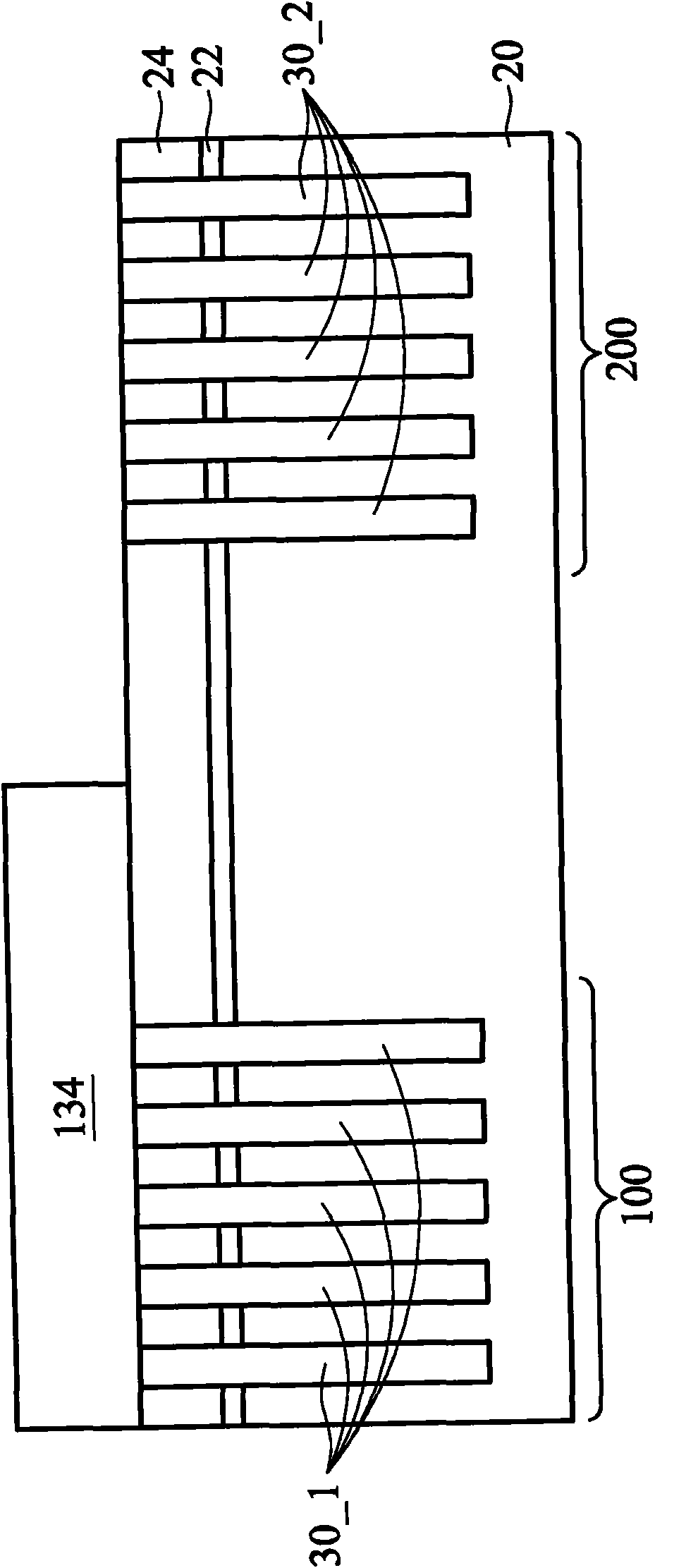

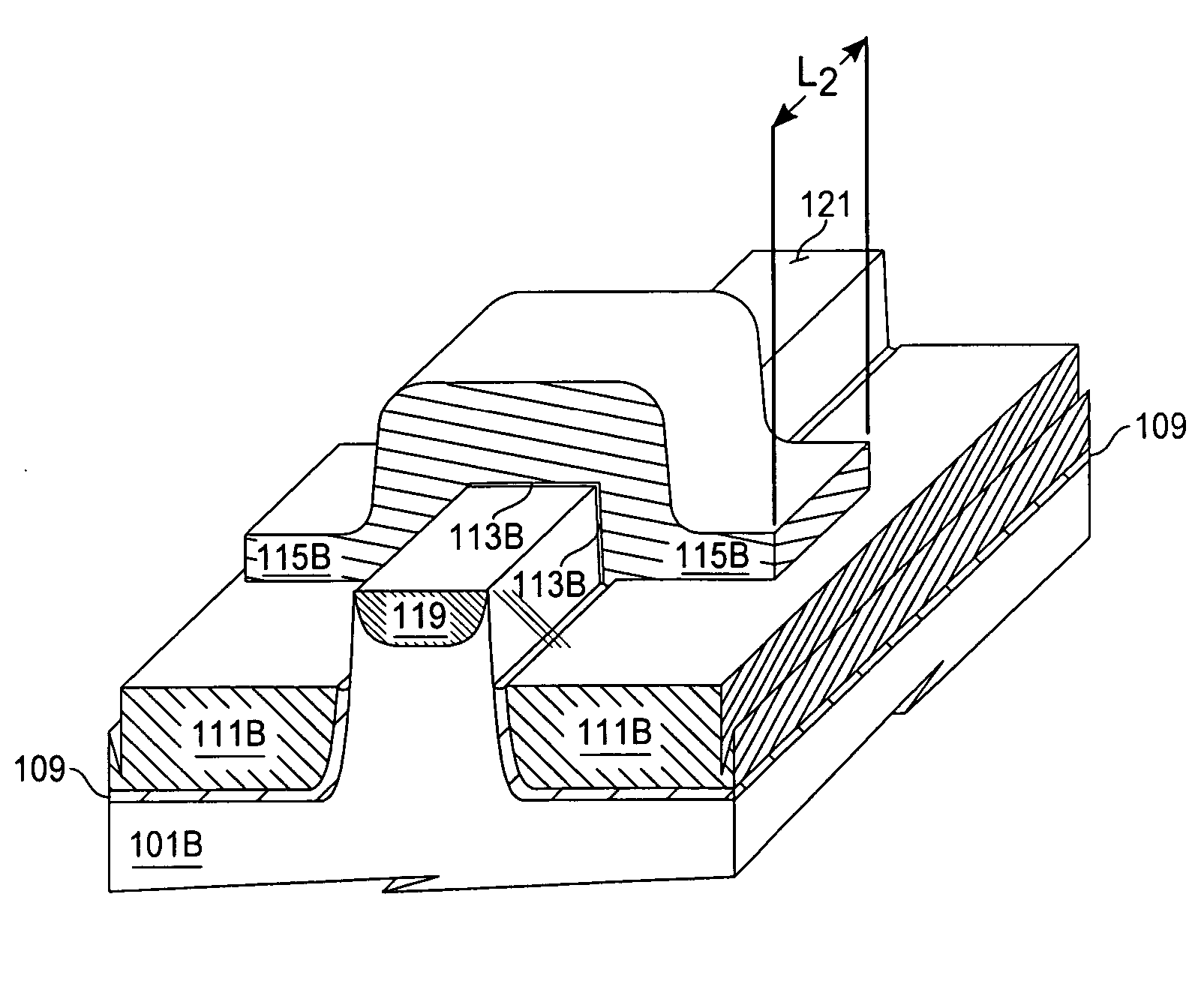

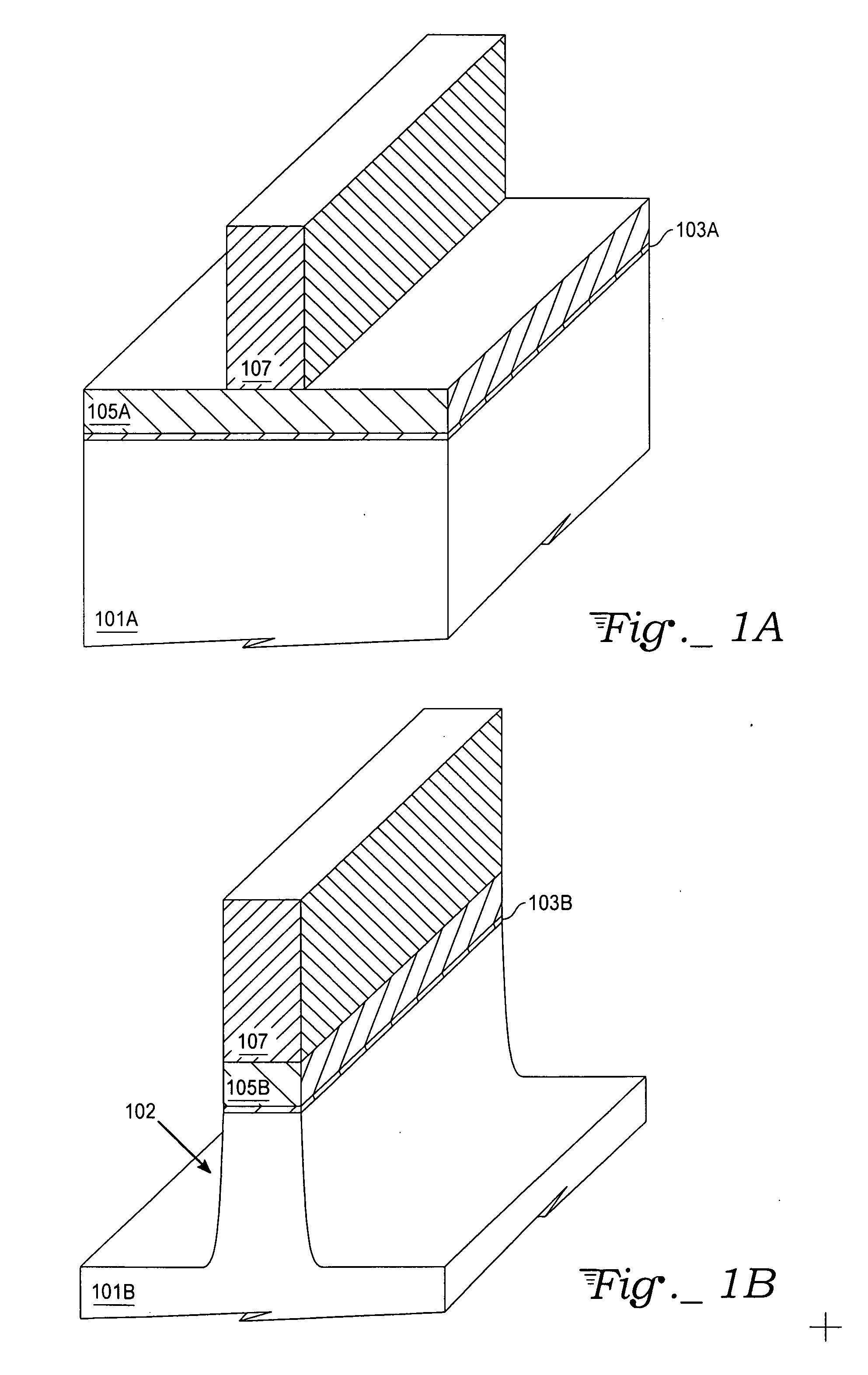

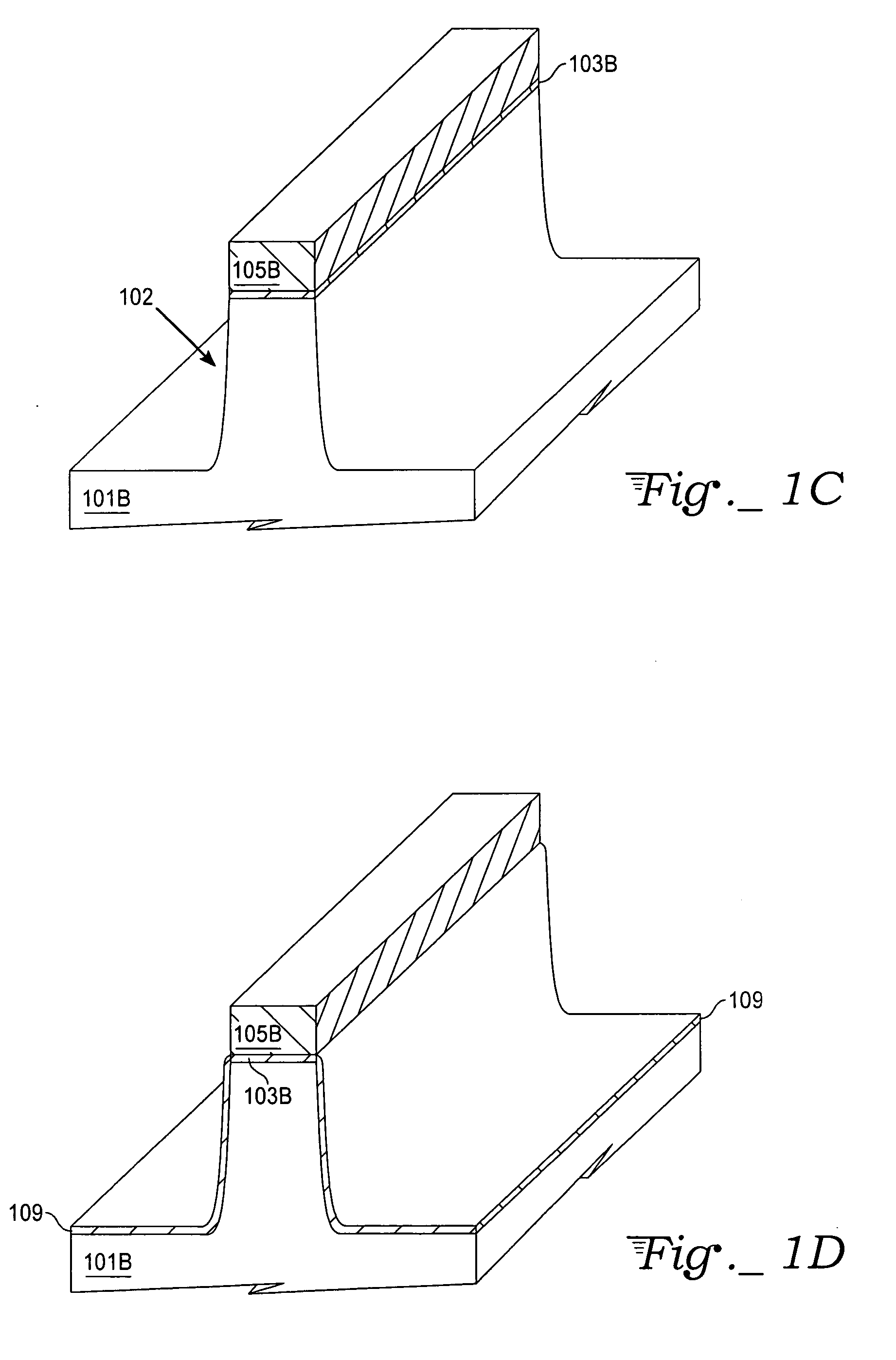

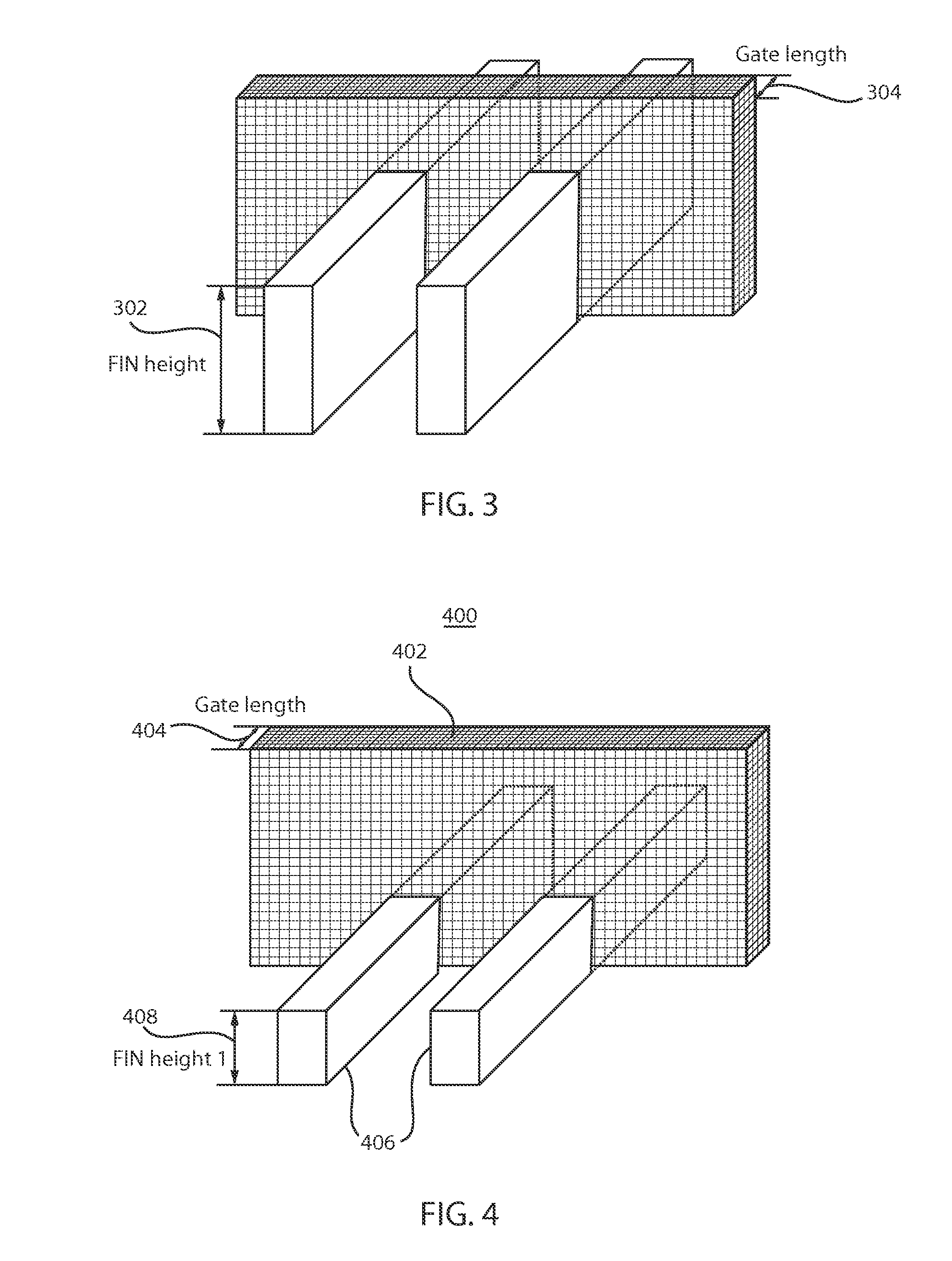

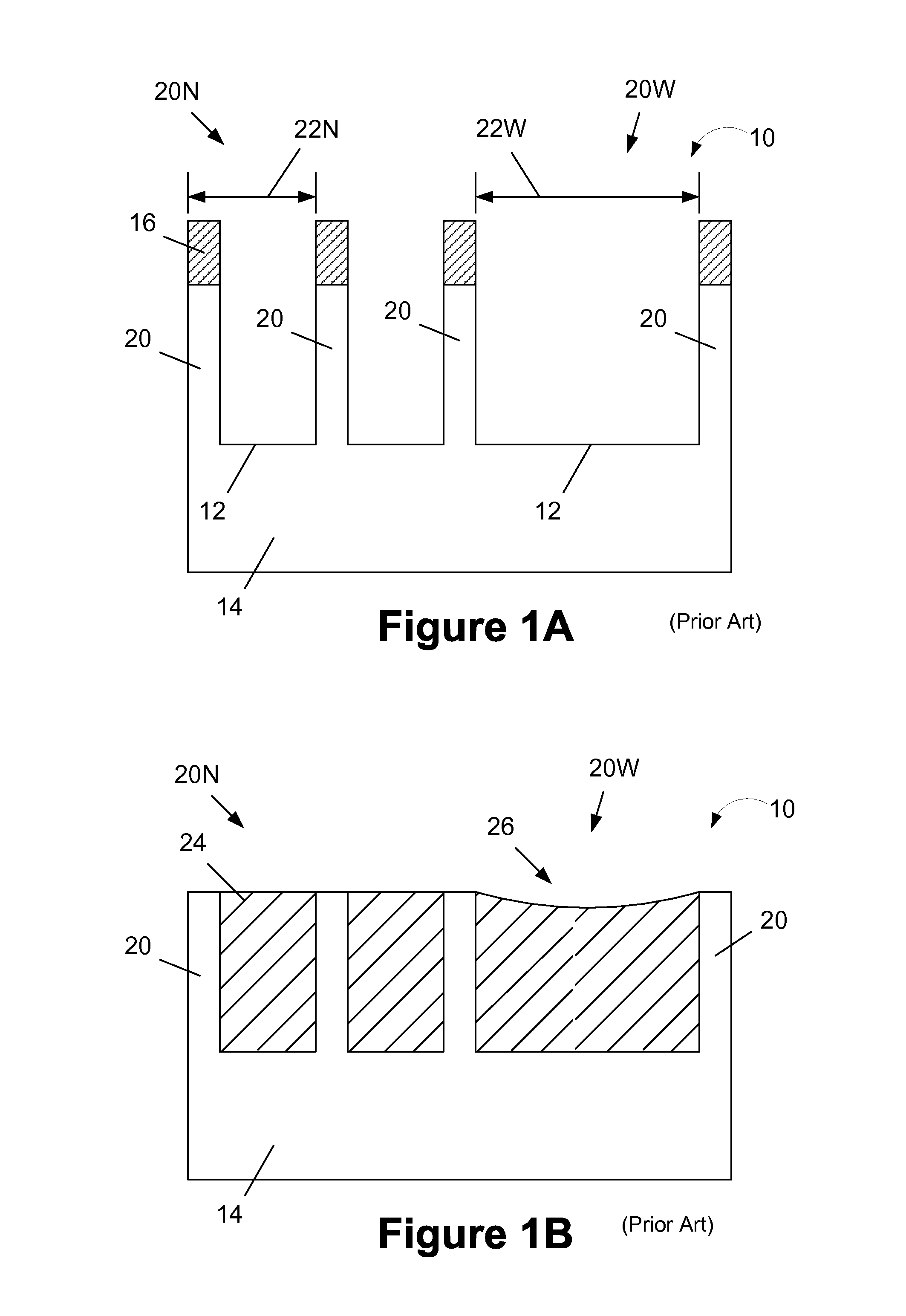

Semiconductor Device Having Multiple Fin Heights

A semiconductor device having multiple fin heights is provided. Multiple fin heights are provided by using multiple masks to recess a dielectric layer within a trench formed in a substrate. In another embodiment, an implant mold or e-beam lithography are utilized to form a pattern of trenches in a photoresist material. Subsequent etching steps form corresponding trenches in the underlying substrate. In yet another embodiment, multiple masking layers are used to etch trenches of different heights separately. A dielectric region may be formed along the bottom of the trenches to isolate the fins by performing an ion implant and a subsequent anneal.

Owner:TAIWAN SEMICON MFG CO LTD

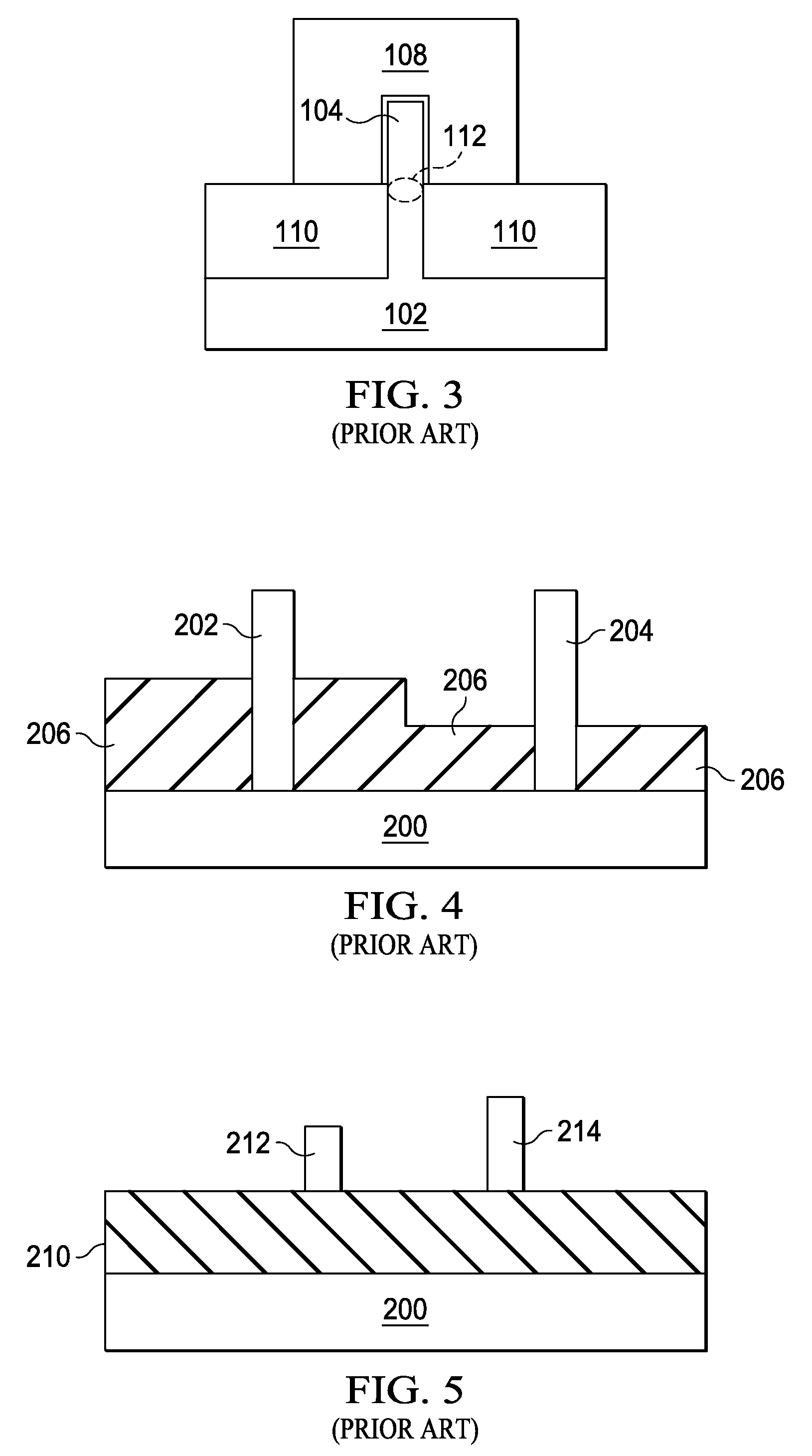

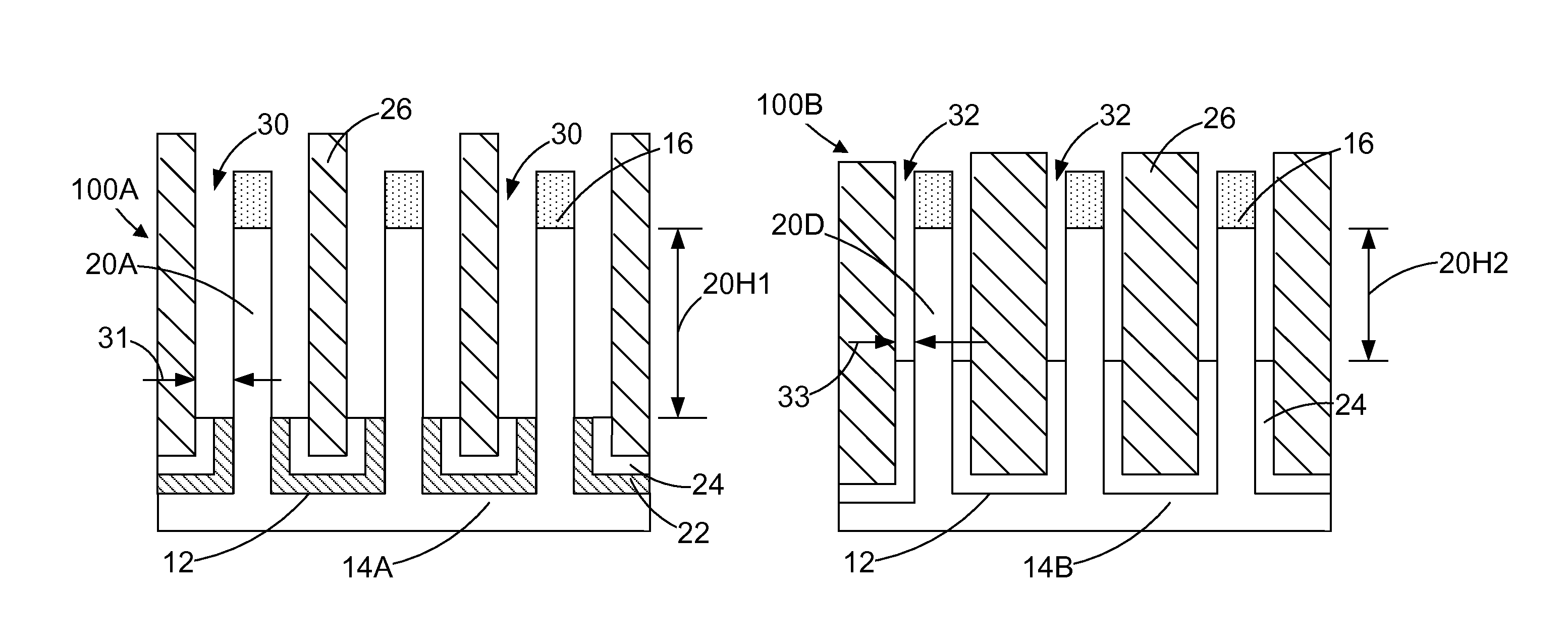

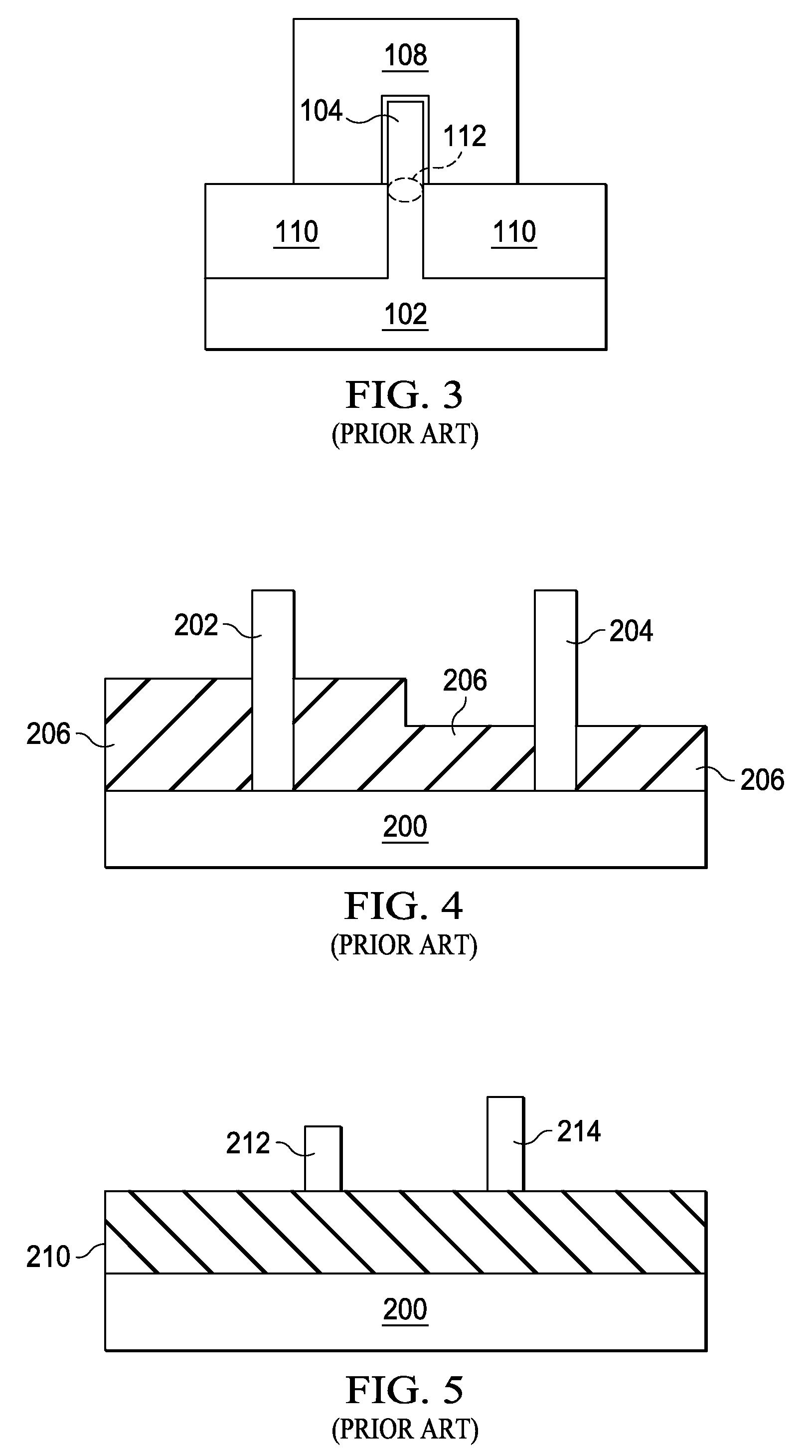

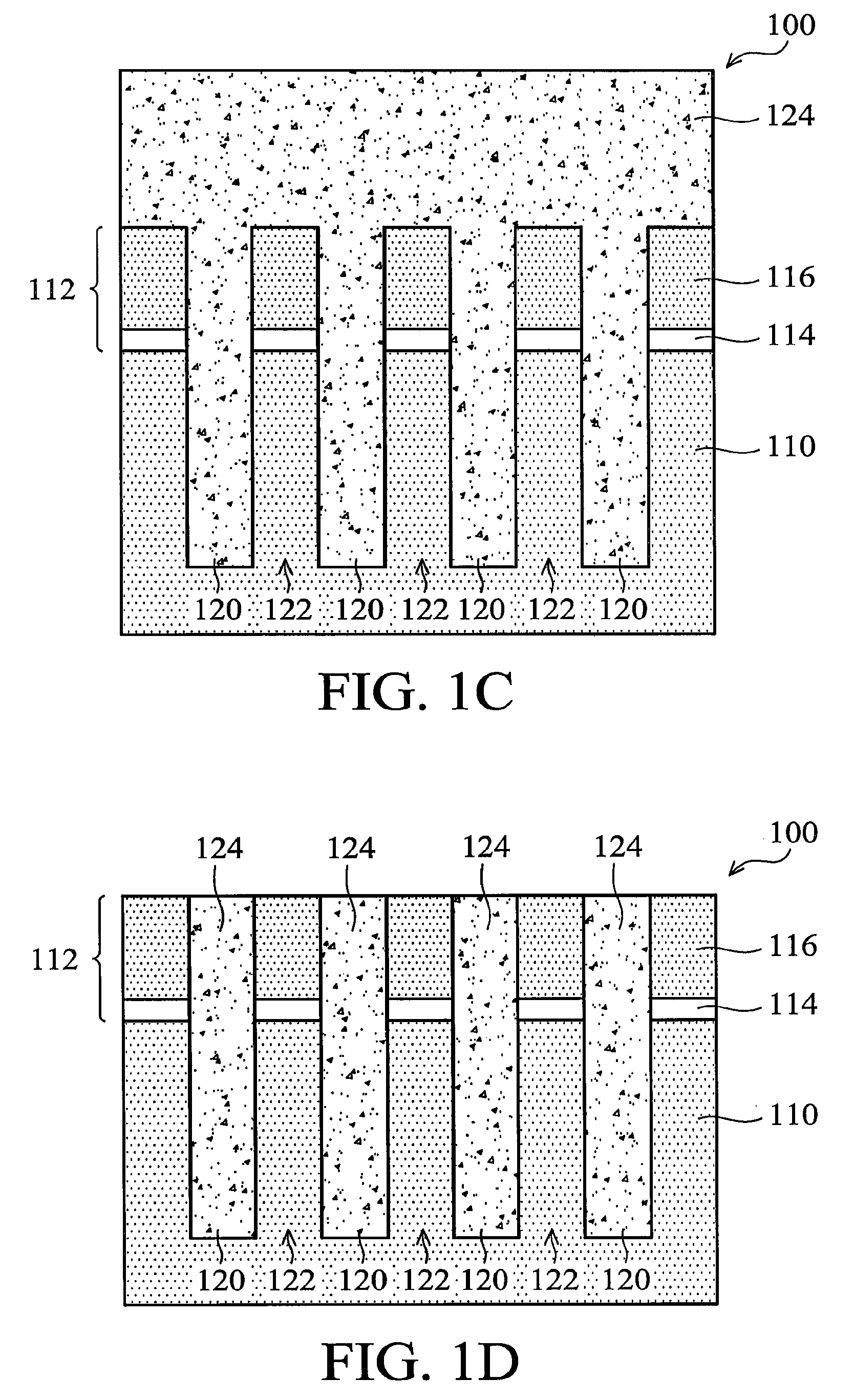

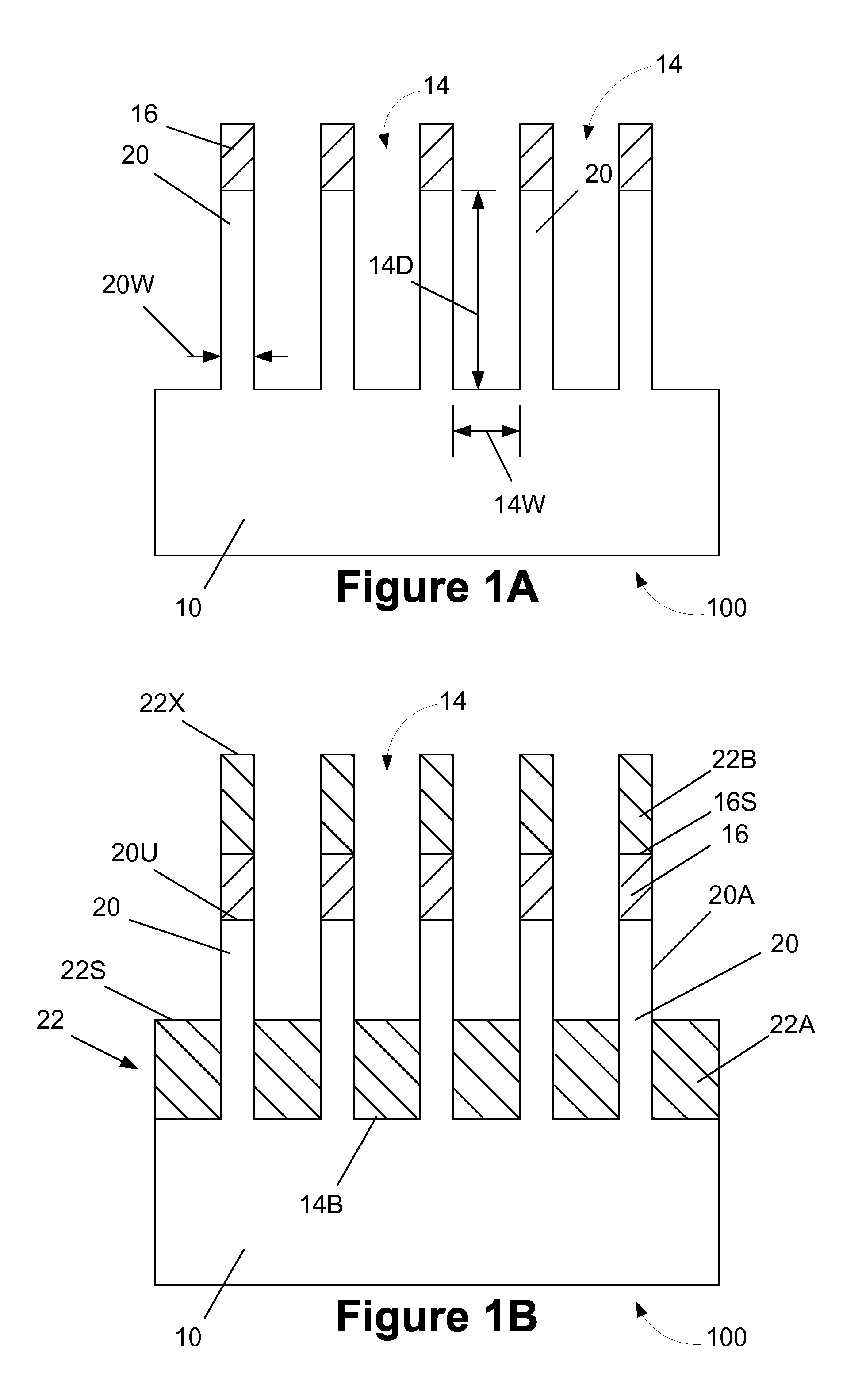

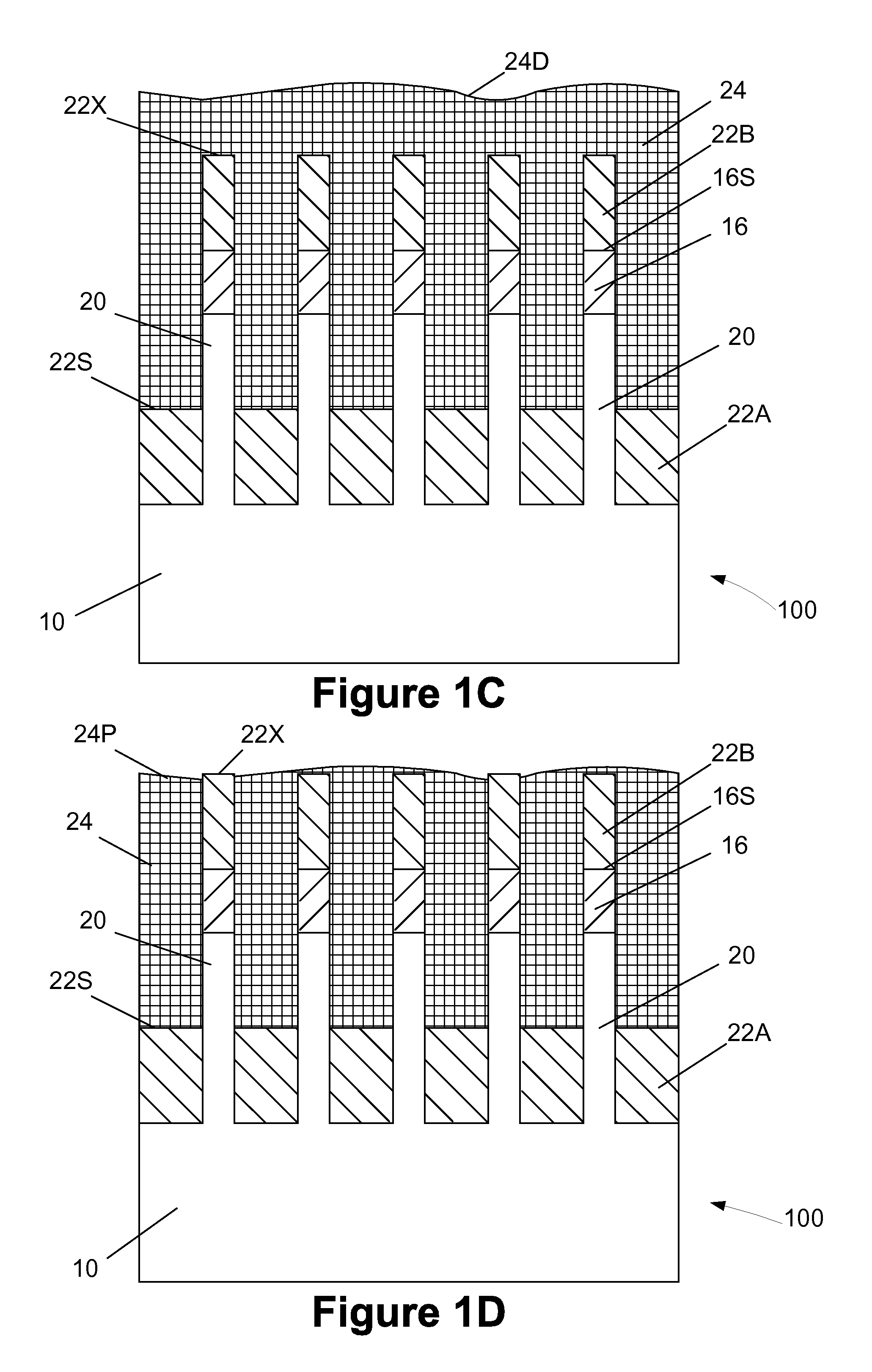

Methods of forming different finfet devices having different fin heights and an integrated circuit product containing such devices

One illustrative method disclosed herein includes forming a plurality of trenches in a plurality of active regions of a substrate that defines at least a first plurality of fins and a second plurality of fins for first and second FinFET devices, respectively, forming liner materials adjacent to the first and second plurality of fins, wherein the liner materials adjacent the first fins and the second fins have a different thickness. The method also includes removing insulating material to expose portions of the liner materials, performing an etching process to remove portions of the liner materials so as to expose at least one fin in the first plurality of fins to a first height and at least one of the second plurality of fins to a second height that is different from the first height.

Owner:GLOBALFOUNDRIES US INC

Dielectric punch-through stoppers for forming FinFETs having dual fin heights

ActiveUS8263462B2Improved accuracy in formationTotal current dropTransistorSolid-state devicesDielectricSemiconductor structure

A semiconductor structure includes a semiconductor substrate having a first portion and a second portion. A first Fin field-effect transistor (FinFET) is formed over the first portion of the semiconductor substrate, wherein the first FinFET includes a first fin having a first fin height. A second FinFET is formed over the second portion of the semiconductor substrate, wherein the second FinFET includes a second fin having a second fin height different from the first fin height. A top surface of the first fin is substantially level with a top surface of the second fin. A punch-through stopper is underlying and adjoining the first FinFET, wherein the punch-through stopper isolates the first fin from the first portion of the semiconductor substrate.

Owner:TAIWAN SEMICON MFG CO LTD

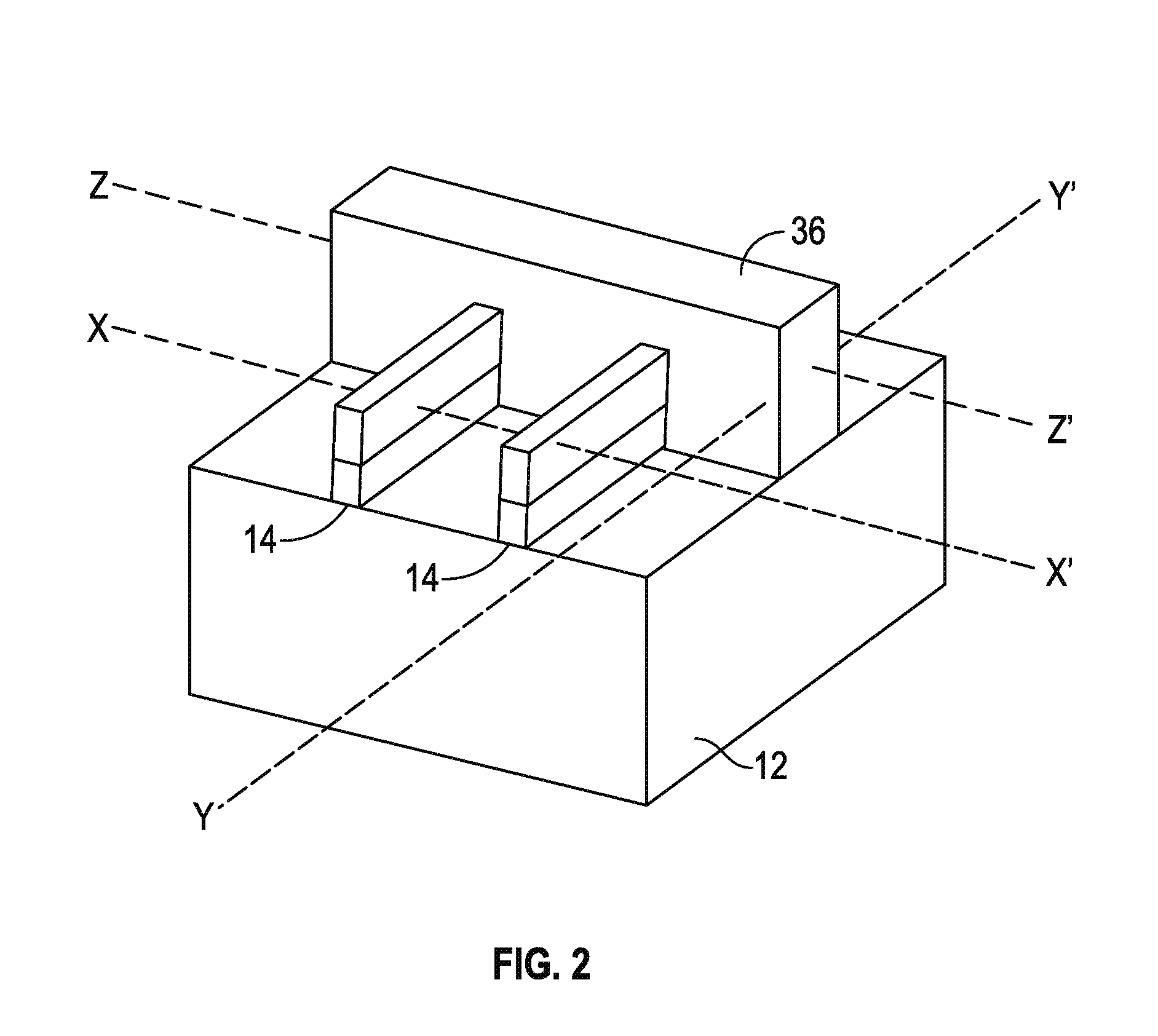

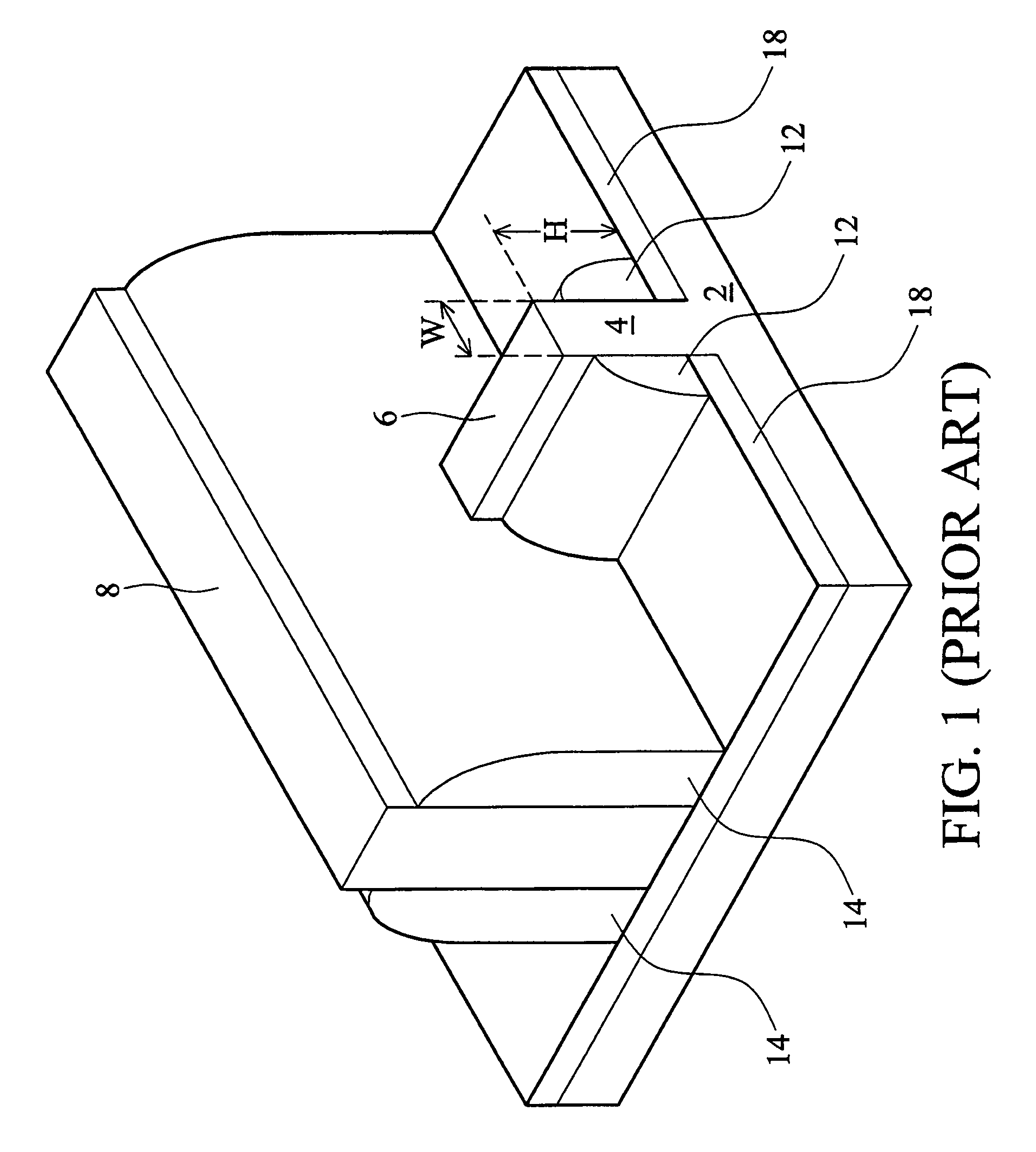

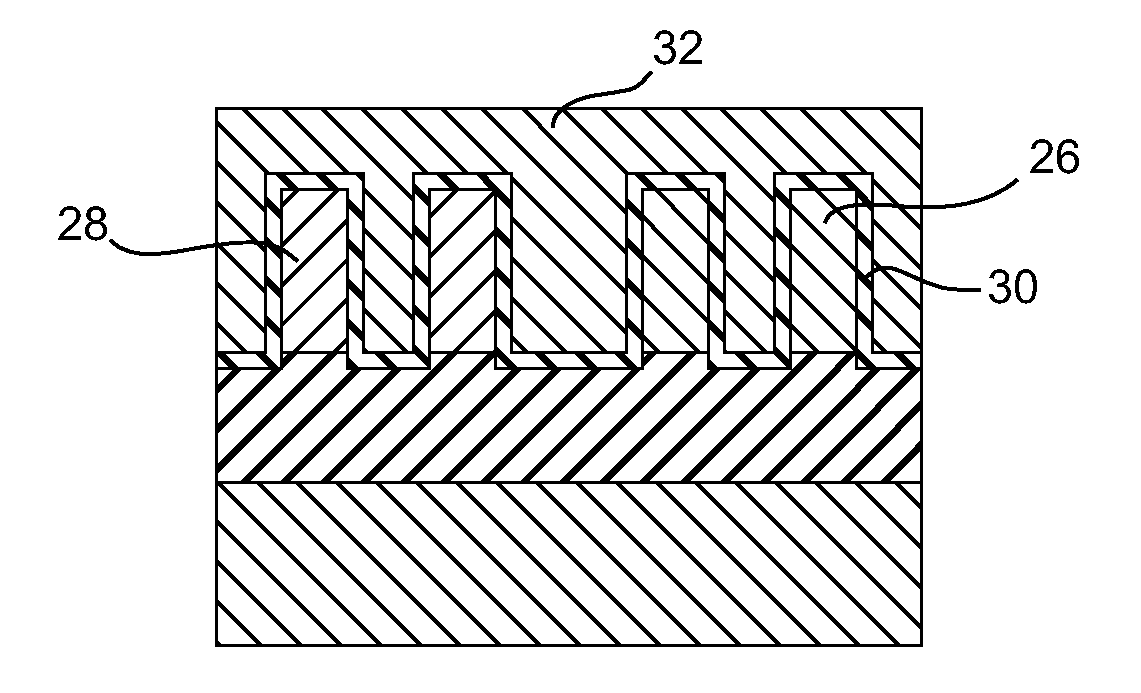

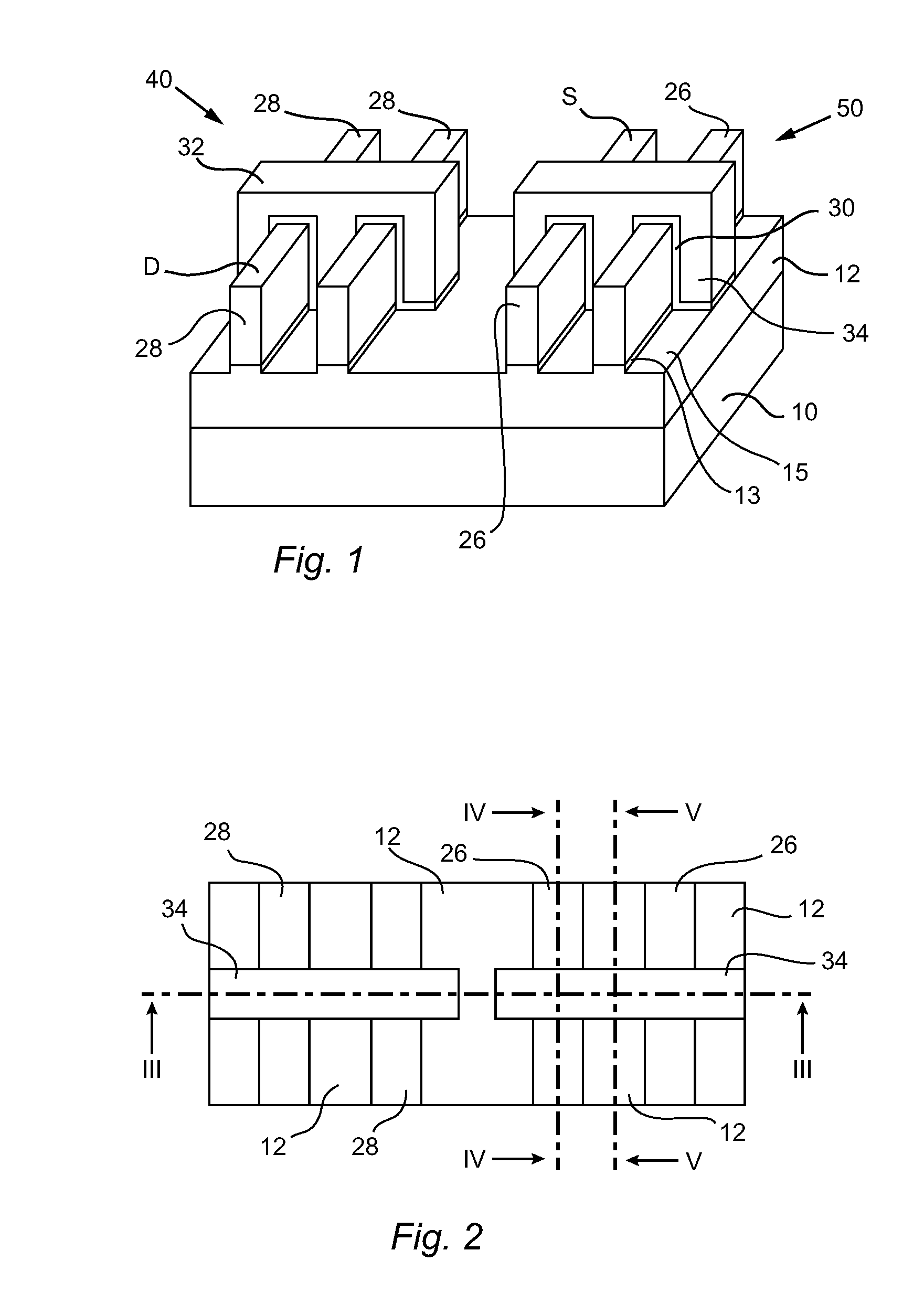

Fin-fet device and method and integrated circuits using such

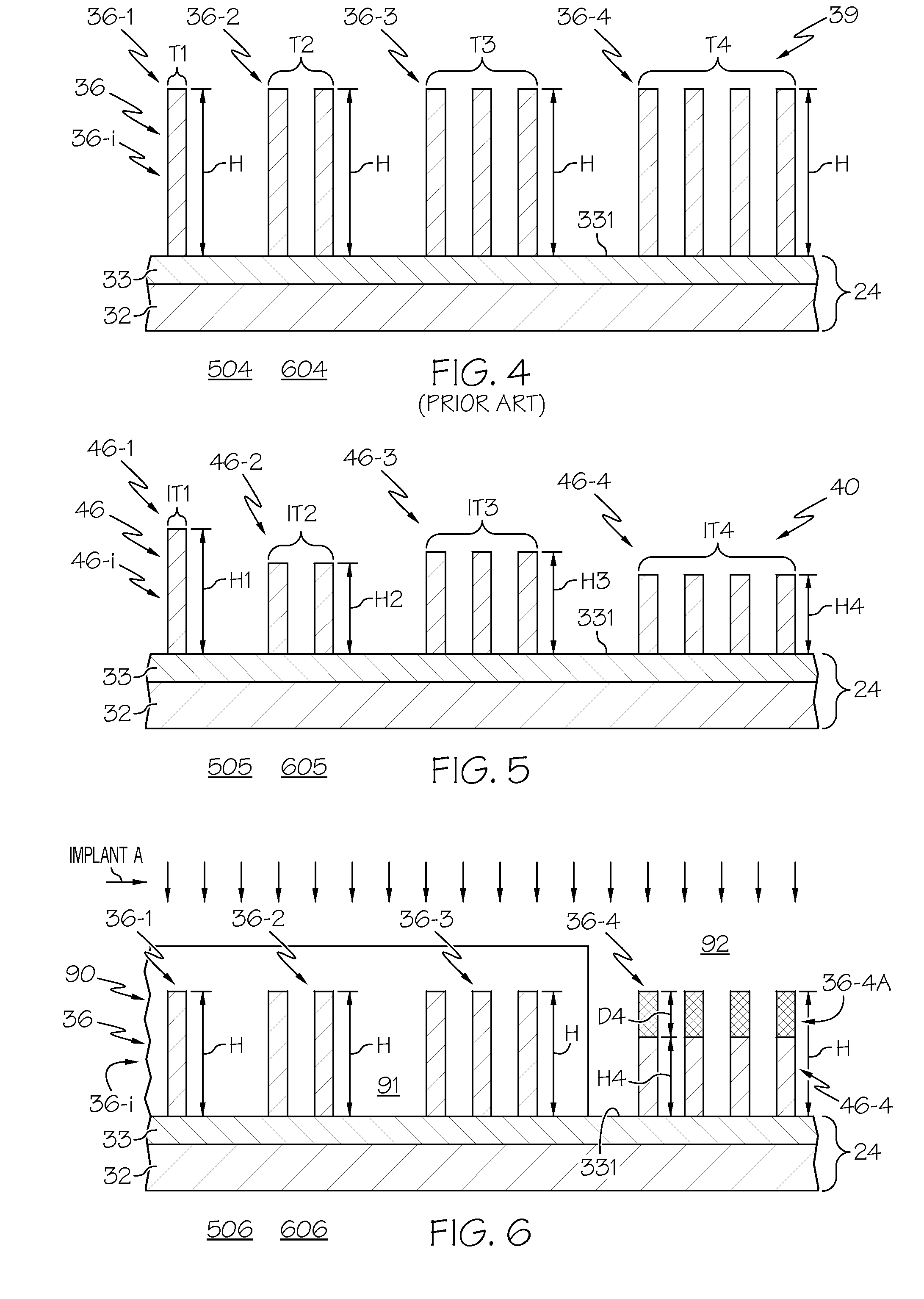

InactiveUS20120313169A1Semiconductor/solid-state device testing/measurementSolid-state devicesEngineeringFin height

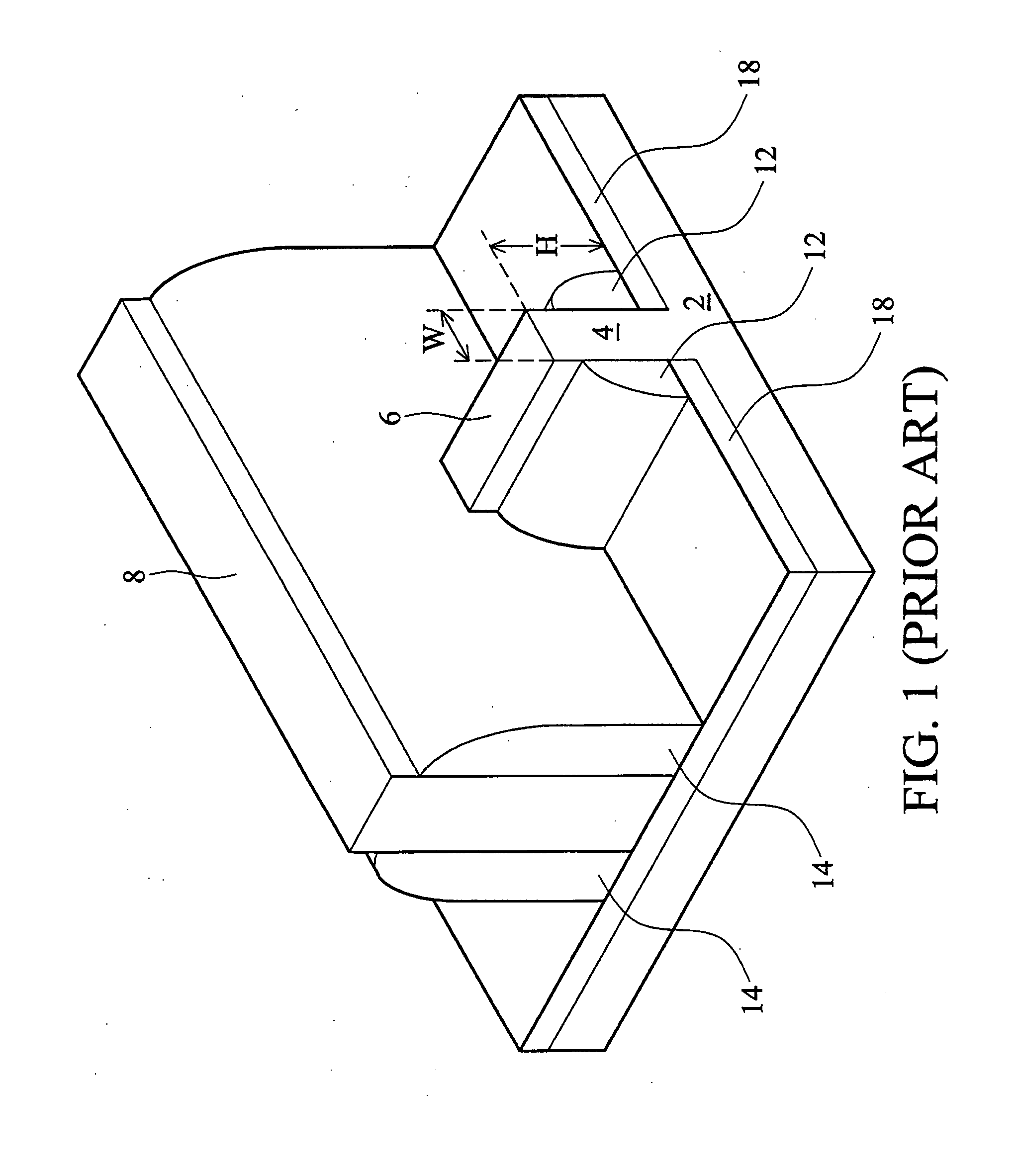

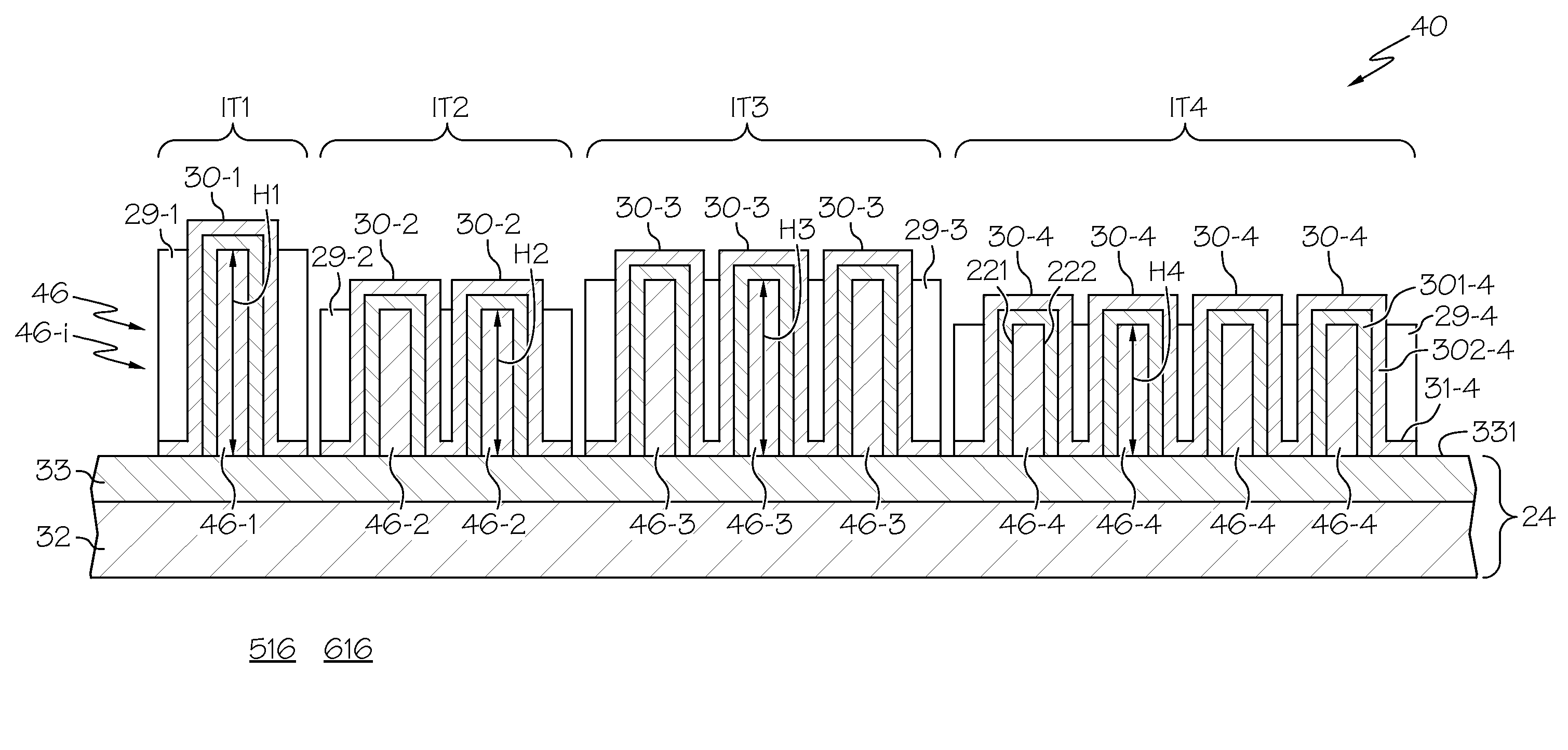

FIN-FET ICs with adjustable FIN-FET channel widths are formed from a semiconductor layer (42). Fins (36) may be etched from the layer (42) and then some (46) locally shortened or the layer (42) may be locally thinned and then fins (46) of different fin heights etched therefrom. Either way provides fins (46) and FIN-FETs (40) with different channel widths W on the same substrate (24). Fin heights (H) are preferably shortened by implanting selected ions (A, B, C, etc.) through a mask (90, 90′, 94, 94′, 97, 97′) to locally enhance the etch rate of the layer (42) or some of the fins (36). The implant(s) (A, B, C, etc.) is desirably annealed and then differentially etched. This thins part(s) (42-i) of the layer (42) from which the fins (46) are then etched or shortens some of the fins (46) already etched from the layer (42). For silicon, germanium is a suitable implant ion. Having fins (42) with adjustable fin heights Hi on the same substrate (24) enables such FIN-FET ICs (40) to avoid channel-width quantization effects observed with prior art uniform fin height FIN-FETs (20).

Owner:ALSEPHINA INNOVATIONS INC

Semiconductor structures and methods for forming isolation between fin structures of finfet devices

ActiveUS20110068431A1Low variabilitySemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureEngineering

Semiconductor structures and methods for forming isolation between fin structures formed from a bulk silicon wafer are provided. A bulk silicon wafer is provided having one or more fin structures formed therefrom. Forming of the fin structures defines isolation trenches between the one or more fin structures. Each of the fin structures has vertical sidewalls. An oxide layer is deposited in the isolation trenches and on the vertical sidewalls using HPDCVD in about a 4:1 ratio or greater. The oxide layer is isotropically etched to remove the oxide layer from the vertical sidewalls and a portion of the oxide layer from the bottom of the isolation trenches. A substantially uniformly thick isolating oxide layer is formed on the bottom of the isolation trench to isolate the one or more fin structures and substantially reduce fin height variability.

Owner:GLOBALFOUNDRIES US INC

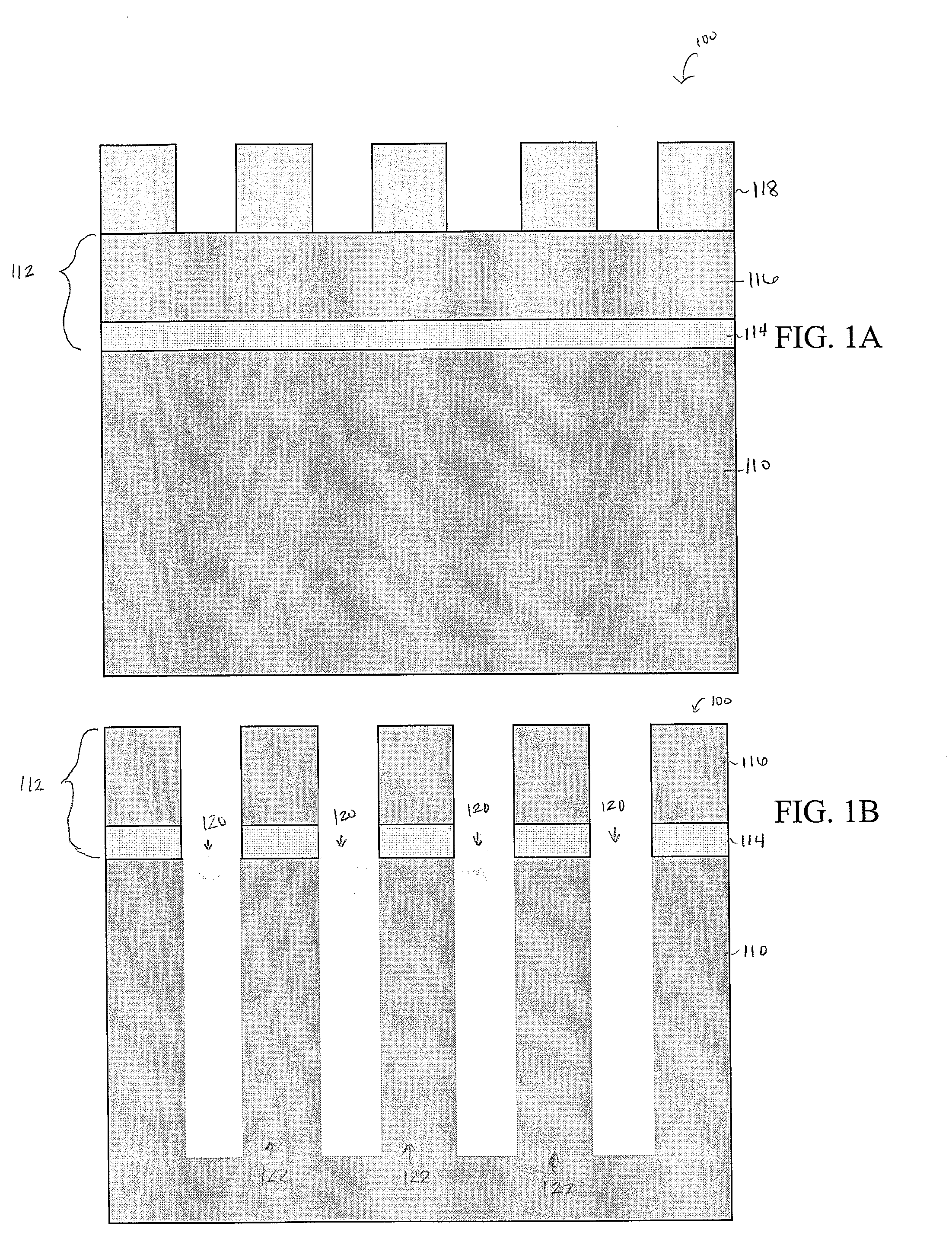

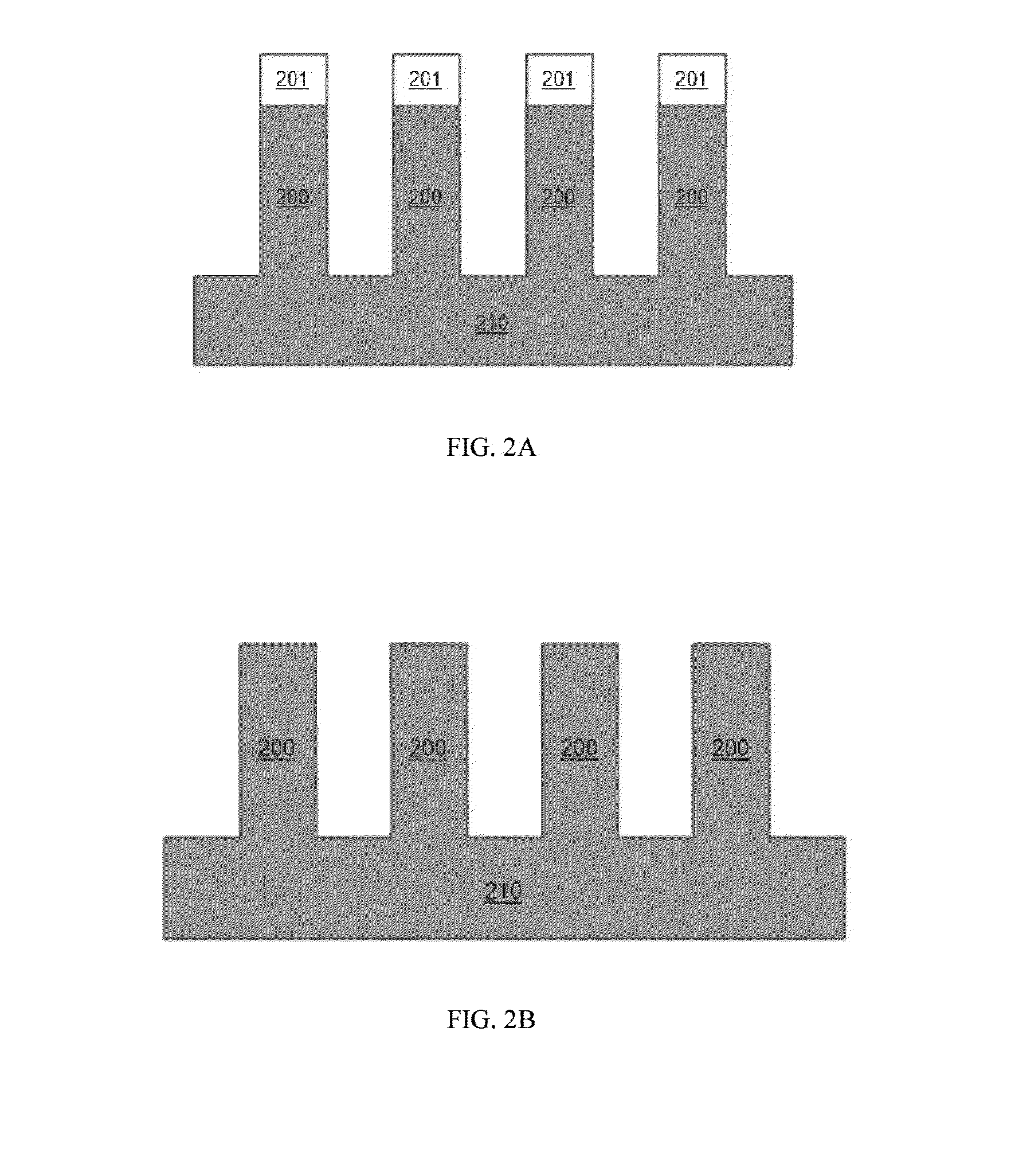

Finfet integrated circuits with uniform fin height and methods for fabricating the same

Methods for fabricating FinFET integrated circuits with uniform fin height and ICs fabricated from such methods are provided. A method includes etching a substrate using an etch mask to form fins. A first oxide is formed between the fins. A first etch stop is deposited on the first oxide. A second oxide is formed on the first etch stop. A second etch stop is deposited on the second oxide. A third oxide is deposited overlying the second etch stop. An STI extends from at least a surface of the substrate to at least a surface of the second etch stop overlying the fins to form a first active region and a second active region. The first etch stop overlying the fins is removed. The third oxide is removed to expose the second etch stop. A gate stack is formed overlying a portion of each of the fins.

Owner:GLOBALFOUNDRIES US INC

Semiconductor device having multiple fin heights

A semiconductor device having multiple fin heights is provided. Multiple fin heights are provided by using multiple masks to recess a dielectric layer within a trench formed in a substrate. In another embodiment, an implant mold or e-beam lithography are utilized to form a pattern of trenches in a photoresist material. Subsequent etching steps form corresponding trenches in the underlying substrate. In yet another embodiment, multiple masking layers are used to etch trenches of different heights separately. A dielectric region may be formed along the bottom of the trenches to isolate the fins by performing an ion implant and a subsequent anneal.

Owner:TAIWAN SEMICON MFG CO LTD

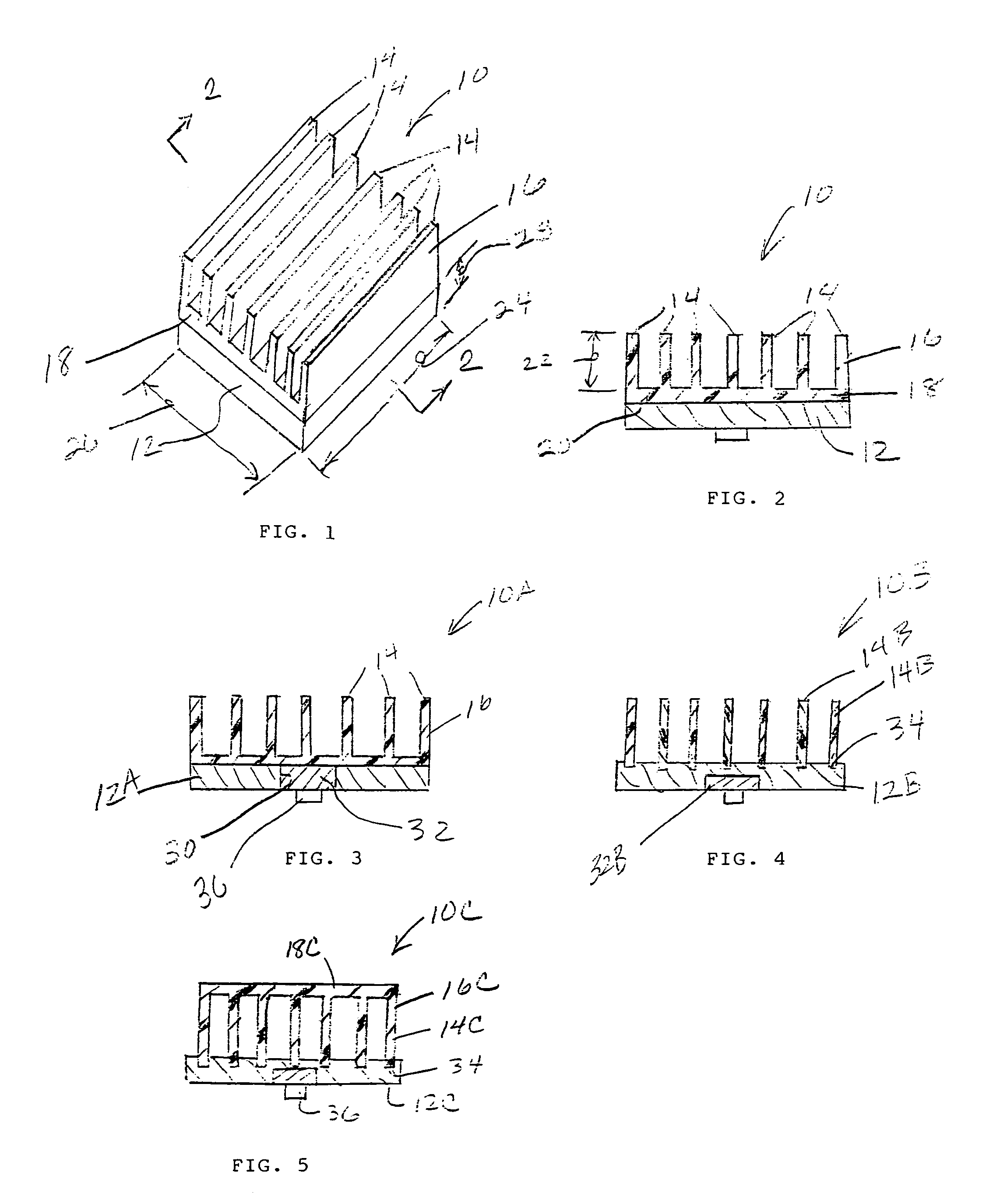

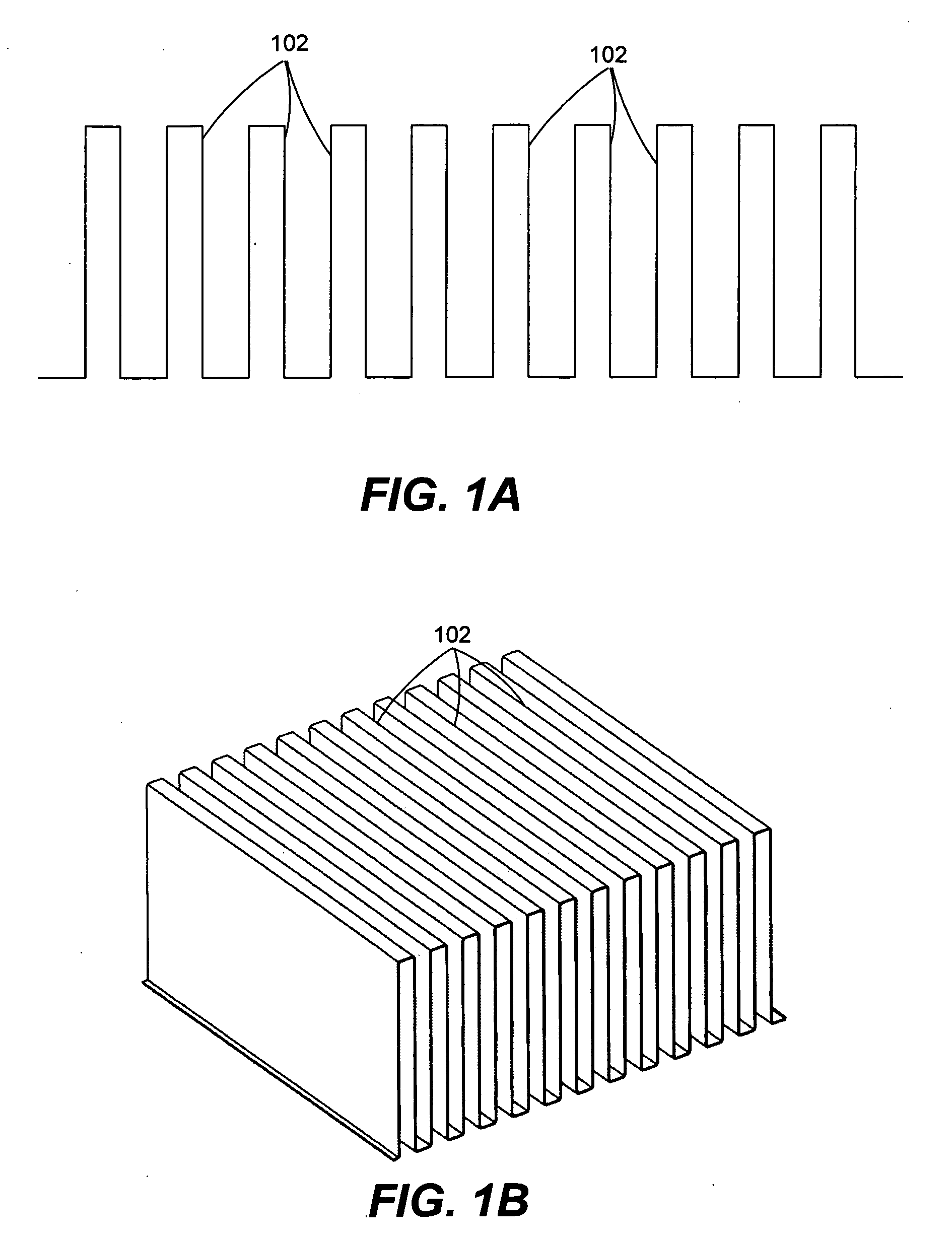

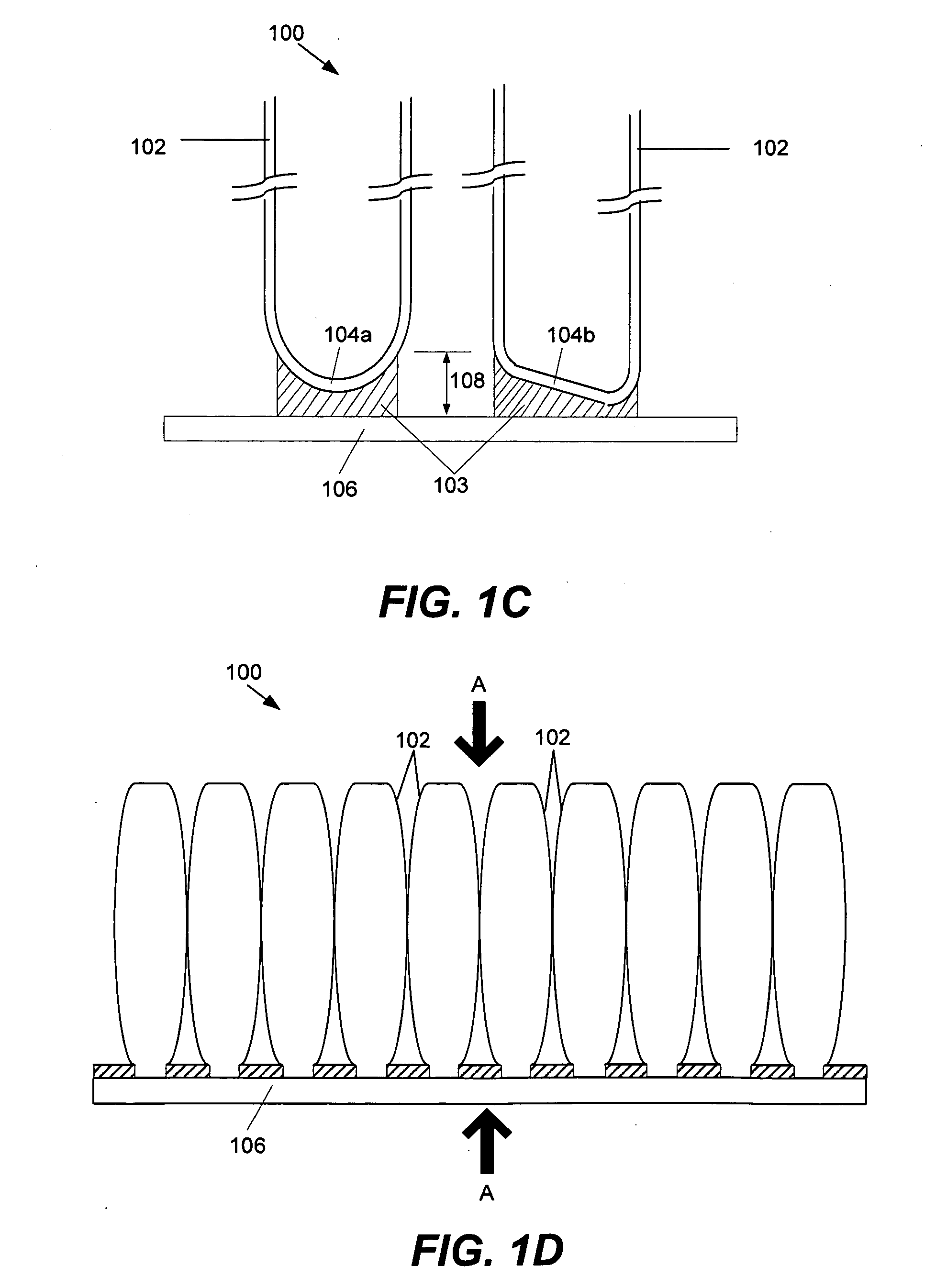

Optimized heat sink using high thermal conducting base and low thermal conducting fins

InactiveUS7108055B2Cheap constructionSemiconductor/solid-state device detailsSolid-state devicesComposite constructionPlastic materials

An optimized design for a composite heat sink is provided utilizing a high thermal conducting base and low thermal conducting fins. The base preferably is constructed from anisotropic graphite material, and the fins are preferably constructed from a thermally conductive plastic material. In the case of a low profile heat sink having a fin height of no greater than about 3 times that of the base, the composite construction provides superior cooling yet lighter weight as compared to a conventional all-aluminum heat sink of the same dimensions.

Owner:NEOGRAF SOLUTIONS LLC

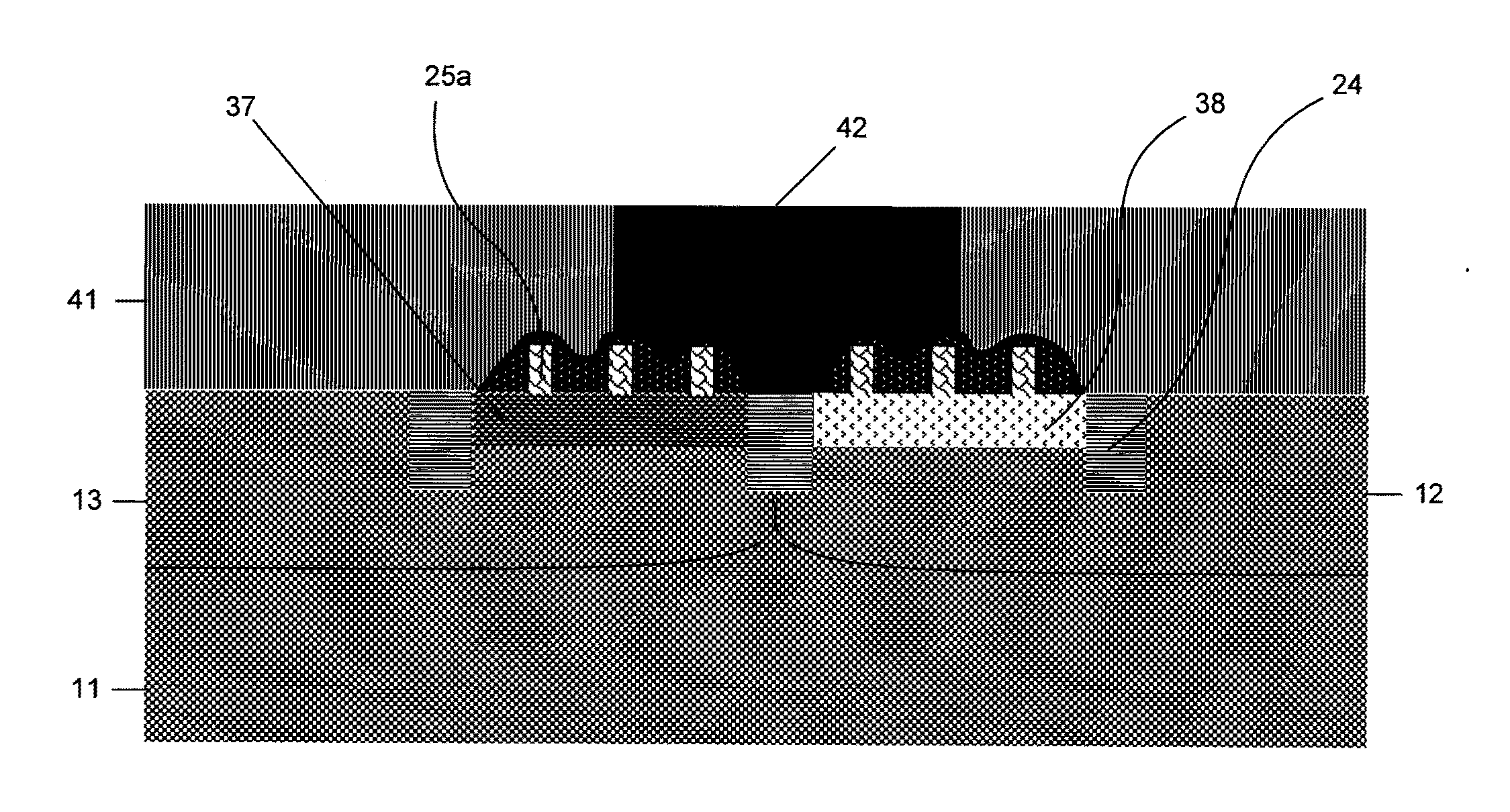

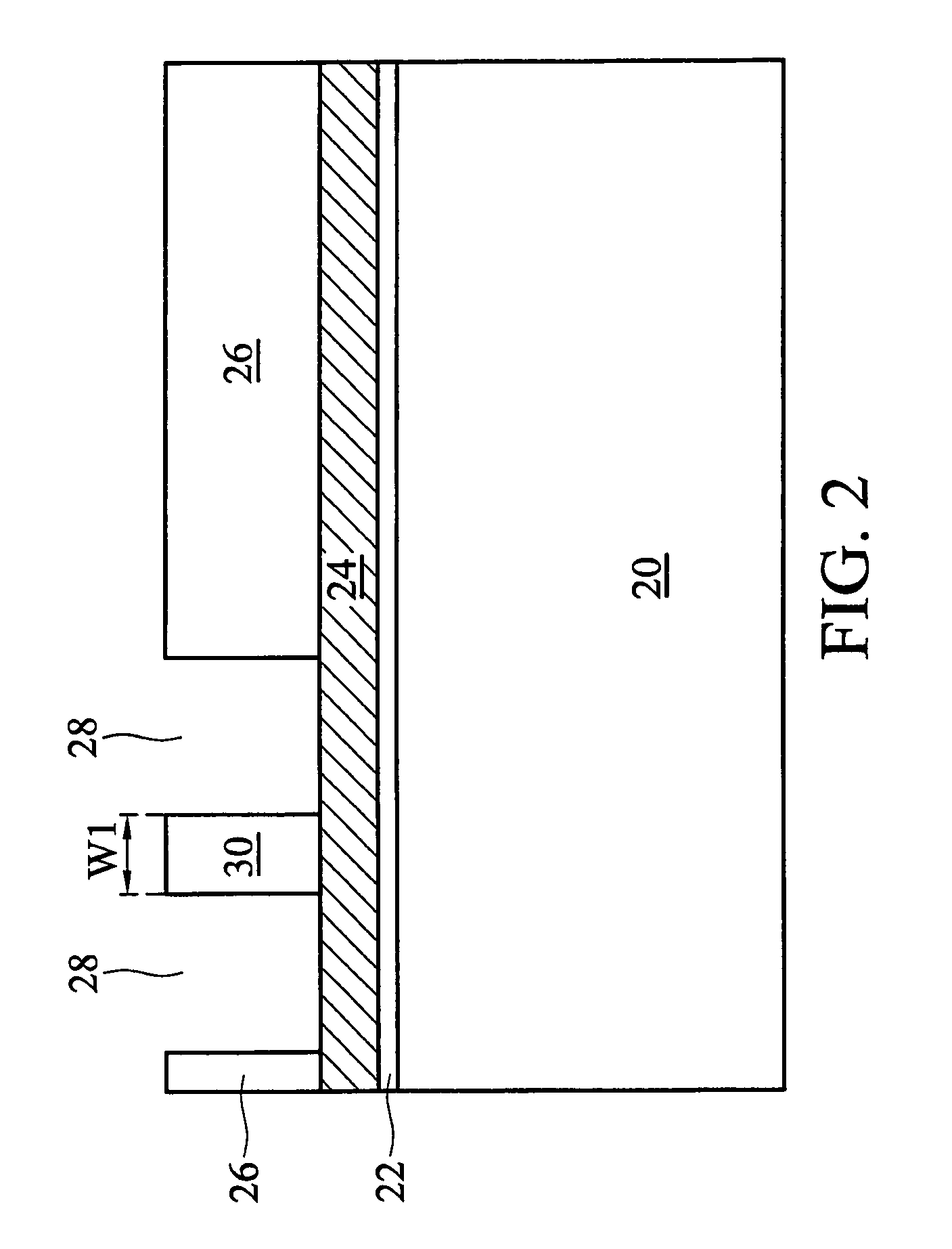

Process for Forming FINS for a FinFET Device

ActiveUS20120025316A1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringField-effect transistor

An integrated fin-based field effect transistor (FinFET) and method of fabricating such devices on a bulk wafer with EPI-defined fin heights over shallow trench isolation (STI) regions. The FinFET channels overlie the STI regions within the semiconductor bulk, while the fins extend beyond the STI regions into the source and drain regions which are implanted within the semiconductor bulk. With bulk source and drain regions, reduced external FinFET resistance is provided, and with the fins extending into the bulk source and drain regions, improved thermal properties is provided over conventional silicon on insulator (SOI) devices.

Owner:ADVANCED MICRO DEVICES INC

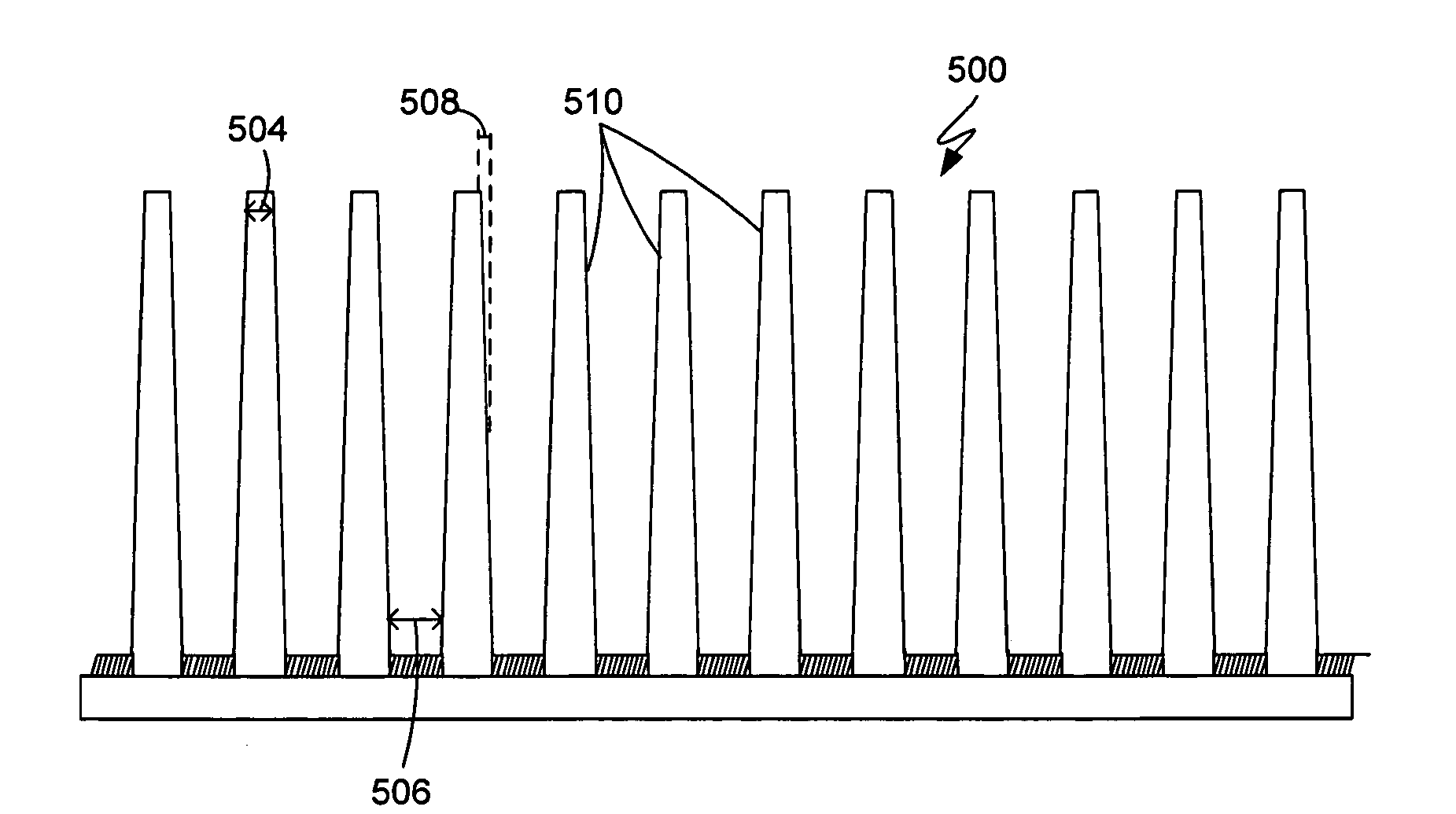

Finfet fin height control

Fin height control techniques for FINFET fabrication are disclosed. The technique includes a method for controlling the height of plurality of fin structures to achieve uniform height thereof relative to a top surface of isolation material located between fin structures on a semiconductor substrate. The isolation material located between fin structures may be selectively removed after treatment to increase its mechanical strength such as by, for example, annealing and curing. A sacrificial material may be deposited over the isolation material between the fin structures in a substantially uniform thickness. The top portion of the fin structures may be selectively removed to achieve a uniform planar surface over the fin structures and sacrificial material. The sacrificial material may then be selectively removed to achieve a uniform fin height relative to the isolation material.

Owner:ALSEPHINA INNOVATIONS INC

Fabrication of FinFETs with multiple fin heights

A semiconductor structure includes a first semiconductor strip extending from a top surface of the semiconductor substrate into the semiconductor substrate, wherein the first semiconductor strip has a first height. A first insulating region is formed in the semiconductor substrate and surrounding a bottom portion of the first semiconductor strip, wherein the first insulating region has a first top surface lower than a top surface of the first semiconductor strip. A second semiconductor strip extends from a top surface of the semiconductor substrate into the semiconductor substrate, wherein the second semiconductor strip has a second height greater than the first height. A second insulating region is formed in the semiconductor substrate and surrounding a bottom portion of the second semiconductor strip, wherein the second insulating region has a second top surface lower than the first top surface, and wherein the first and the second insulating regions have substantially same thicknesses.

Owner:TAIWAN SEMICON MFG CO LTD

Solar receiver

In one embodiment, a solar receiver has a base plate having a first surface and a second surface, a plurality of solar cells positioned over and supported by the first surface of the base plate, and a multiplicity of fins extending outwardly from the second surface of the base plate. Each of the multiplicity of fins has a fin height axis extending generally perpendicular relative to the base plate, a fin length axis extending generally in parallel with the base plate, and a bottom end attached to the second surface of the base plate, wherein each of the multiplicity of fins are formed from a single, continuous sheet of metal arranged in a serpentine configuration, and wherein each of the multiplicity of fins have a plurality of undulations along the length axis of the fin.

Owner:SKYLINE SOLAR INC

Recessing STI to increase fin height in fin-first process

A method includes forming a semiconductor fin over top surfaces of insulation regions, and forming a gate stack on a top surface and sidewalls of a middle portion of the semiconductor fin. The insulation regions include first portions overlapped by the gate stack, and second portions misaligned from the gate stack. An end portion of the semiconductor fin is etched to form a recess located between the second portions of the insulation regions. An epitaxy is performed to grow a source / drain region from the recess. After the epitaxy, a recessing is performed to recess the second portions of the insulation regions, with the second portions of the insulation regions having first top surfaces after the first recessing. A dielectric mask layer is formed on the first top surfaces of the second portions of the insulation regions. The dielectric mask layer further extends on a sidewall of the gate stack.

Owner:TAIWAN SEMICON MFG CO LTD

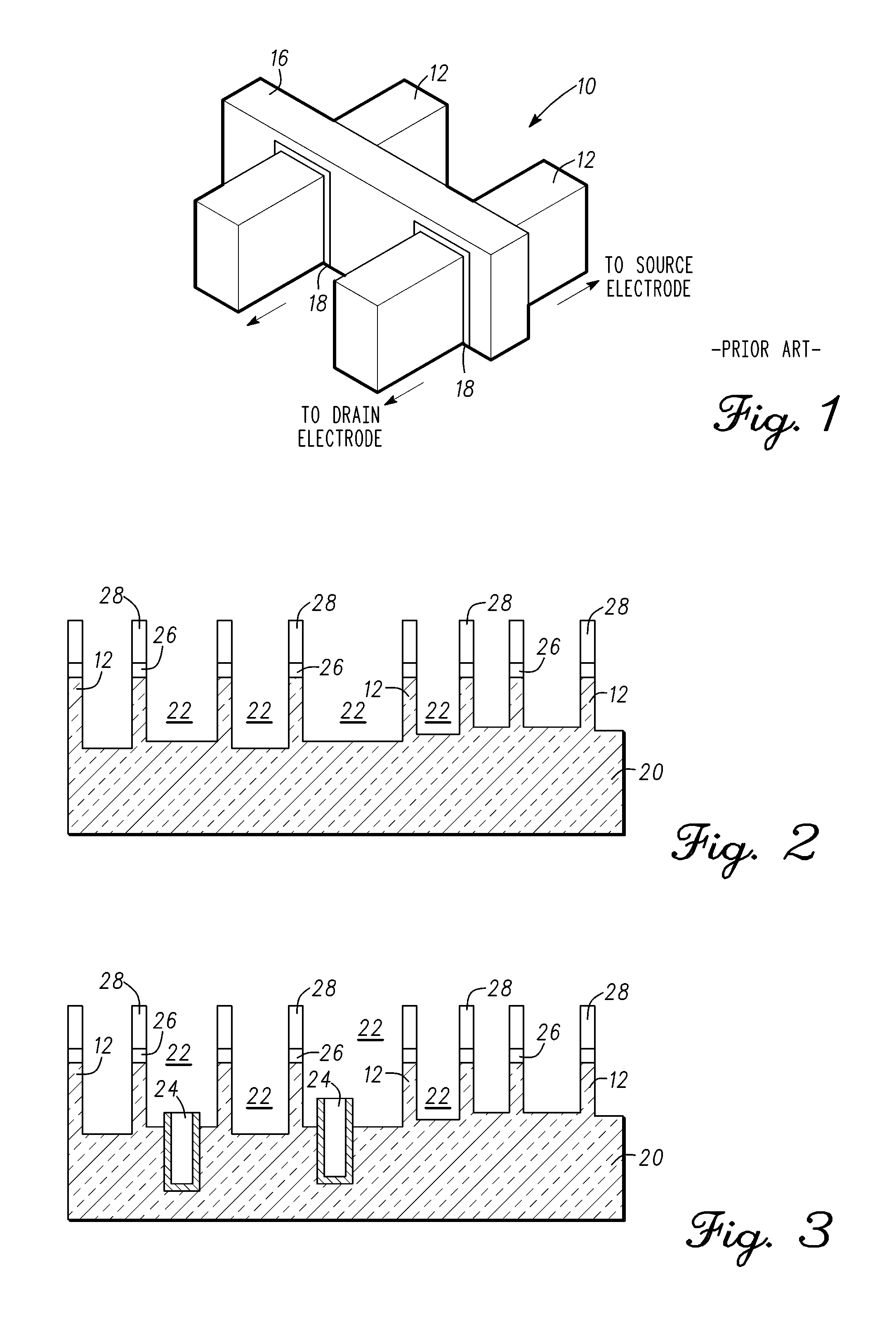

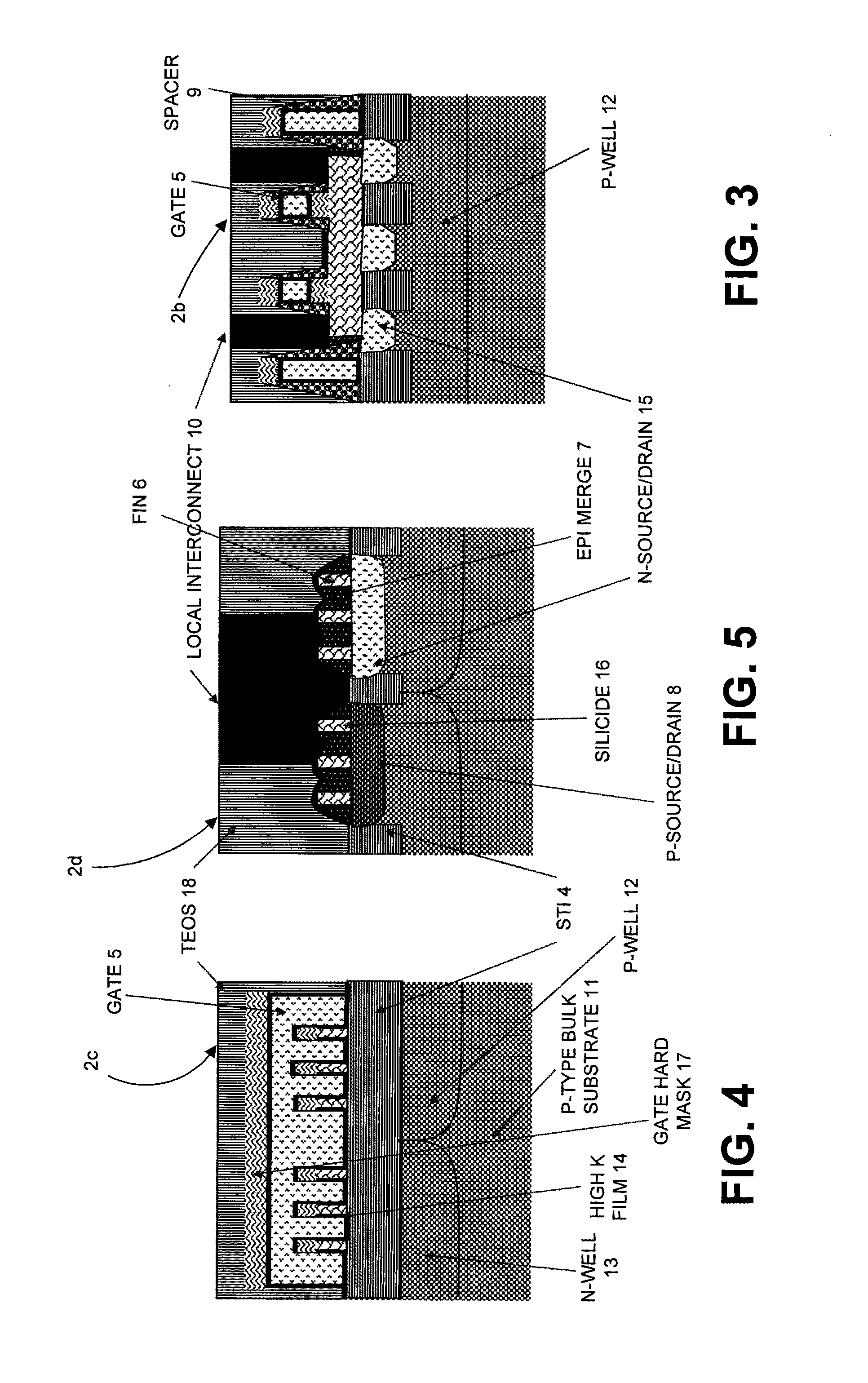

Recessed contact for multi-gate FET optimizing series resistance

ActiveUS20110049583A1Reduce parasitic resistanceReduce parasitic contact resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesFin heightTransistor

A transistor, which can be referred to as a multi-gate transistor or as a FinFET, includes a gate structure having a length, a width and a height. The transistor further includes at least one electrically conductive channel or fin between a source region and a drain region that passes through the width of the gate structure. The channel has a first height (h1) within the gate structure that is less than the height of the gate structure, and has a second height (h2) external to the gate structure, where h2 is less than h1. The transistor further includes a silicide layer disposed at least partially over the at least one channel external to the gate structure. Reducing the fin height external to the gate structure is shown to beneficially reduce parasitic resistance.

Owner:AURIGA INNOVATIONS INC

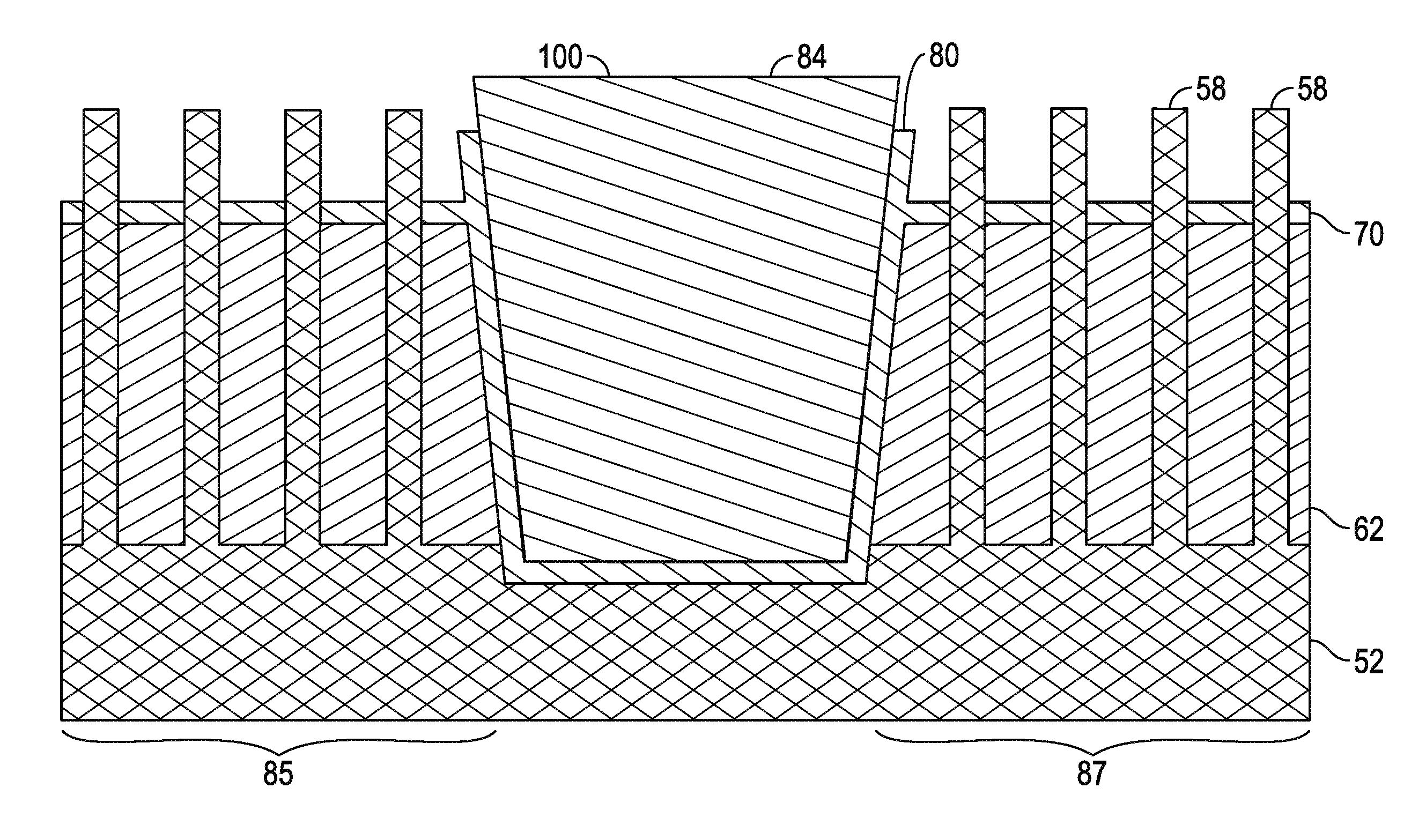

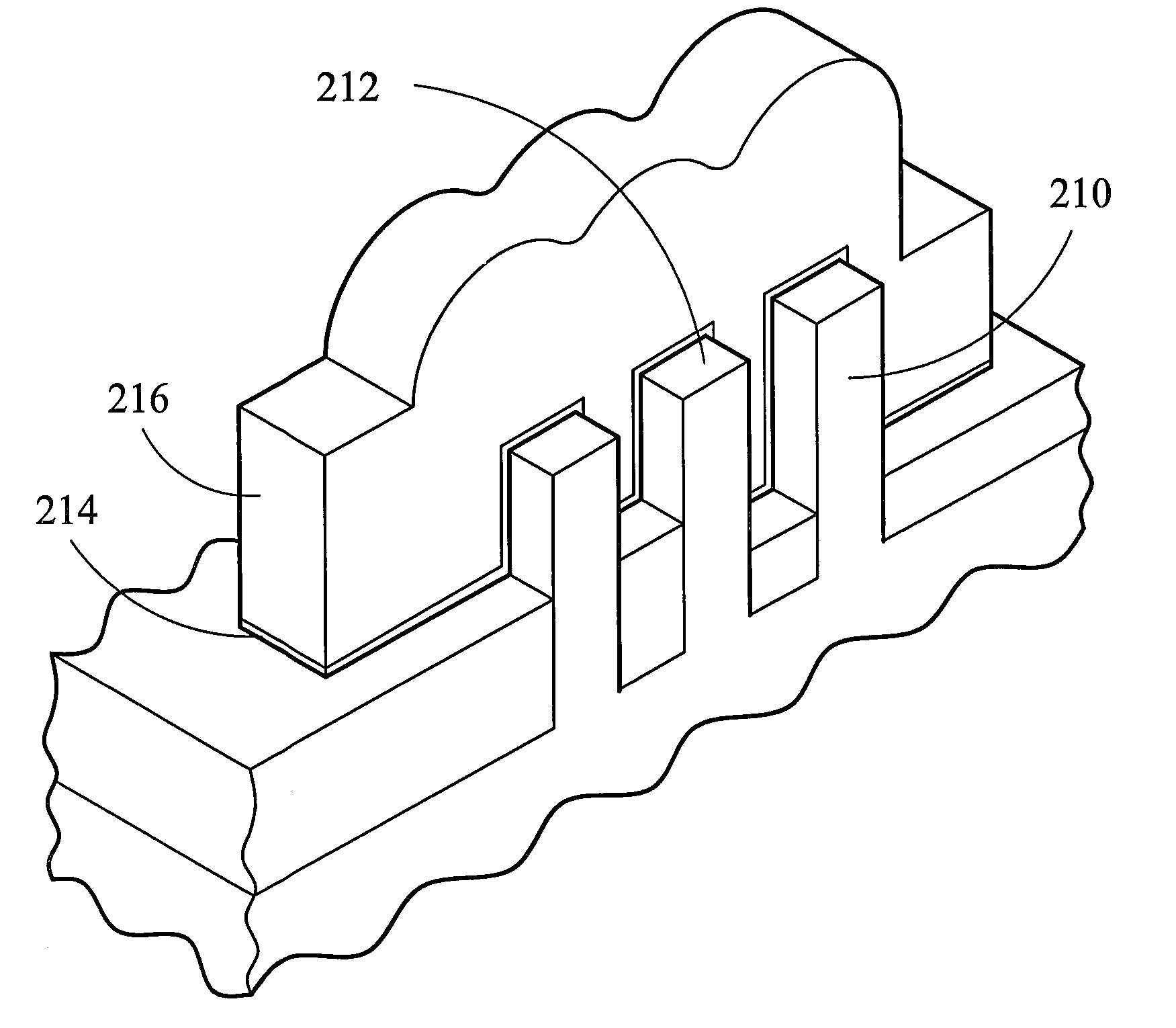

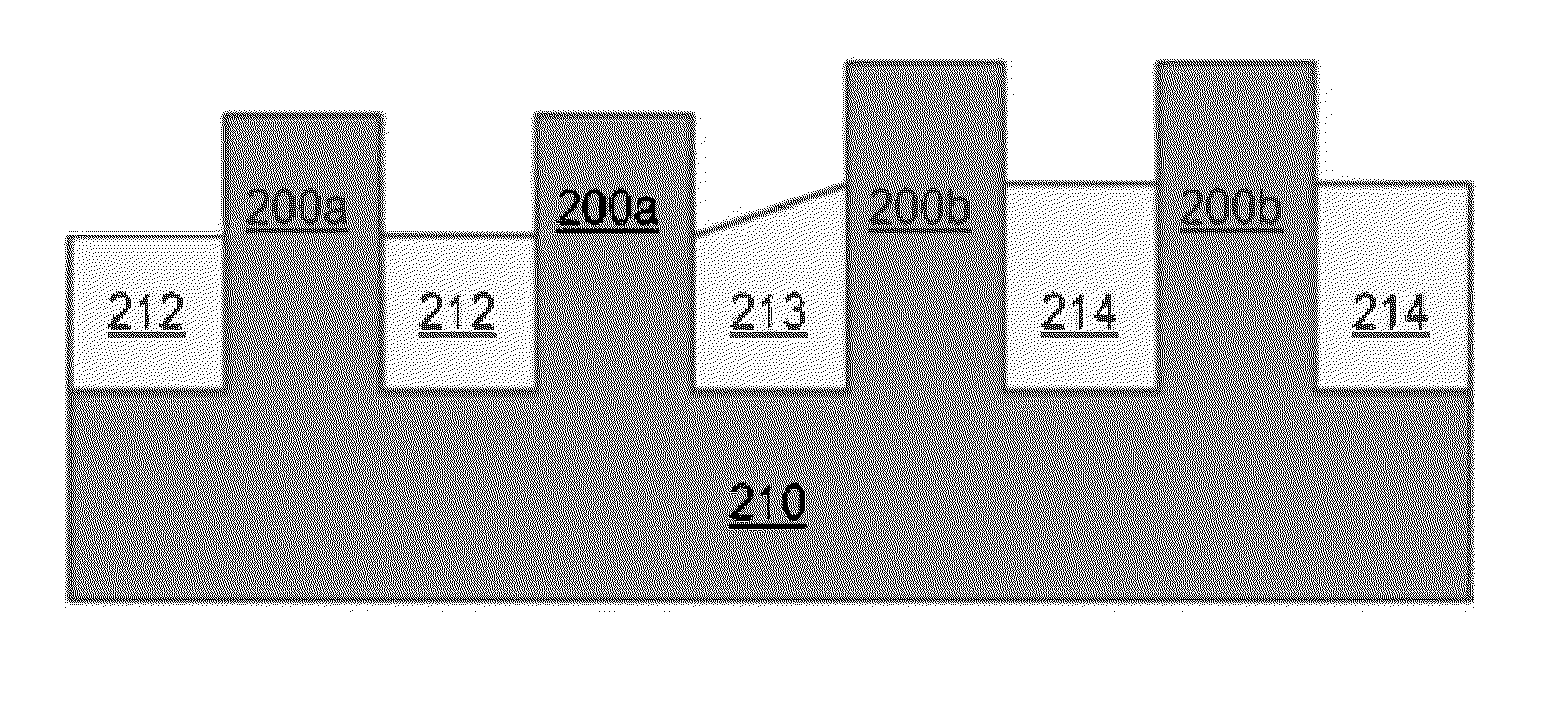

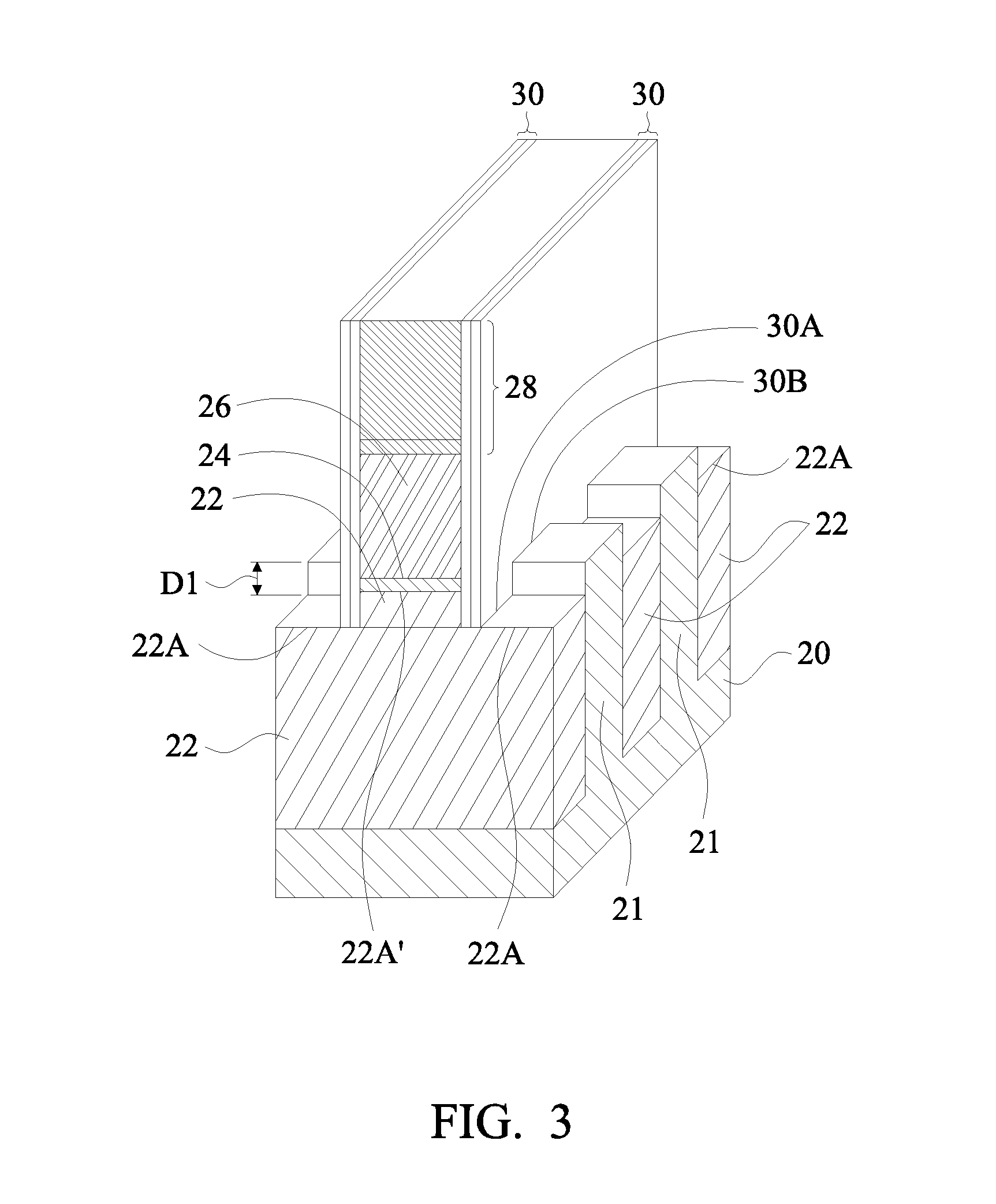

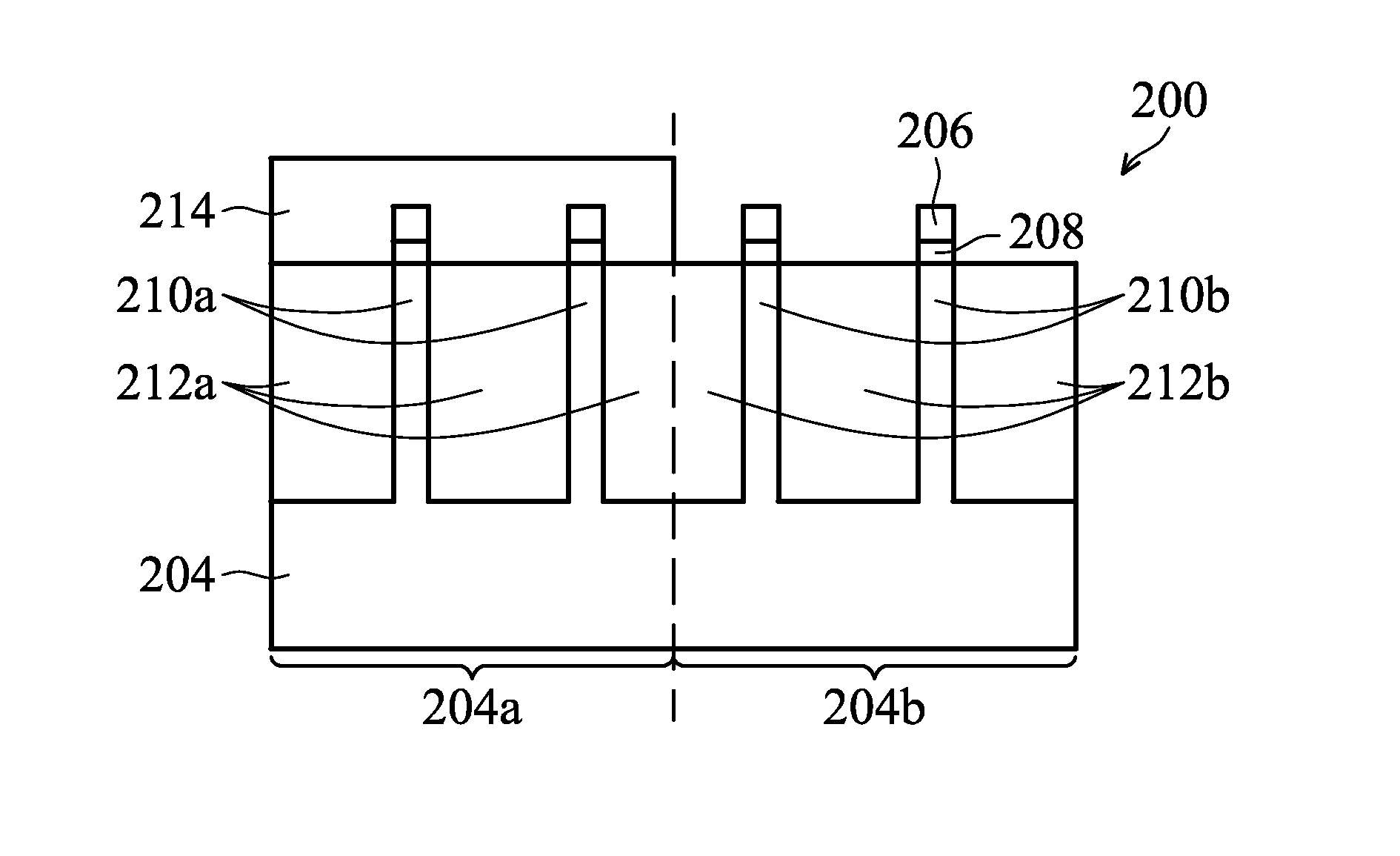

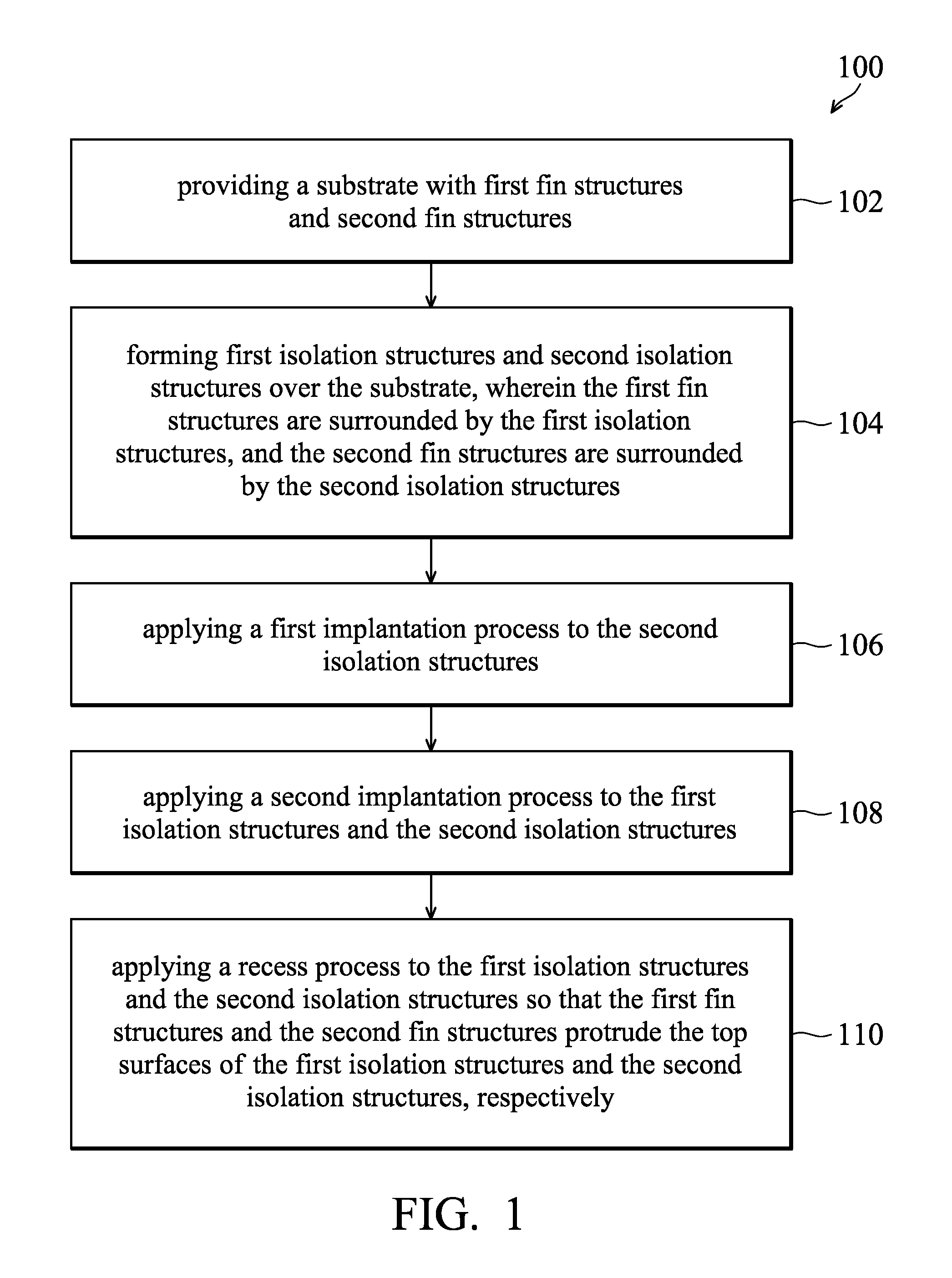

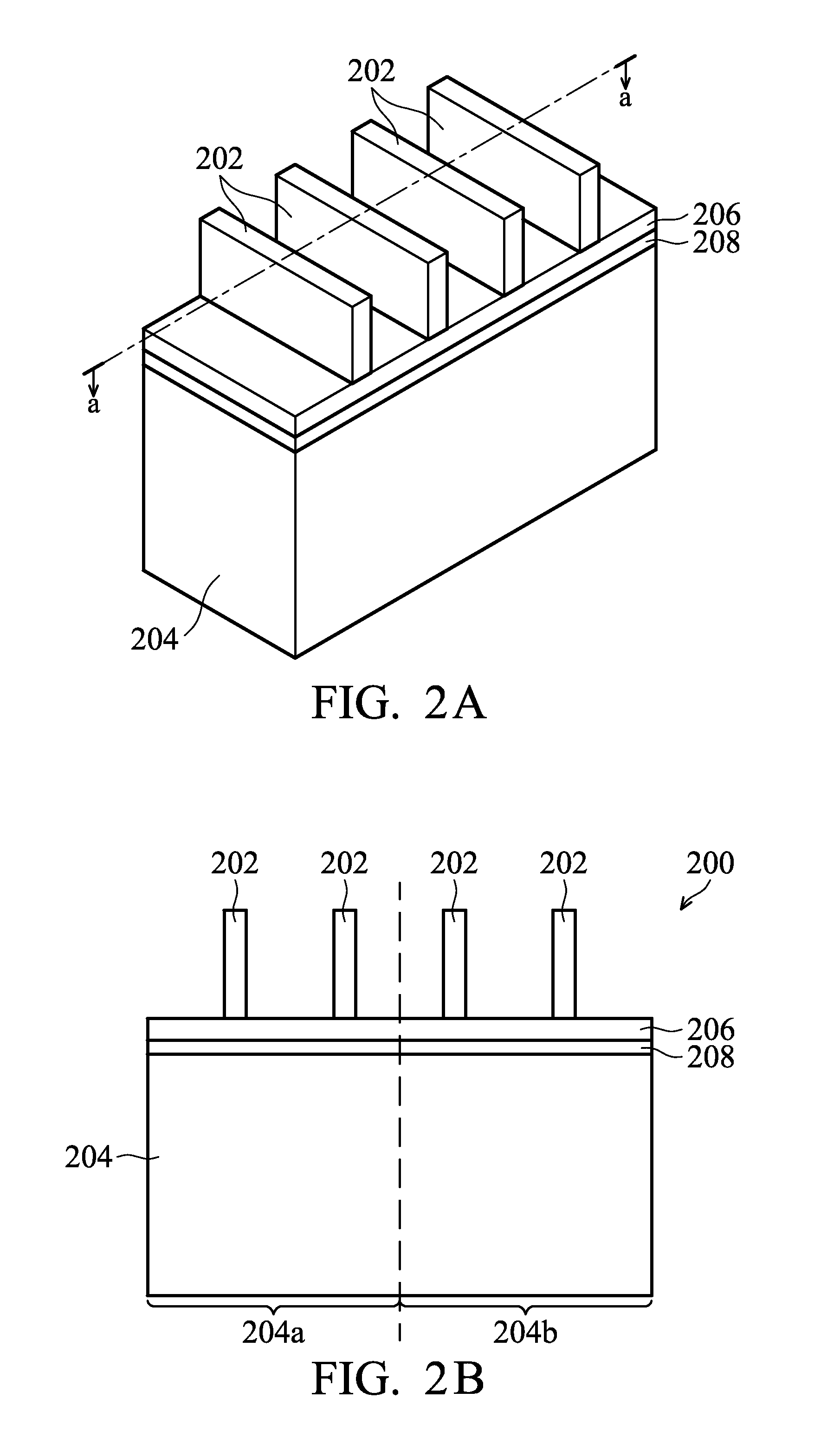

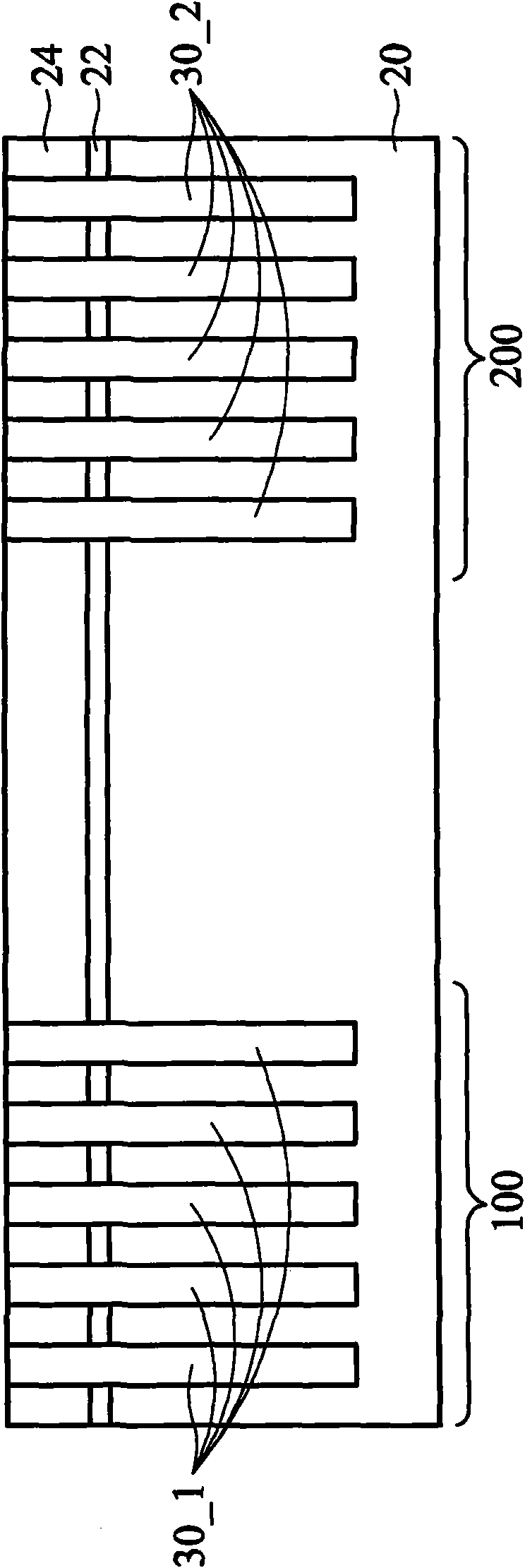

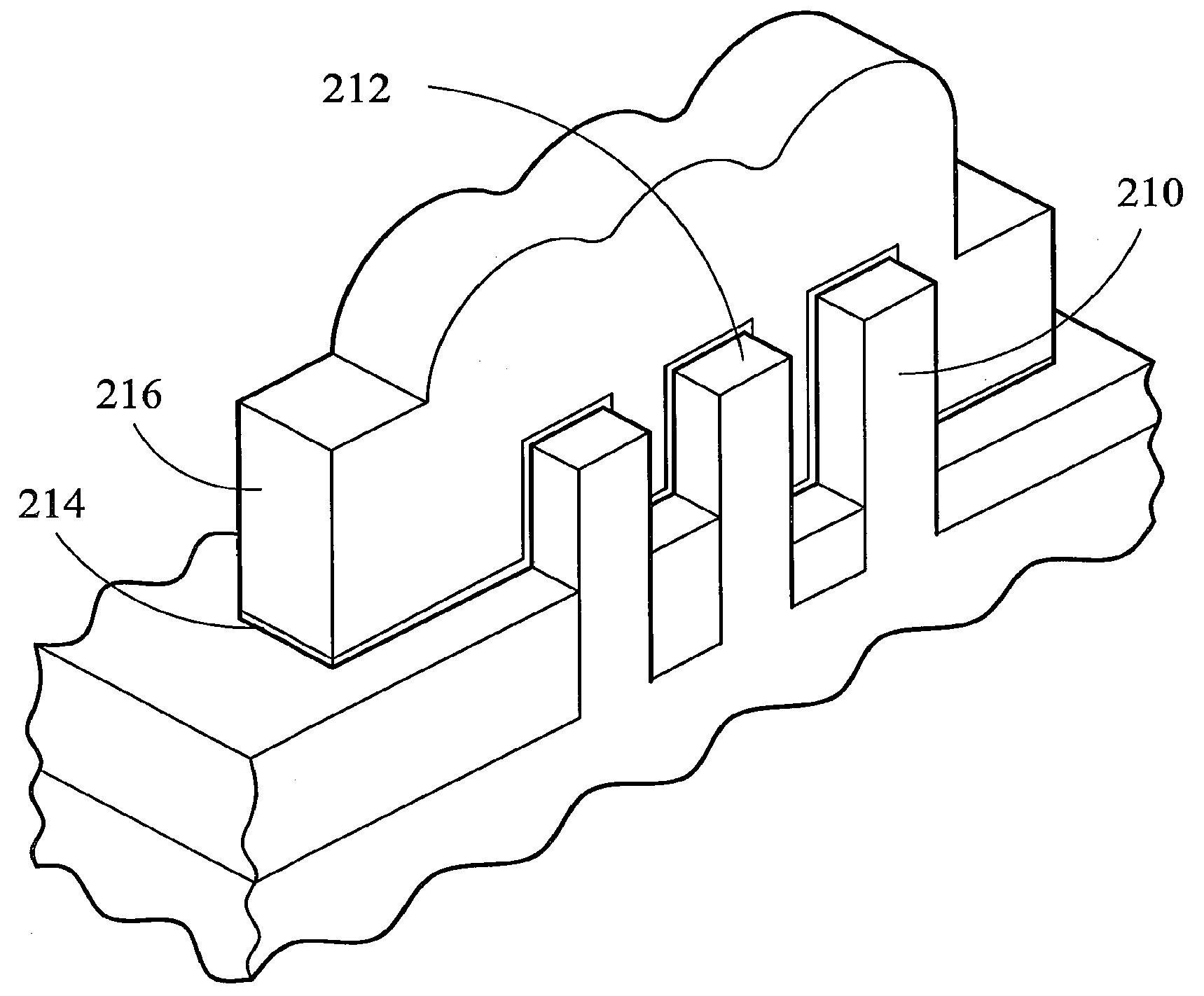

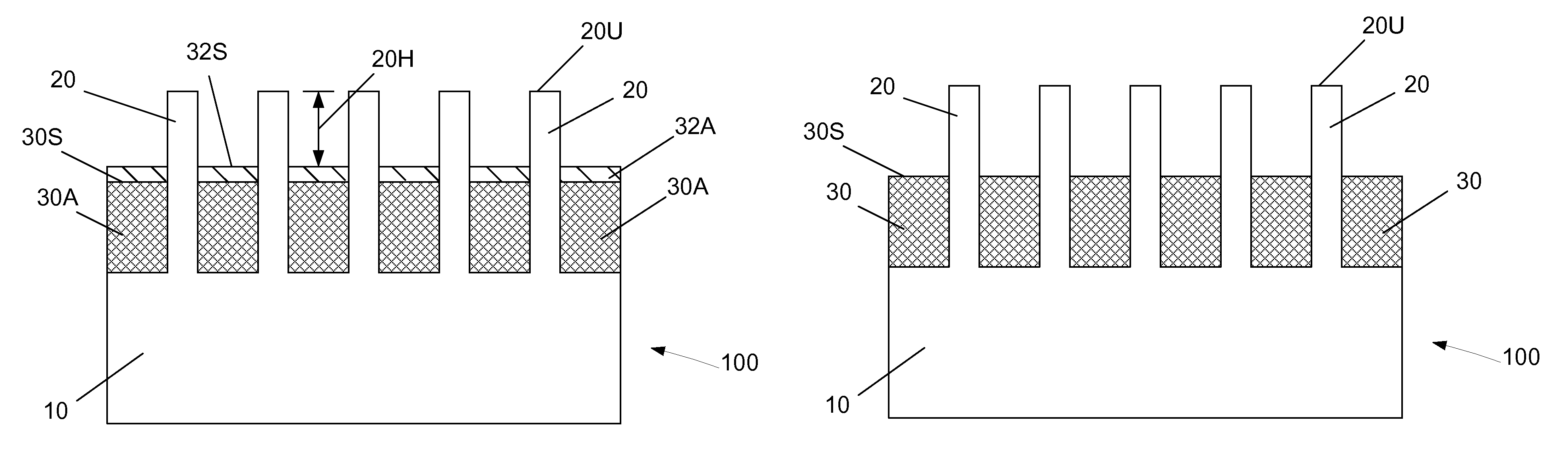

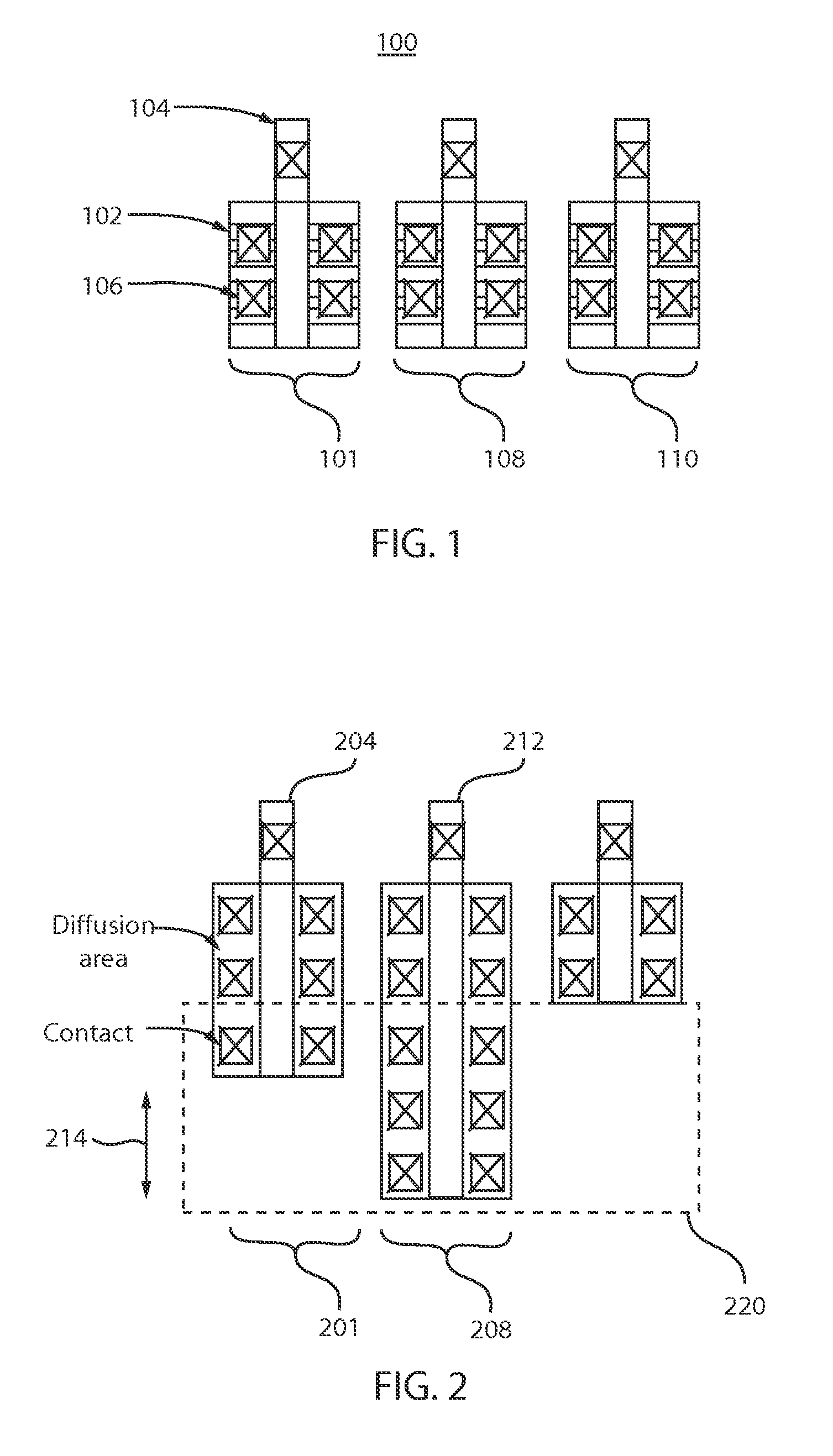

Mechanisms for forming finfets with different fin heights

Embodiments of mechanisms for forming a semiconductor device are provided. The semiconductor device includes a first fin partially surrounded by a first isolation structure and protruding through a top surface thereof. The semiconductor device also includes a second fin partially surrounded by a second isolation structure and protruding through a top surface thereof. The top surface of the first isolation structure is higher than the top surface of the second isolation structure such that the second fin has a height higher than that of the first fin. The second isolation structure has a dopant concentration higher than that of the first isolation structure.

Owner:TAIWAN SEMICON MFG CO LTD

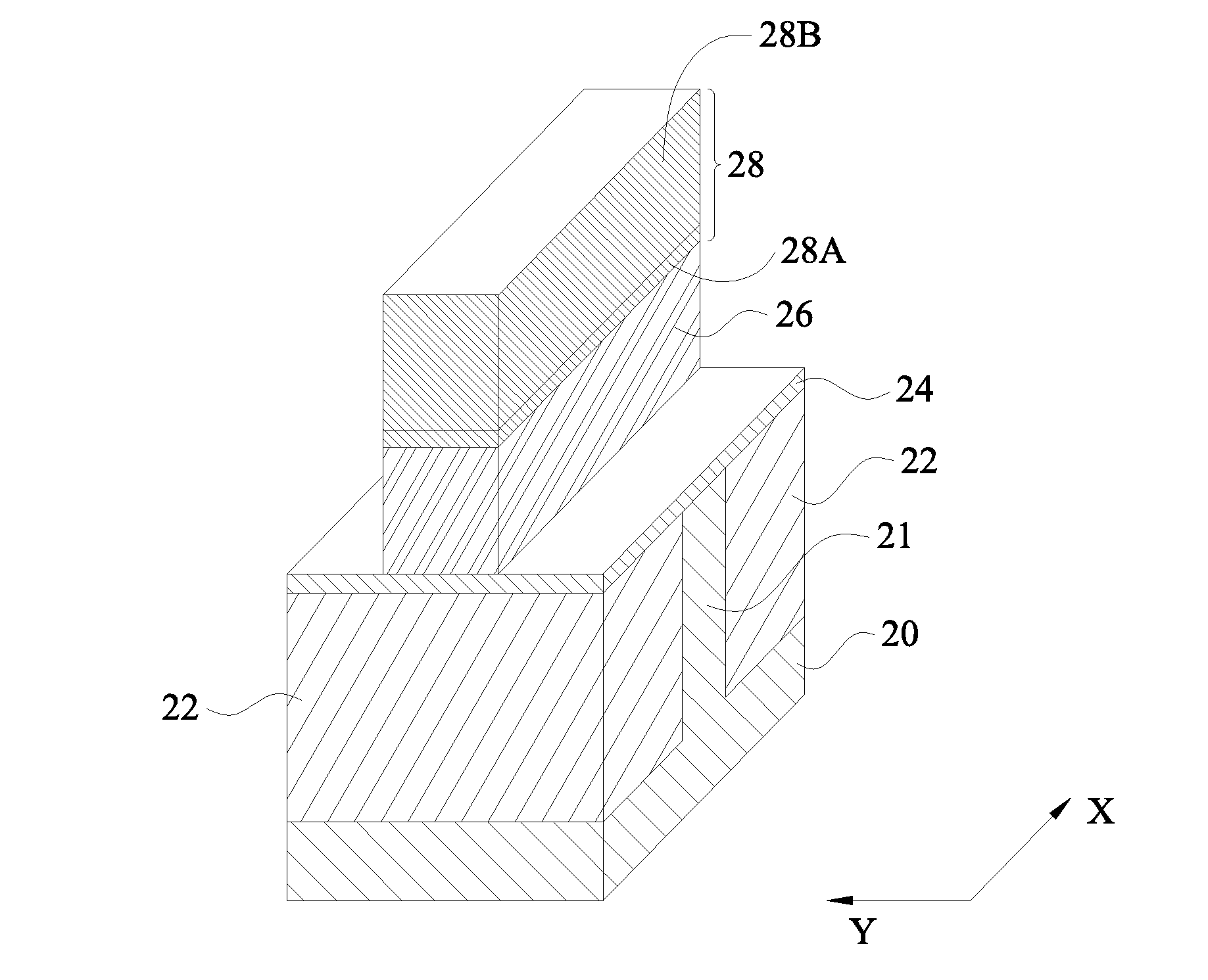

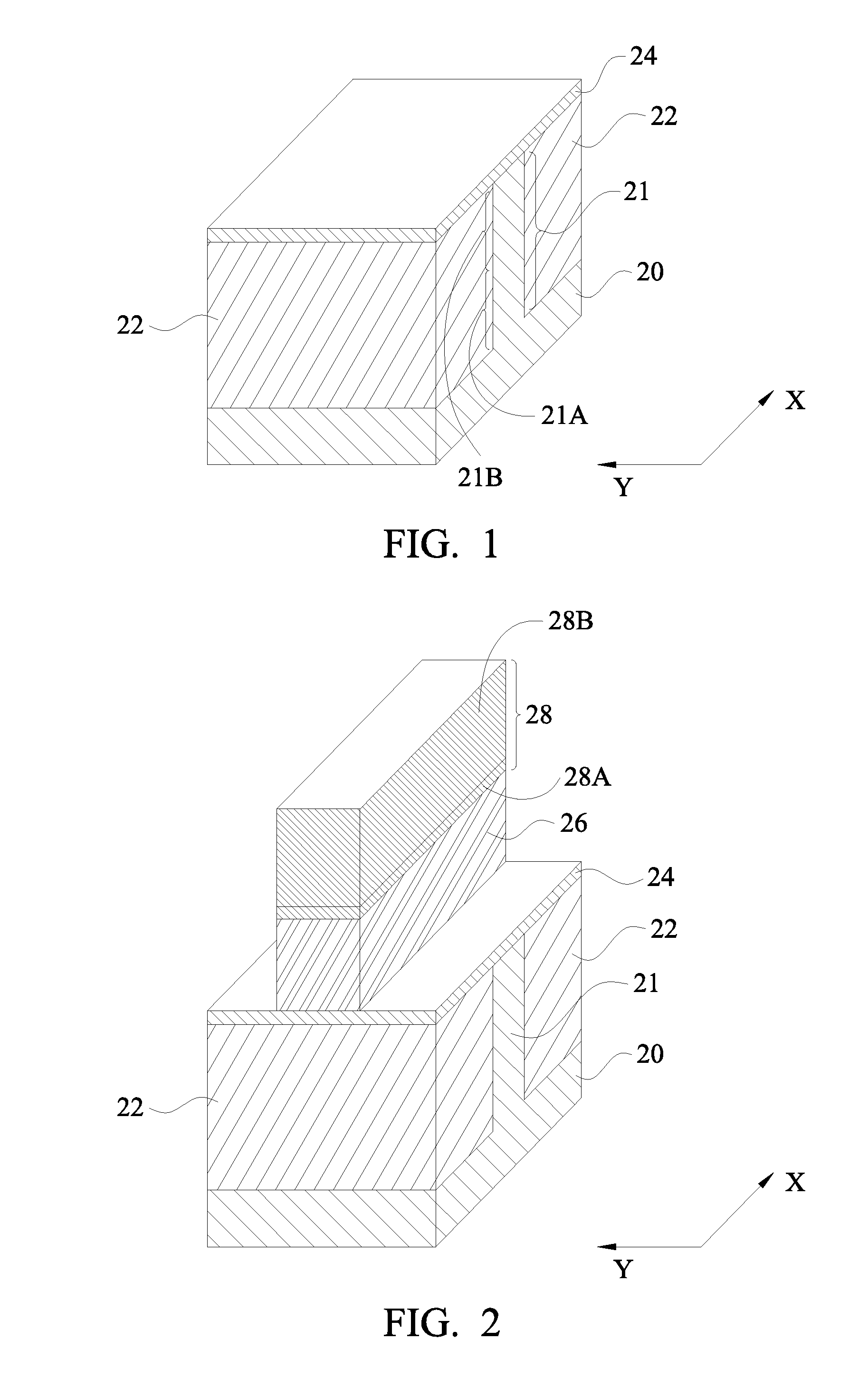

Integrated circuit structure and formation method thereof

ActiveCN102074582AReduce current crowdingReduce tensionSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorEngineering

The invention provides an integrated circuit structure and a formation method thereof, and the structure comprises a first portion in which a semiconductor substrate is contained in a first element region, and a second portion in which a semiconductor substrate is contained in a second element region. A first semiconductor fin is over the semiconductor substrate and has a first fin height. A second semiconductor fin is over the semiconductor substrate and has a second fin height. The first fin height is greater than the second fin height. The invention has a positive effect on the reduction of the current crowding at the source electrode and the drain electrode regions. Because of the volume increase of the stress source electrode and the drain electrode regions, the tension and the compression strain on the channel region of a fin-type field effect transistor are increased.

Owner:TAIWAN SEMICON MFG CO LTD

Semiconductor device having finfet structures and method of making same

ActiveUS20140252483A1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringSoi substrate

A semiconductor device and method making it comprises pFETs with an SiGe channel and nFETs with an Si channel, formed on an SOI substrate. Improved uniformity of fin height and width is attained by forming the fins additively by depositing an SiGe layer on the SOI substrate and forming first fins from the superposed SiGe layer and underlying thin Si film of the SOI substrate. Second fins of Si can then be formed by replacing the upper SiGe portions of selected first fins with Si.

Owner:RENESAS ELECTRONICS CORP

Exhaust gas heat exchanger

InactiveUS20080011464A1Improve performanceHydraulic resistanceNon-fuel substance addition to fuelInternal combustion piston enginesWater flowExhaust fumes

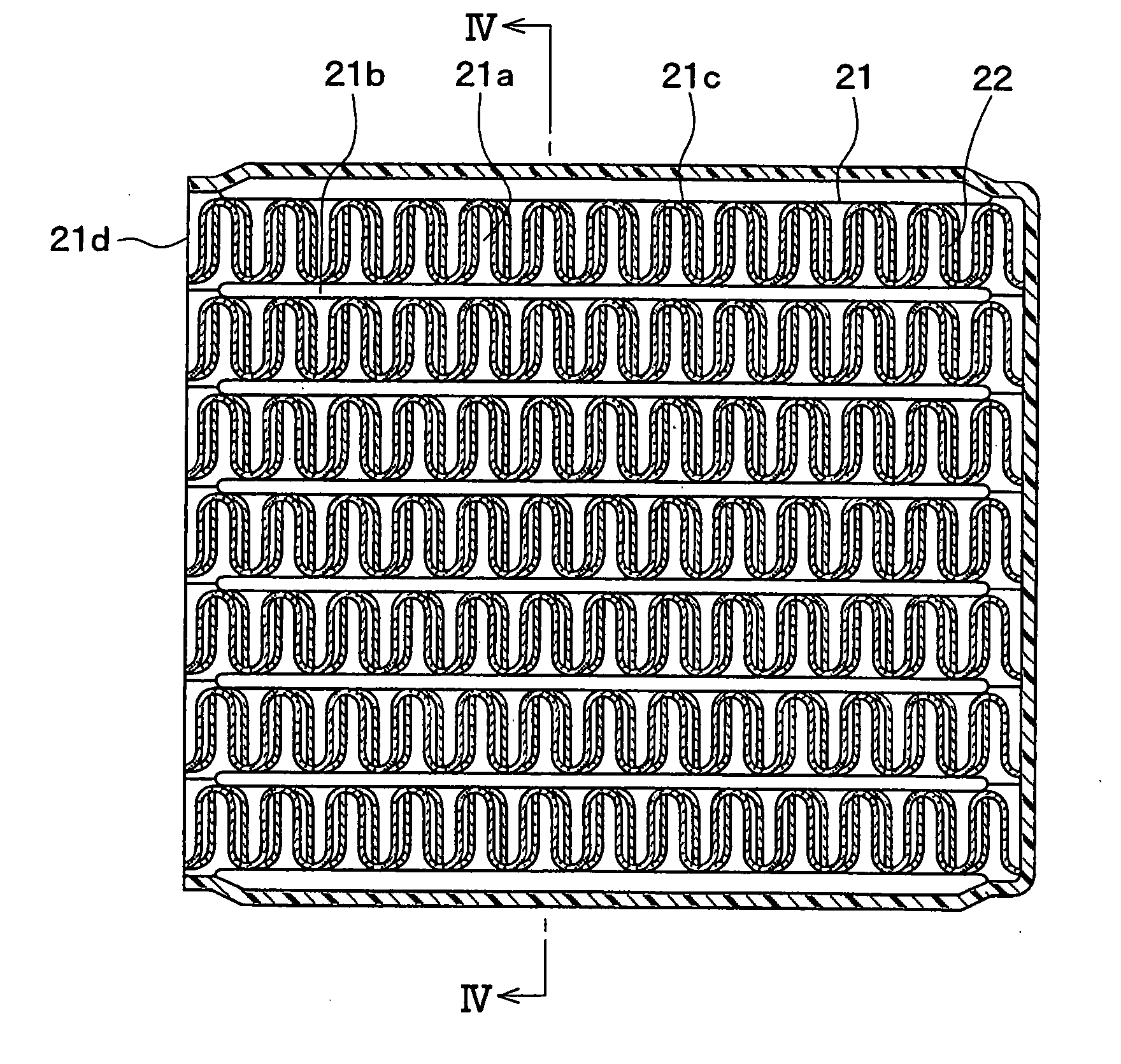

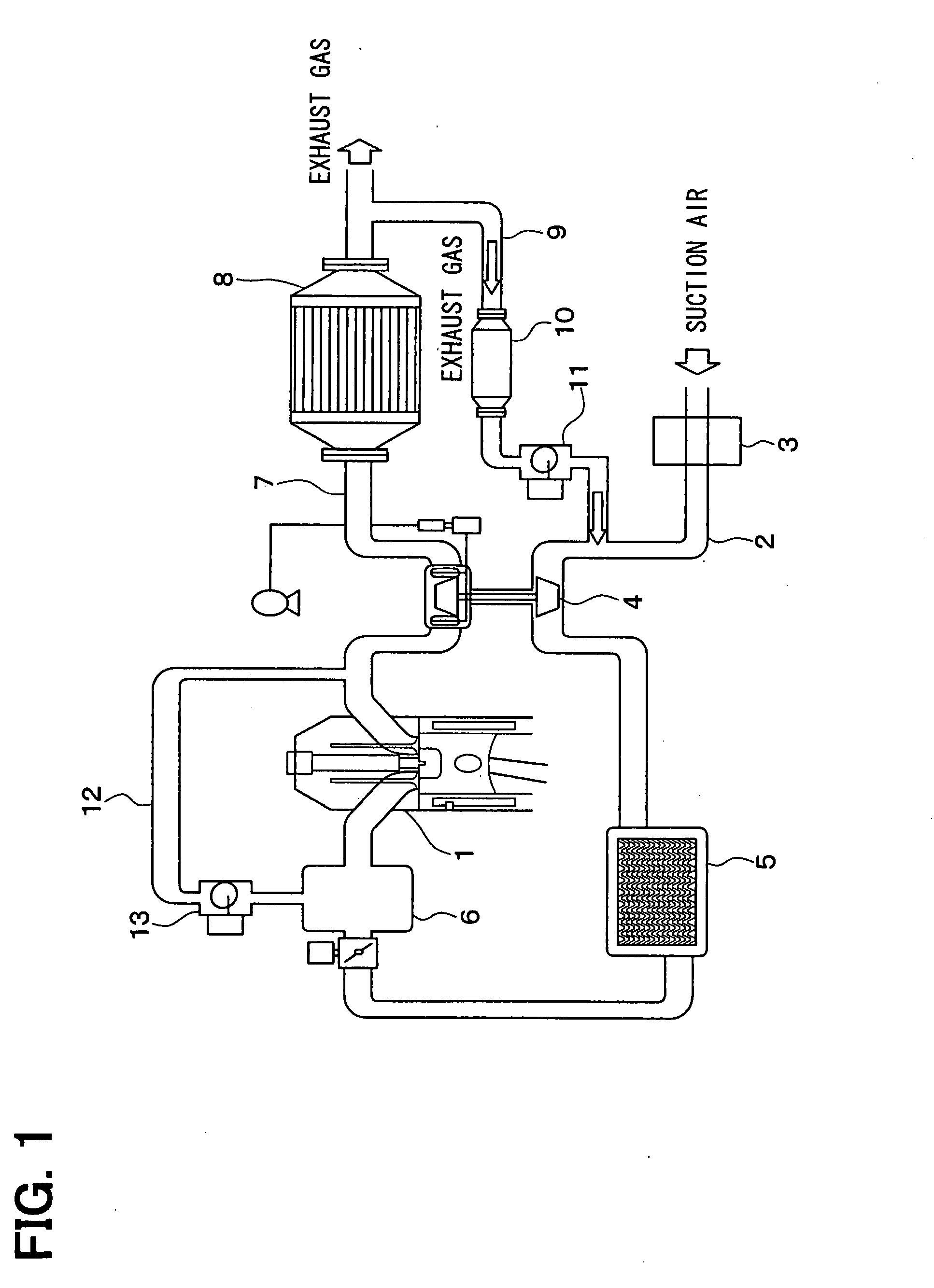

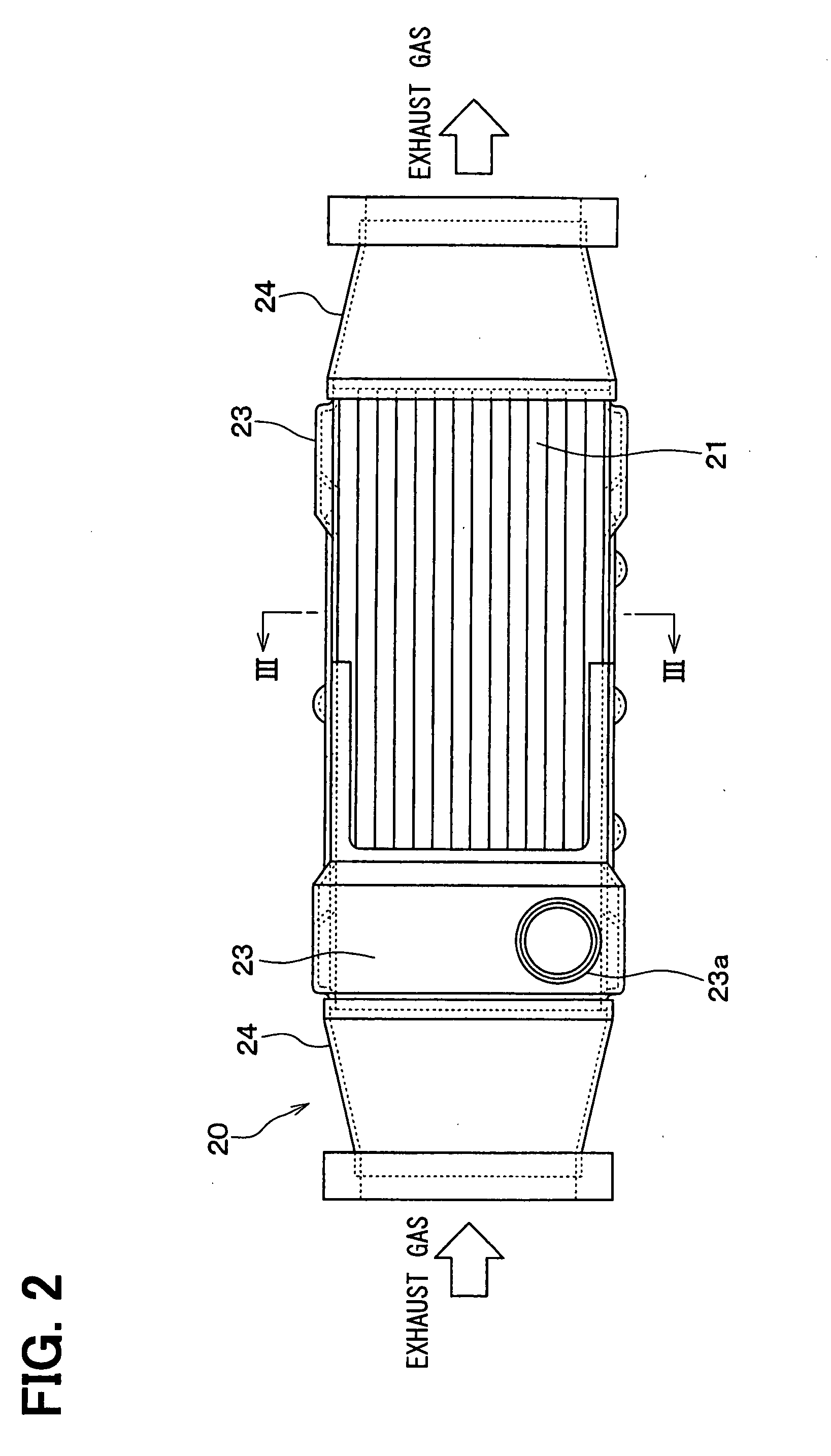

An exhaust gas heat exchanger has a tube which is made of a stainless steel and in which exhaust gas flows, and an inner fin which is made of a stainless steel and arranged in the tube to improve a heat exchange between the exhaust gas and cooling water. The cooling water flows at an outer side of the tube. The fin pitch fp of the inner fin is substantially in the range of 2 mm<fp≦12 mm, and the fin height fh of the inner fin is substantially in the range of 3.5 mm<fh≦12 mm.

Owner:DENSO CORP

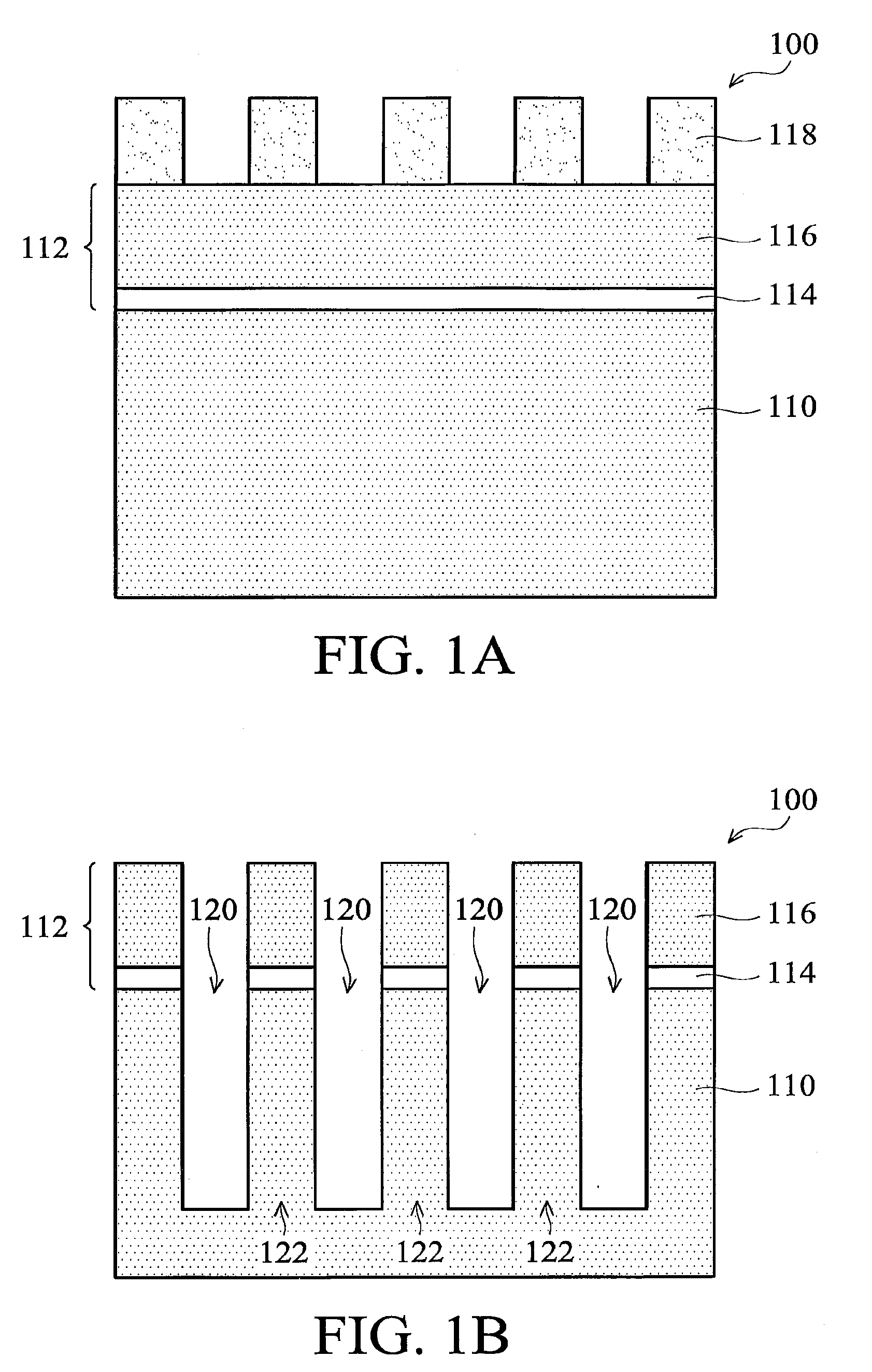

Semiconductor Device Having Multiple Fin Heights

A semiconductor device having multiple fin heights is provided. Multiple fin heights are provided by using multiple masks to recess a dielectric layer within a trench formed in a substrate. In another embodiment, an implant mold or e-beam lithography are utilized to form a pattern of trenches in a photoresist material. Subsequent etching steps form corresponding trenches in the underlying substrate. In yet another embodiment, multiple masking layers are used to etch trenches of different heights separately. A dielectric region may be formed along the bottom of the trenches to isolate the fins by performing an ion implant and a subsequent anneal.

Owner:TAIWAN SEMICON MFG CO LTD

Methods of forming FinFET semiconductor devices with different fin heights

ActiveUS8361894B1Well formedSolid-state devicesSemiconductor/solid-state device manufacturingNitrogenEngineering

One illustrative method disclosed herein includes forming first and second FinFET devices in and above a first region and a second region of a semiconducting substrate, respectively, performing a first ion implantation process through a patterned mask layer to implant nitrogen into the second region, removing the patterned mask layer, performing a second ion implantation process to implant oxygen atoms into both the first and second regions, performing a heating process to form a layer of insulating material at least in the first region and performing at least one etching process to define at least one first fin in the first region and to define at least one second fin in the second region, the second fin being taller than the first fin.

Owner:GLOBALFOUNDRIES INC

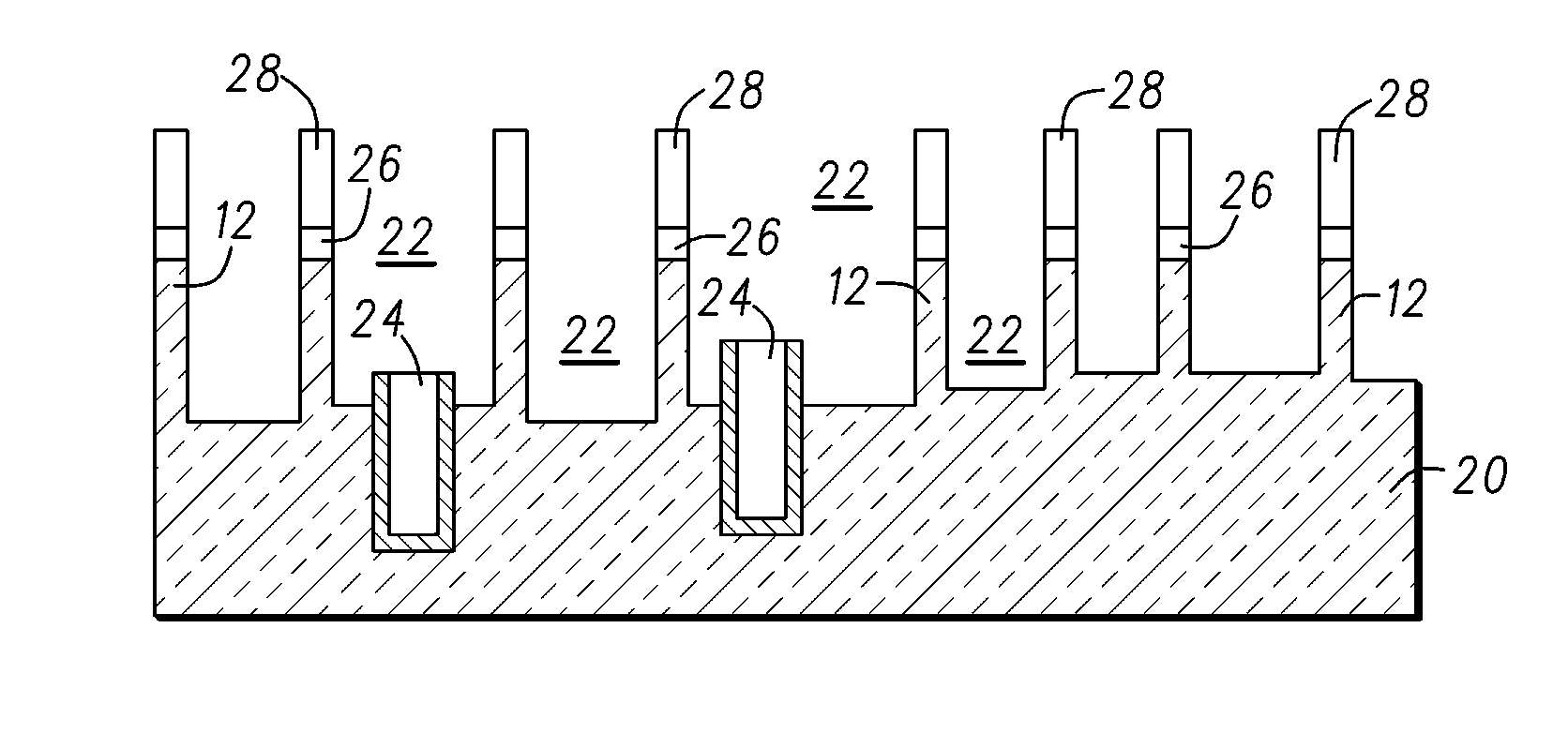

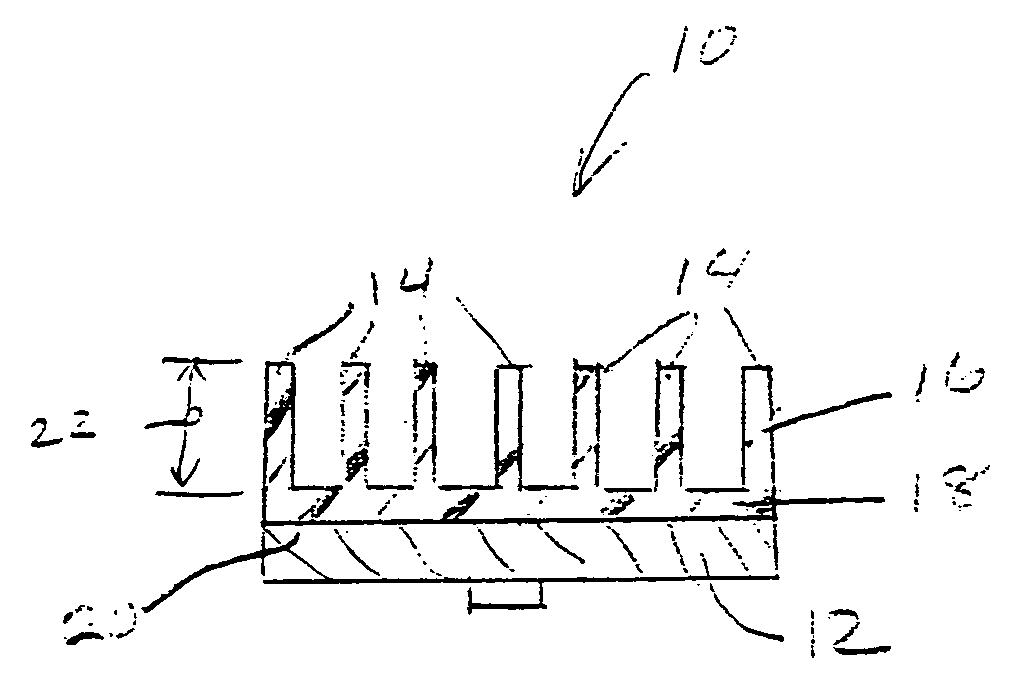

FinFET transistor fabricated in bulk semiconducting material

InactiveUS20070102756A1Uniform and reproducible mannerPromote formationSemiconductor devicesSemiconductor materialsDevice material

A field effect transistor (FET) device structure and method for forming FETs for scaled semiconductor devices. Specifically, FinFET devices are fabricated from bulk semiconductor wafers, as opposed to silicon-on-insulator (SOI) or separation by implantation of oxygen (SIMOX) wafers, in a highly uniform and reproducible manner. The method facilitates formation of FinFET devices from readily-available bulk semiconductor substrates with improved and reproducible fin height control while providing isolation between source and drain regions of the FinFET device.

Owner:ATMEL CORP

Methods of controlling fin height of FinFET devices by performing a directional deposition process

InactiveUS8354320B1Semiconductor/solid-state device manufacturingSemiconductor devicesEngineeringDeposition process

One illustrative method disclosed herein includes a forming plurality of trenches in a substrate to thereby define a fin structure for a FinFET device, forming a first region of a first insulating material within each of the trenches, wherein the as-deposited surface of the first insulating material is positioned below an upper surface of the fin, forming a layer of a second material that contacts the as-deposited surface of the first region of the first insulating material and overfills the trenches, performing at least one process operation to remove at least a portion of the layer of the second material from above the fin structure, and, after performing the at least one process operation, performing a second process operation to selectively remove the second material from above the first region of the first insulating material and thereby expose the as-deposited surface of the first region of the first insulating material.

Owner:GLOBALFOUNDRIES INC

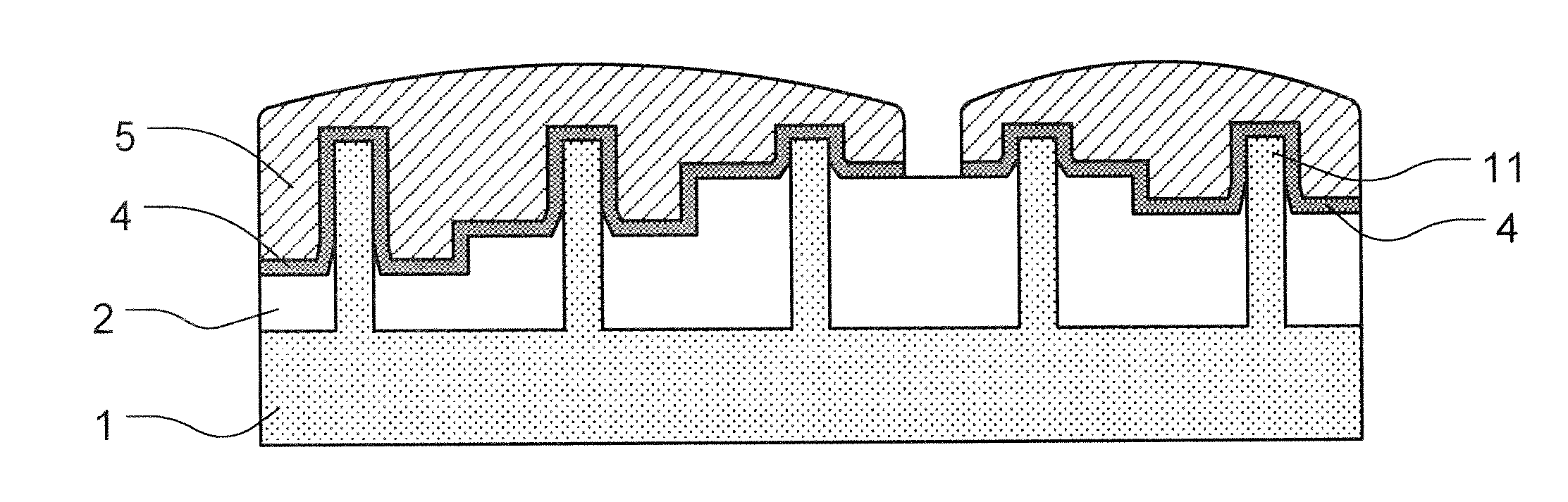

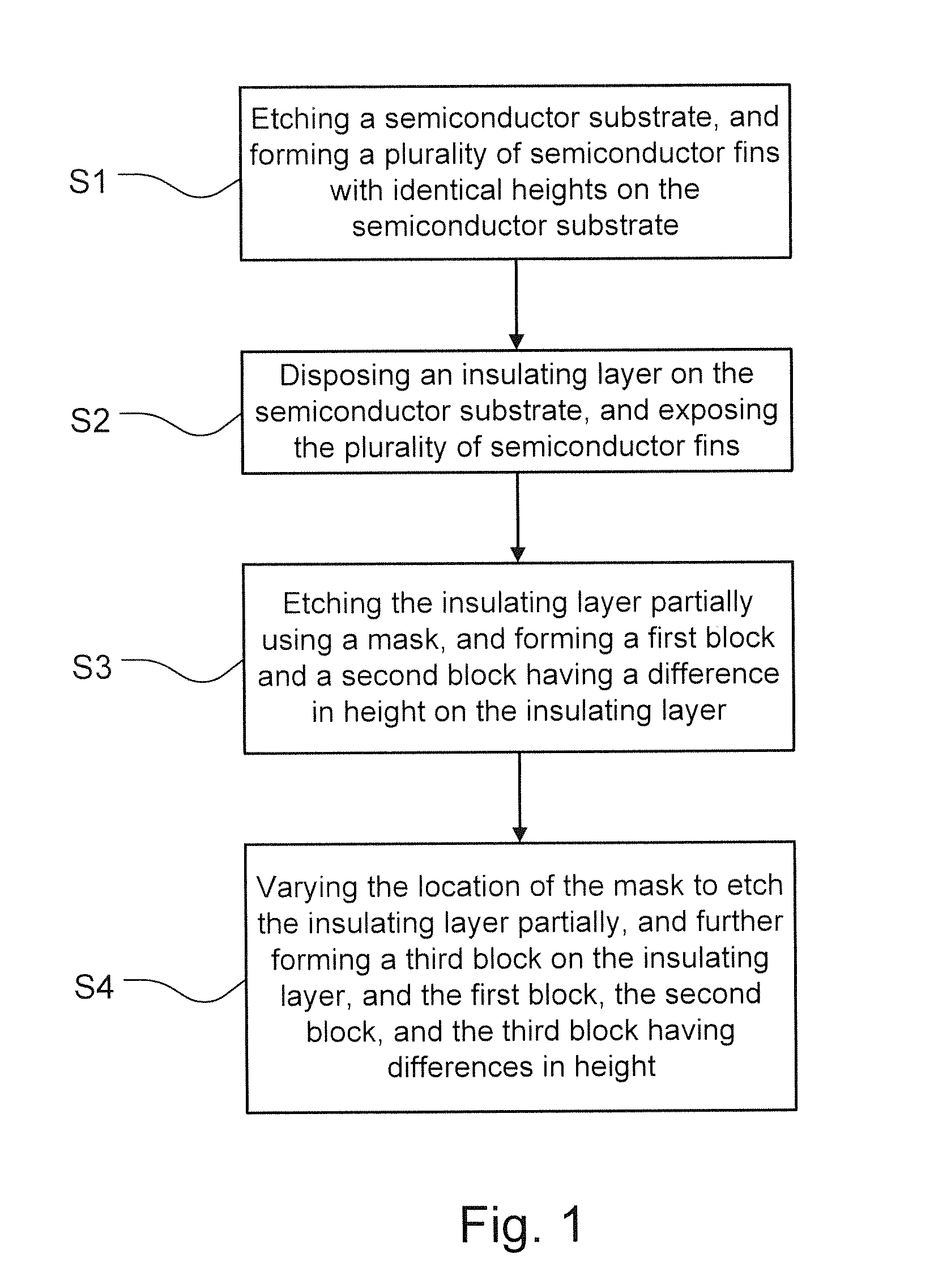

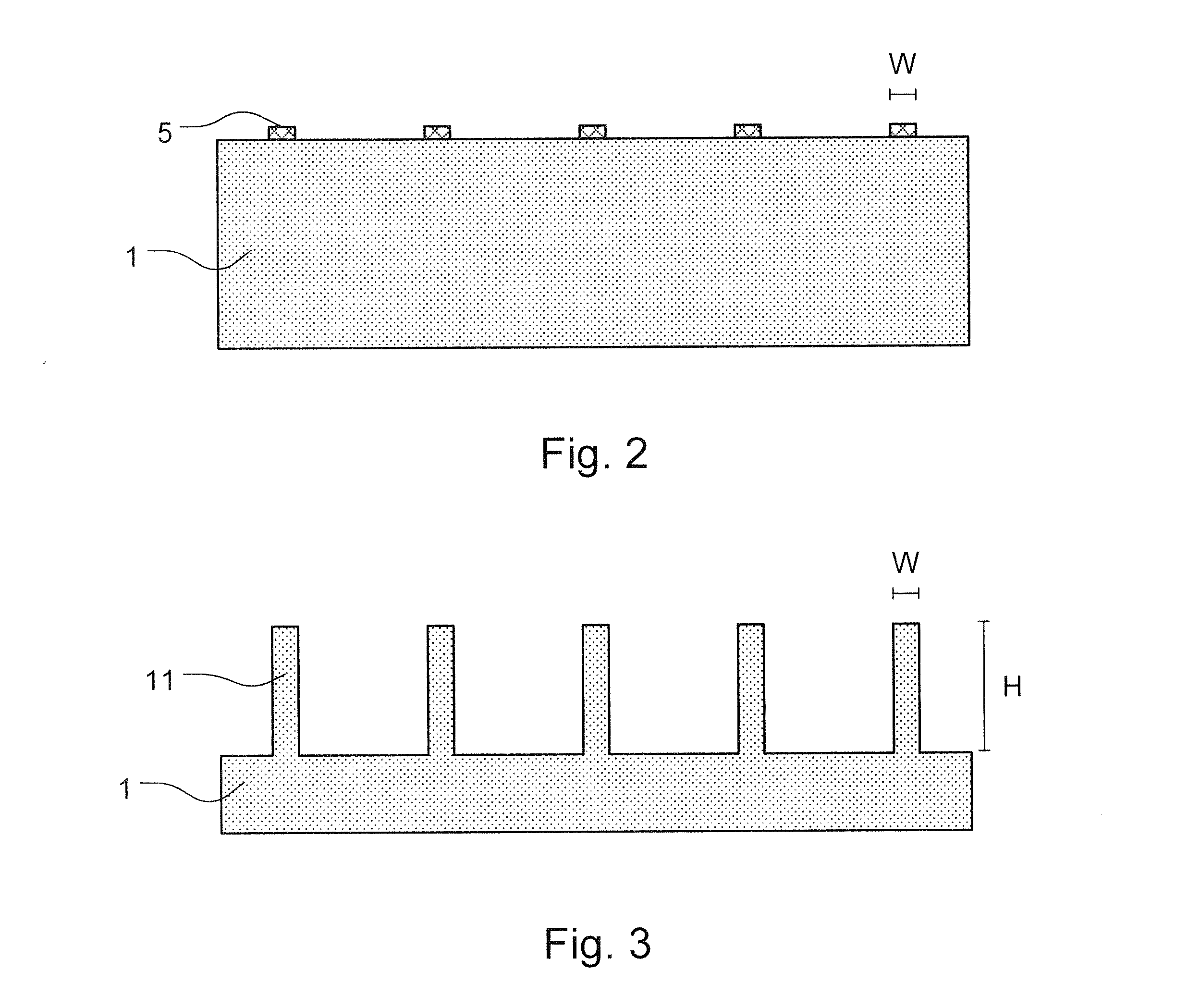

STRUCTURE OF FinFETs

InactiveUS20150145068A1Improving width quantization effectMany choicesTransistorSolid-state devicesEngineeringFin height

The present invention relates to a method for fabricating FinFETs and the structure thereof. The present invention uses an additional mask to define regions forming semiconductor fins having high semiconductor-fin height. By making use of multiple etching processes of the insulating layer, structures with differences in the height of semiconductor fins are achieved. The method can be combined with current process for semiconductor-based FinFETs for overcoming effectively the problem of electron-channel-width quantization effect as well as improving the performance of FinFETs.

Owner:NAT APPLIED RES LAB

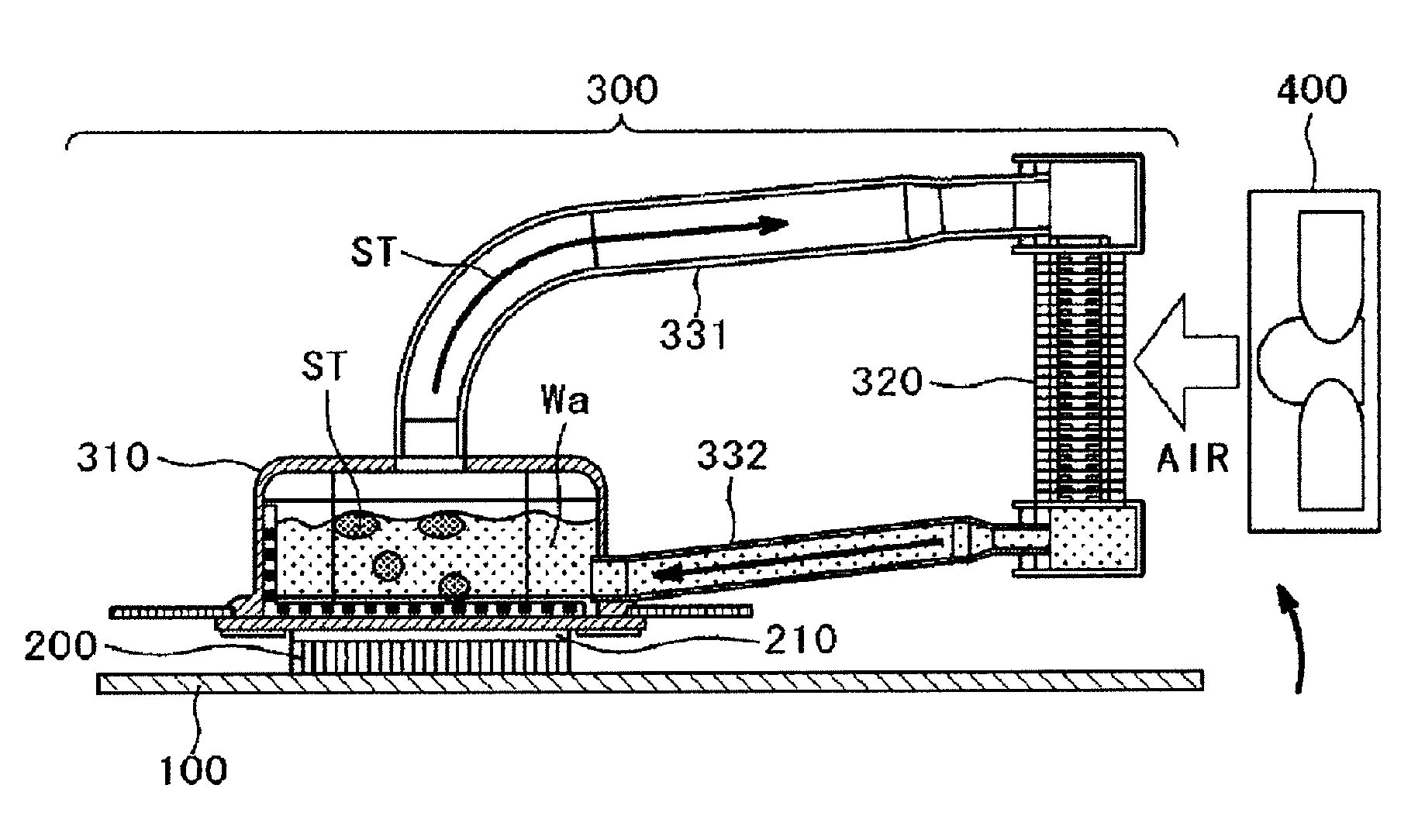

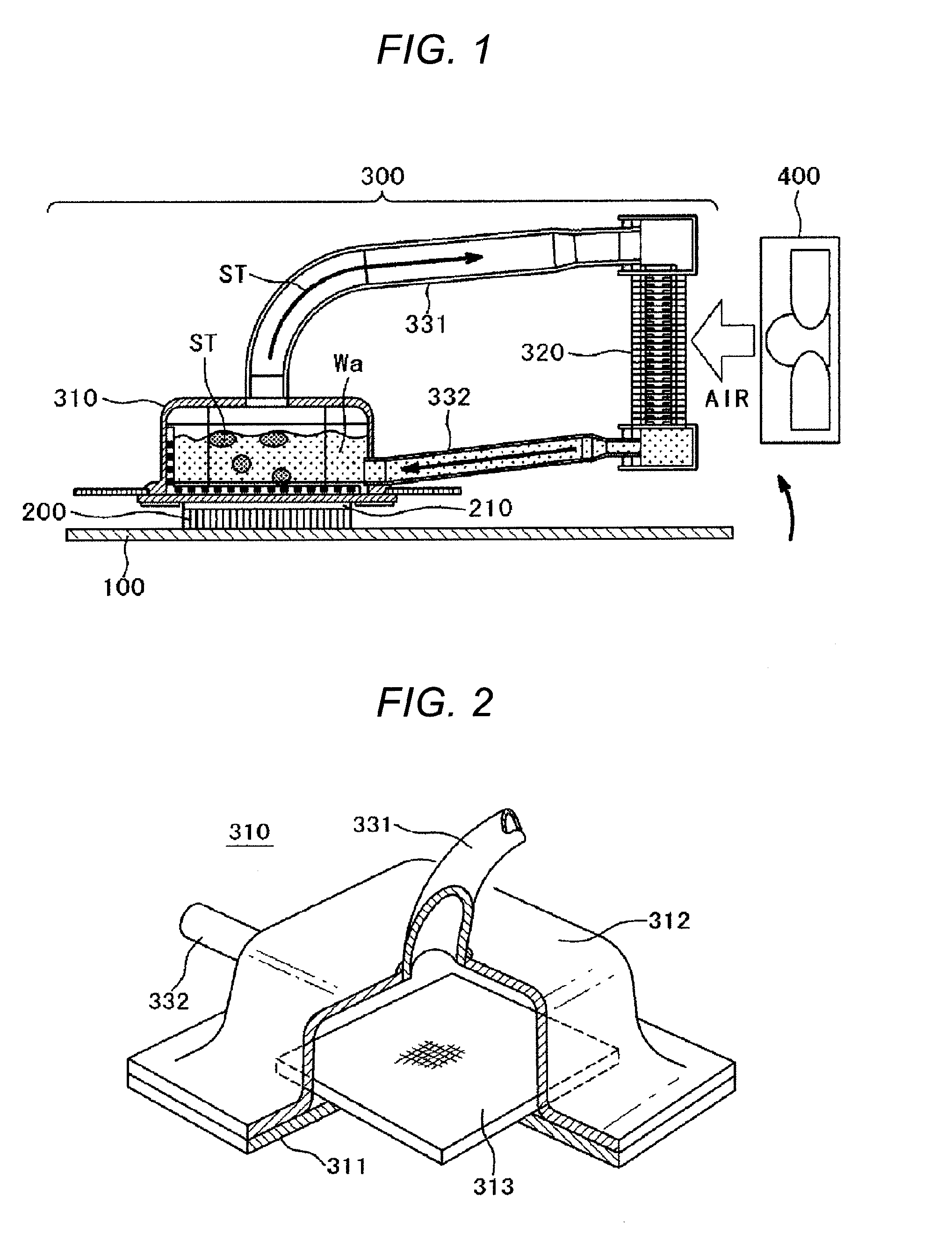

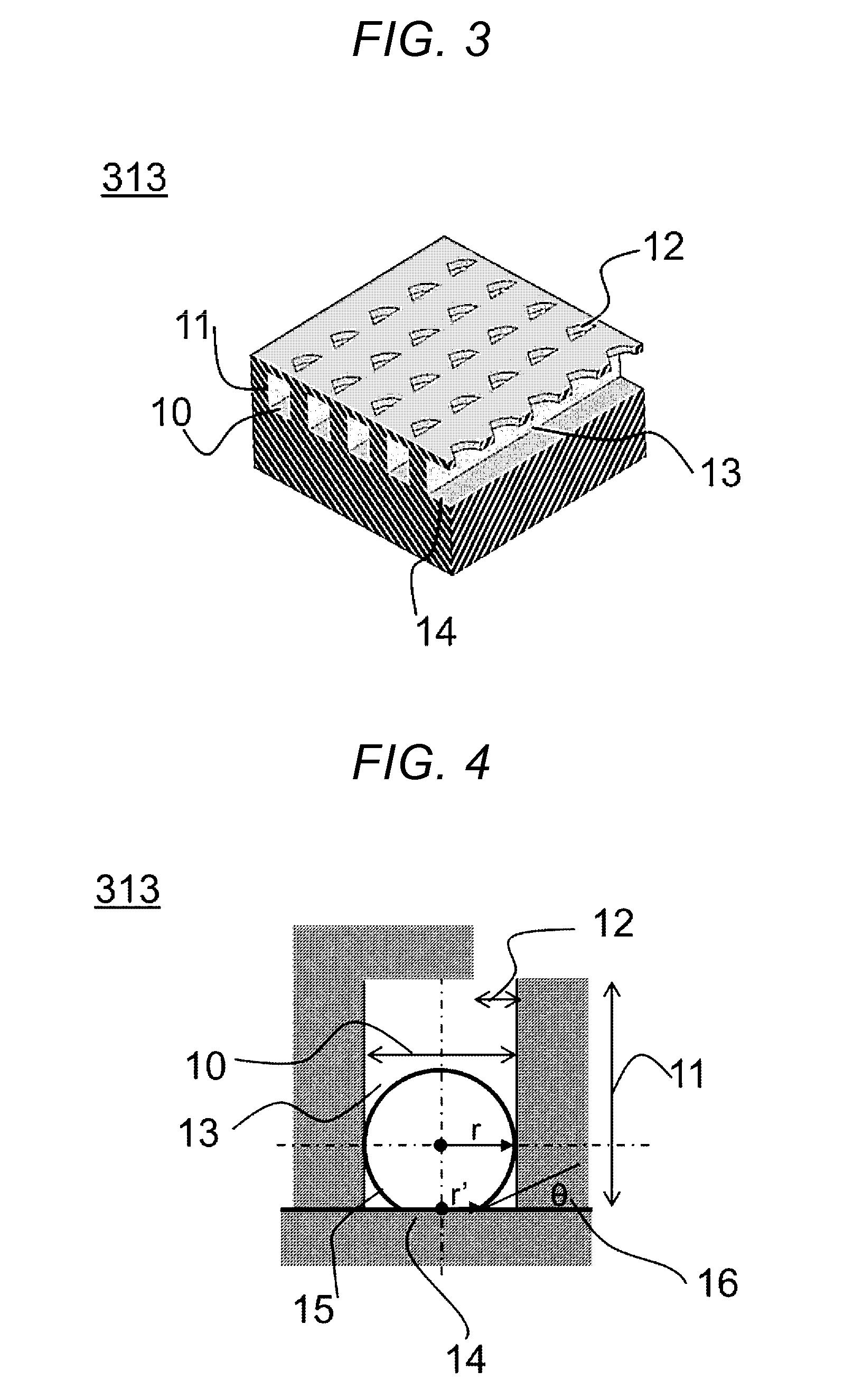

Cooling system and electronic apparatus using the same

InactiveUS20140090814A1Improve heat transfer performanceGenerated heat is relatively largeSemiconductor/solid-state device detailsSolid-state devicesEngineeringBoiling heat transfer

The invention relates to a cooling system and an electronic apparatus using the same, and particularly aims to use a thermosiphon as the cooling system and derives an optimum shape (inter-fin gap, fin height, and fin upper-end hole diameter) of a boiling heat transfer surface for different coolants. In a cooling system using a thermosiphon according to the invention, an optimum shape (inter-fin gap, fin height, and fin upper-end hole diameter) of a boiling heat transfer surface of a heat receiving jacket that forms the cooling system is identified based on a critical radius of a steam bubble produced in an overheated liquid and the diameter of an air bubble departing from the heat transfer surface for a variety of coolants.

Owner:HITACHI LTD

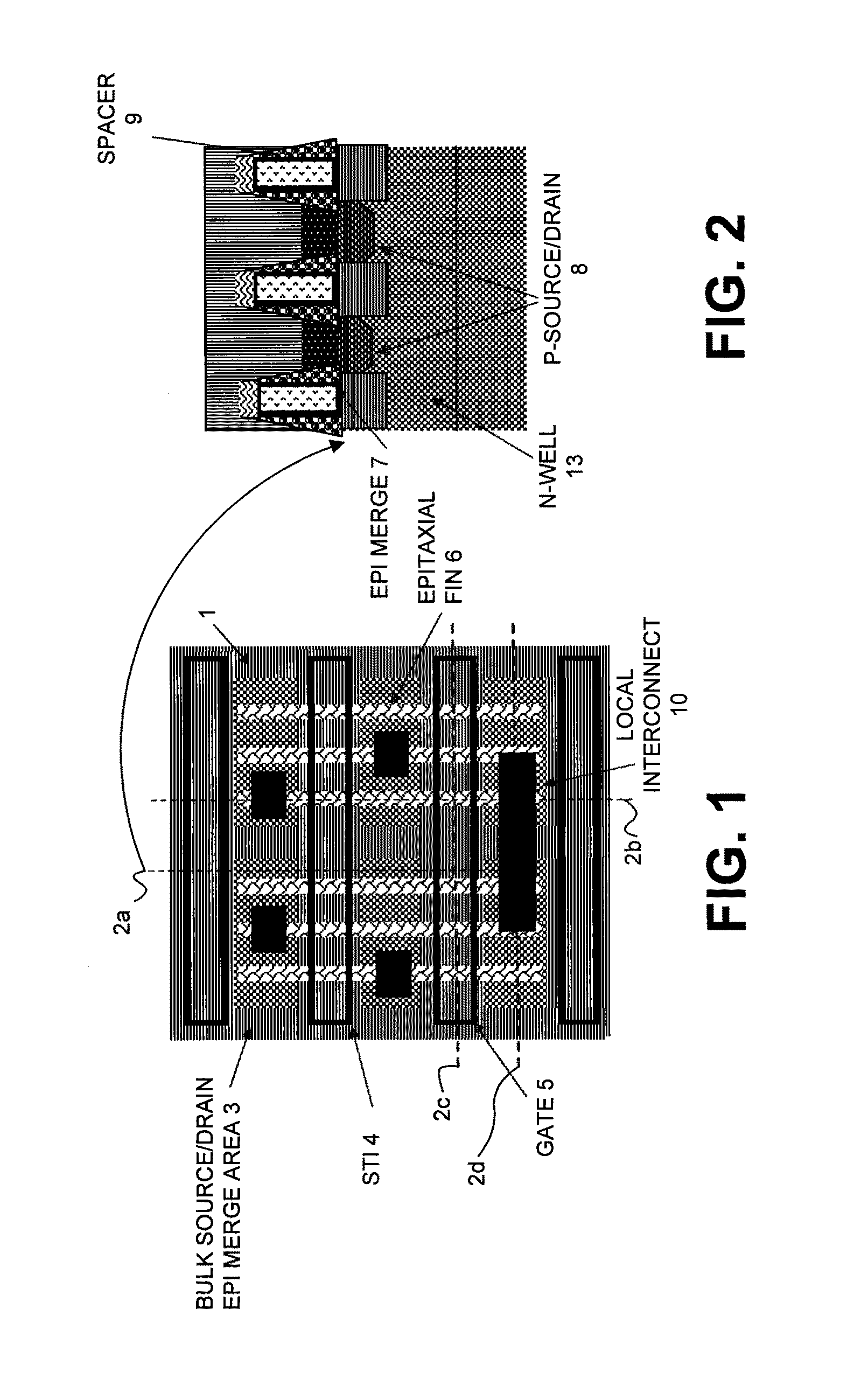

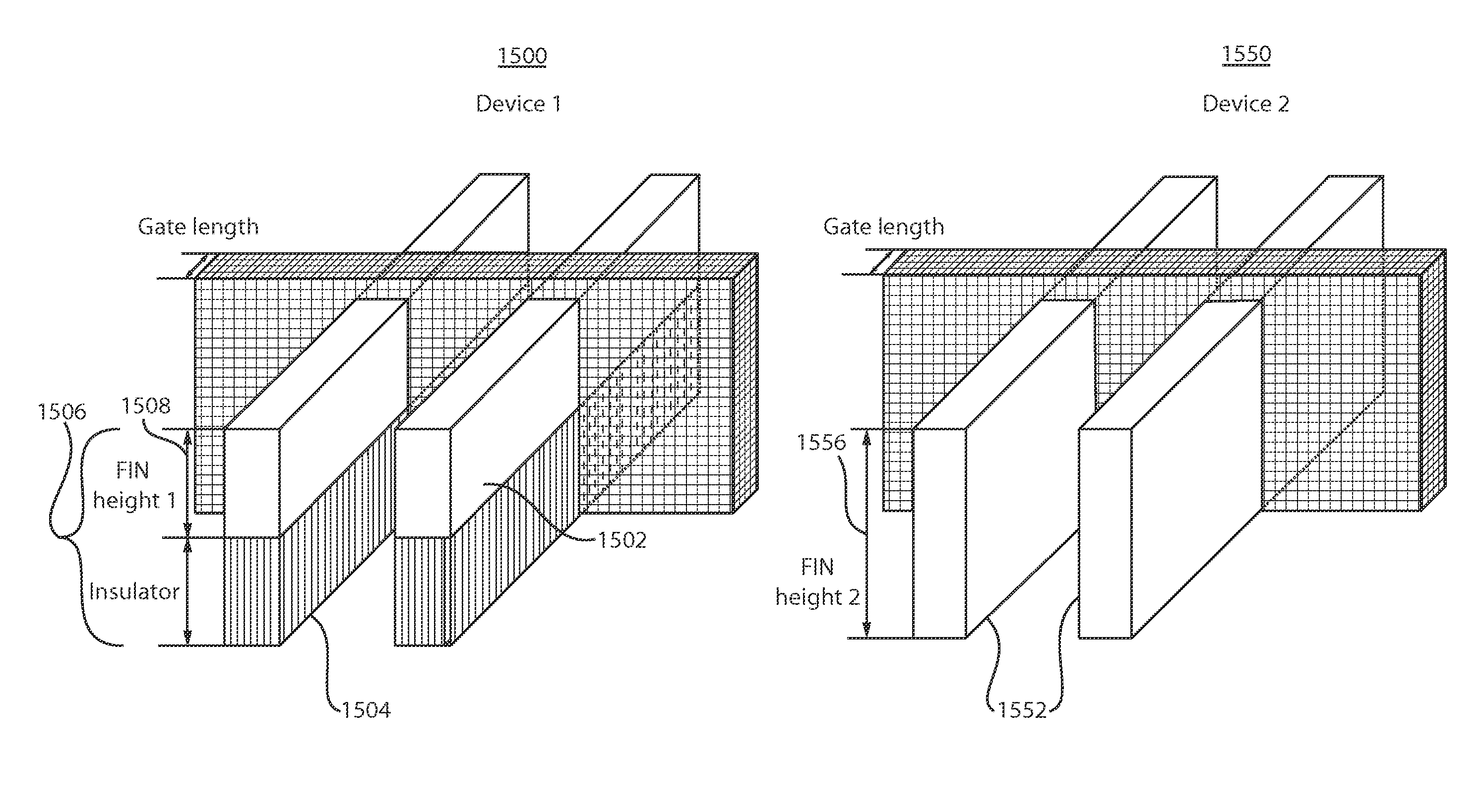

System and method of manufacturing a fin field-effect transistor having multiple fin heights

ActiveUS20150162404A1Easy to controlHigh aspect ratioTransistorLiquid surface applicatorsEngineeringField-effect transistor

An apparatus comprises a first fin field effect transistor (FinFET) device extending from a surface of a first etch stop layer. The apparatus also comprises a second FinFET device extending from a surface of a second etch stop layer. A first compound layer is interposed between the first etch stop layer and the second etch stop layer.

Owner:QUALCOMM INC

Multi-gate field-effect transistors with variable fin heights

Owner:GLOBALFOUNDRIES INC

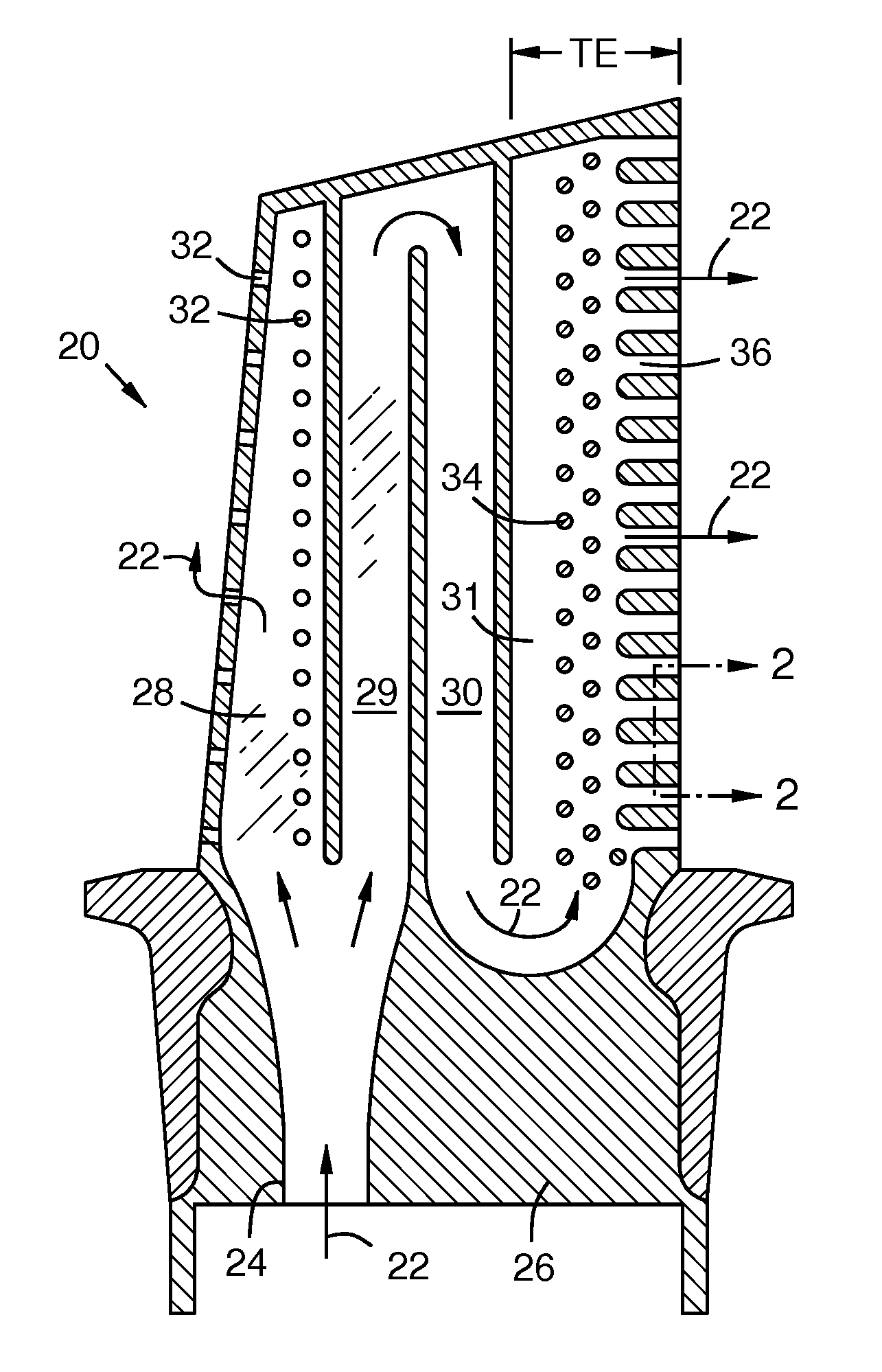

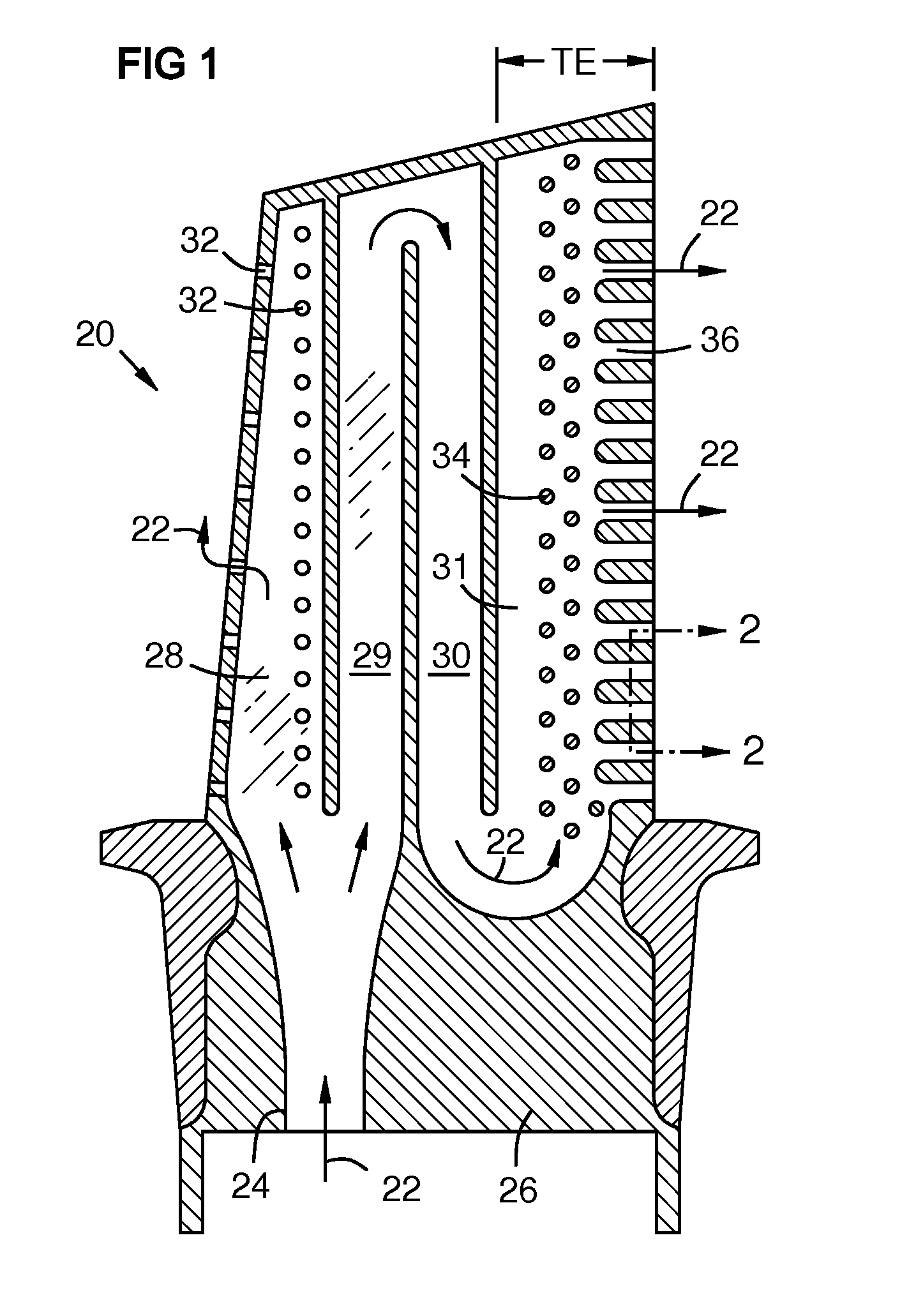

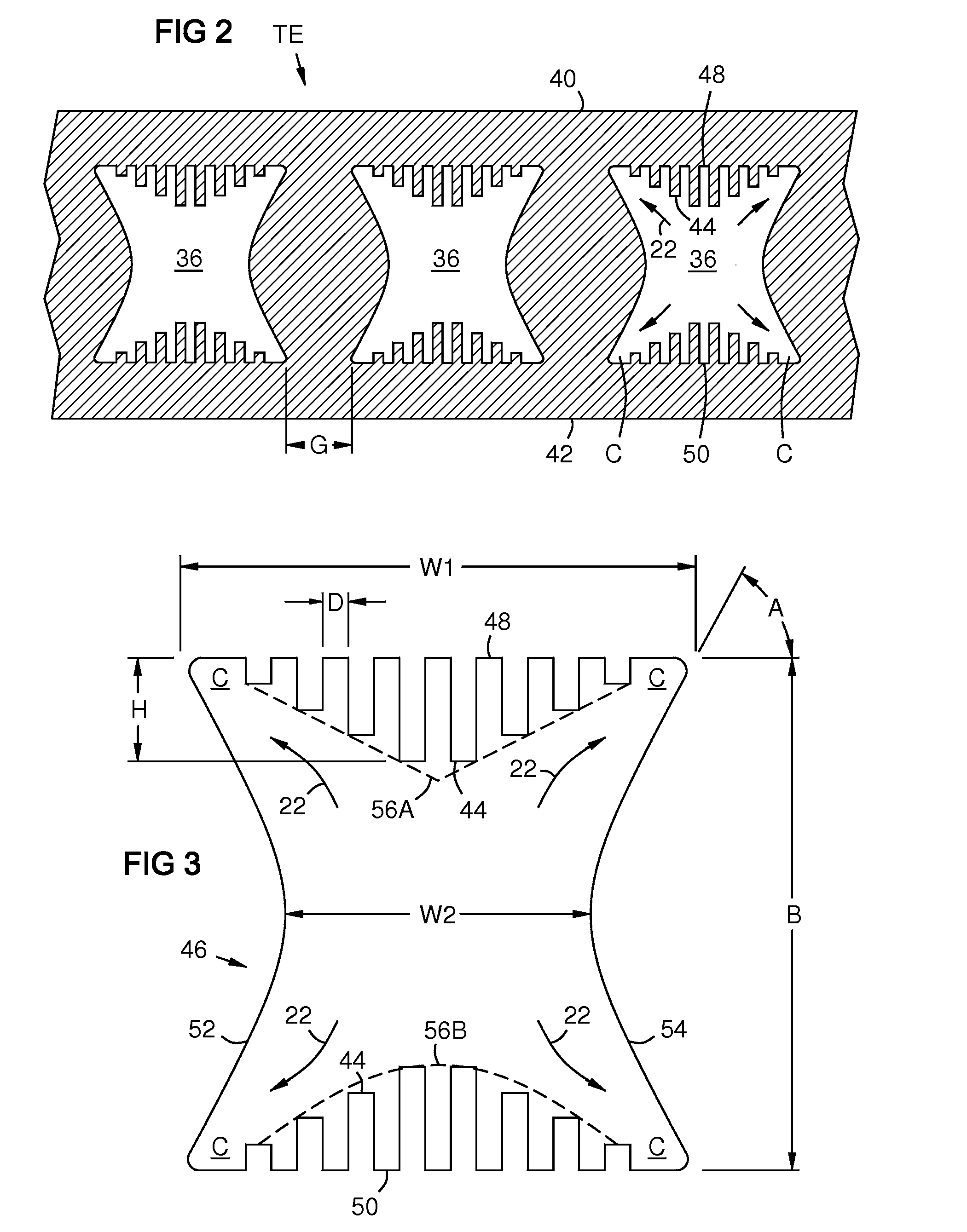

Component cooling channel

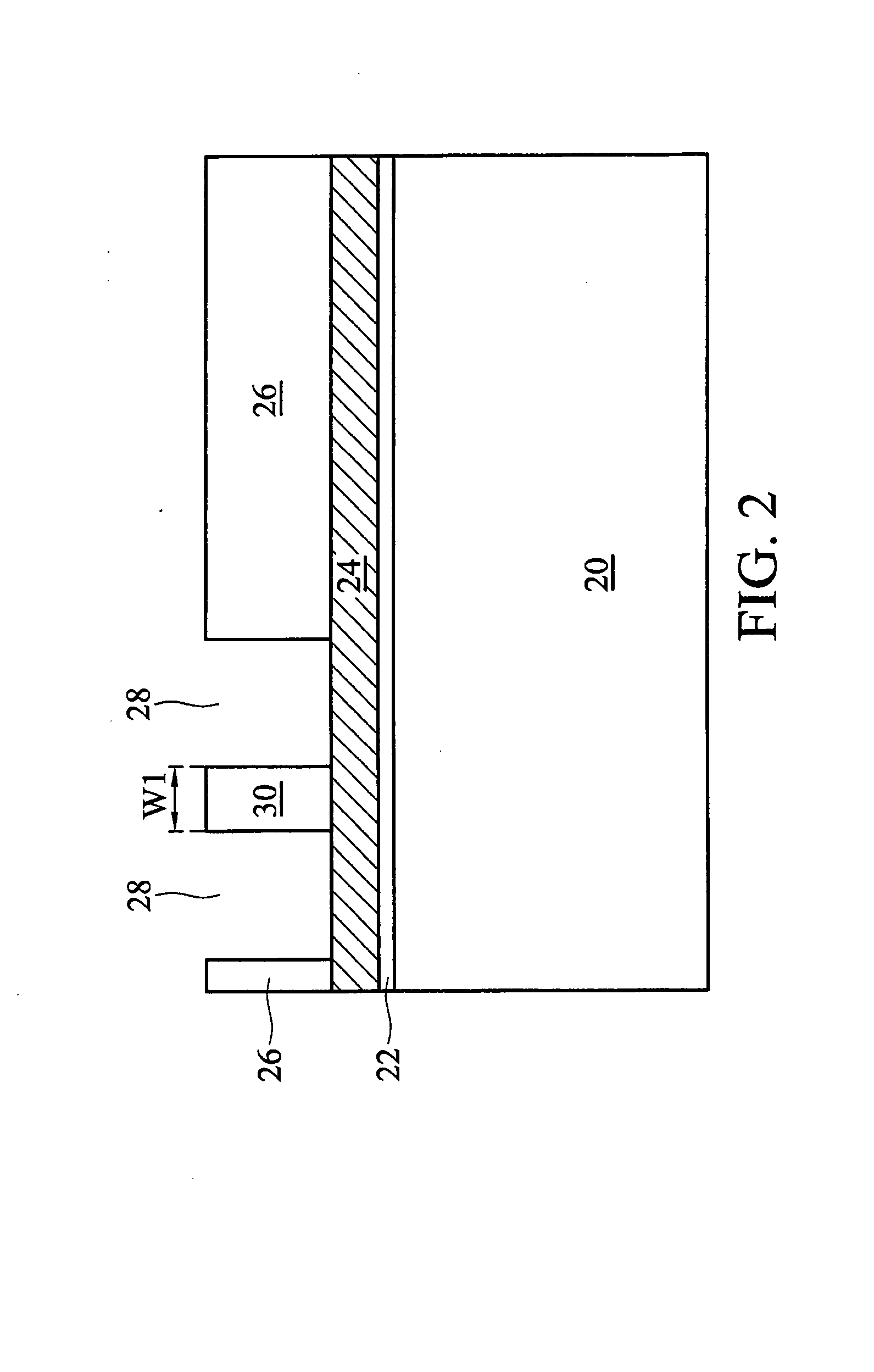

A cooling channel (36, 36B) cools an exterior surface (40 or 42) or two opposed exterior surfaces (40 and 42). The channel has a near-wall inner surface (48, 50) with a width (W1). Interior side surfaces (52, 54) may converge to a reduced channel width (W2). The near-wall inner surface (48, 50) may have fins (44) aligned with a coolant flow (22). The fins may highest at mid-width of the near-wall inner surface. A two-sided cooling channel (36) may have two near-wall inner surfaces (48, 50) parallel to two respective exterior surfaces (40, 42), and may have an hourglass shaped transverse sectional profile. The tapered channel width (W1, W2) and the fin height profile (56A, 56B) increases cooling flow (22) into the corners (C) of the channel for more uniform and efficient cooling.

Owner:MIKRO SYSYTEMS INC +1

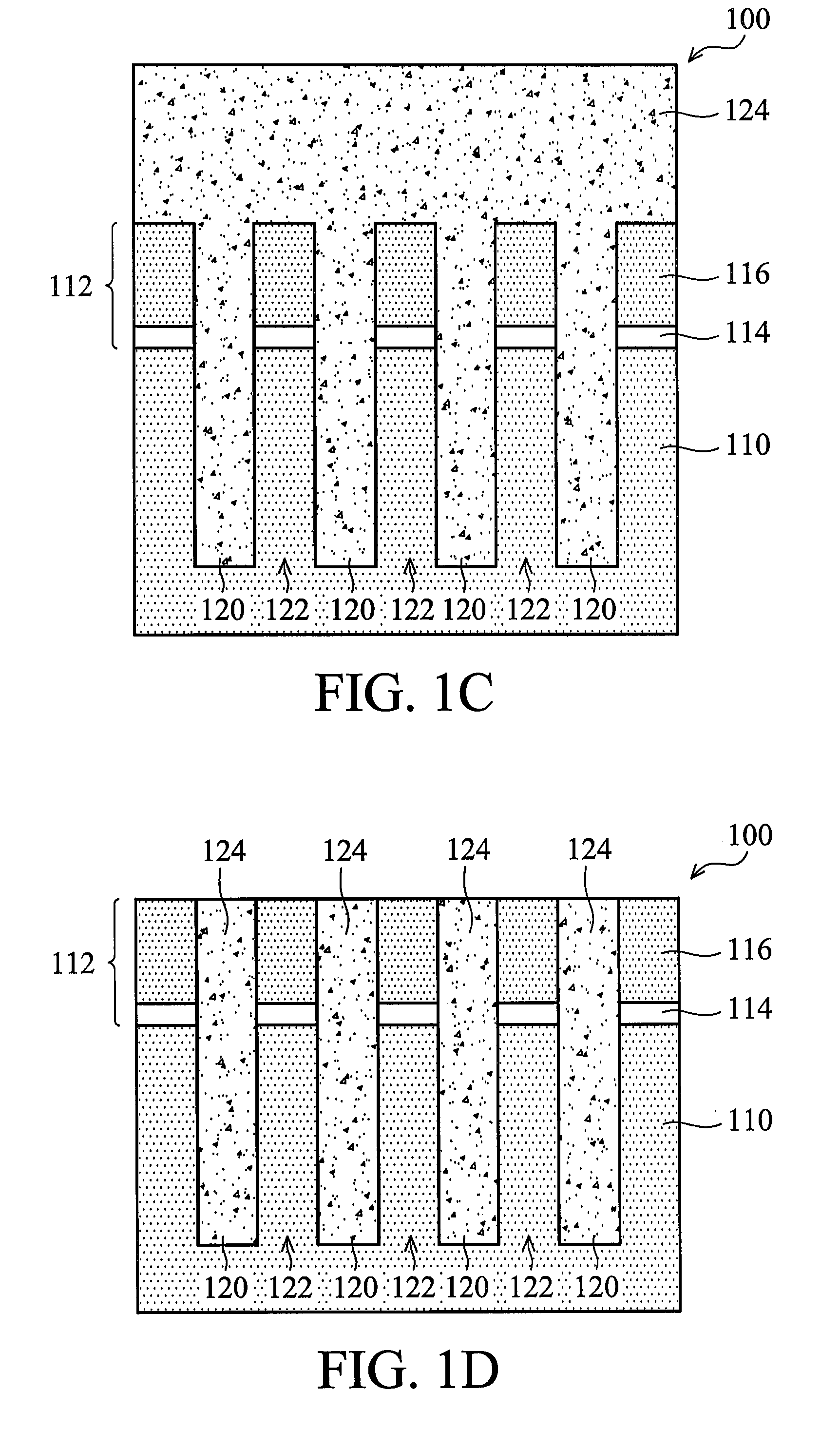

Methods of forming bulk finfet semiconductor devices by performing a liner recessing process to define fin heights and finfet devices with such a recessed liner

ActiveUS20140159171A1Well formedSemiconductor/solid-state device manufacturingSemiconductor devicesFin heightSemiconductor

One method disclosed herein includes forming a conformal liner layer in a plurality of trenches that define a fin, forming a layer of insulating material above the liner layer, exposing portions of the liner layer, removing portions of the liner layer so as to result in a generally U-shaped liner positioned at a bottom of each of the trenches, performing at least one third etching process on the layer of insulating material, wherein at least a portion of the layer of insulating material is positioned within a cavity of the U-shaped liner layer, and forming a gate structure around the fin. A FinFET device disclosed herein includes a plurality of trenches that define a fin, a local isolation that includes a generally U-shaped liner that defines, in part, a cavity and a layer of insulating material positioned within the cavity, and a gate structure positioned around the fin.

Owner:GLOBALFOUNDRIES US INC +1