Integrated circuit structure

An integrated circuit and substrate technology, applied in the field of fin field effect transistors, can solve the problems of increasing effective source/drain resistance, increasing current congestion, etc., and achieve the effect of increasing distance and reducing current congestion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0048] The present invention provides a novel fin field-effect transistor (FinFET) and its forming method, and discusses the differences of various embodiments. In all the different views and illustrated embodiments, the same reference numerals are used to designate the same elements.

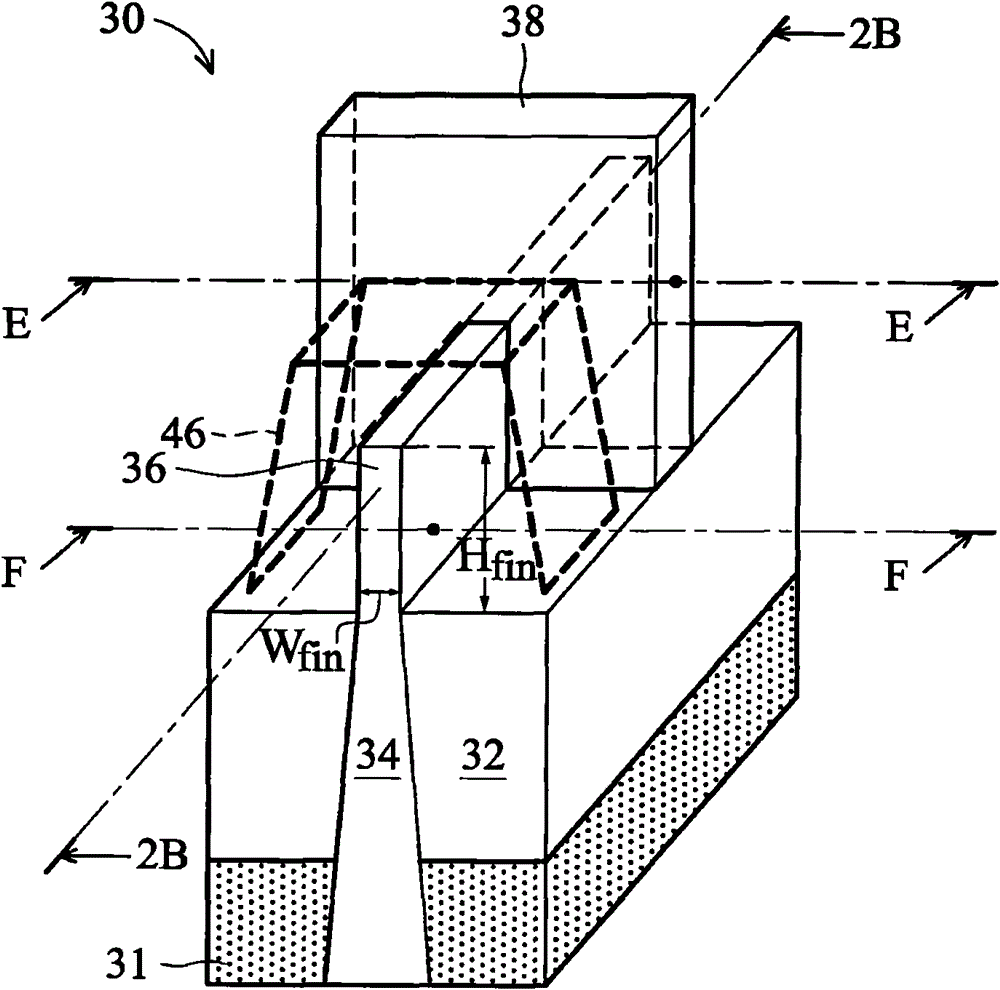

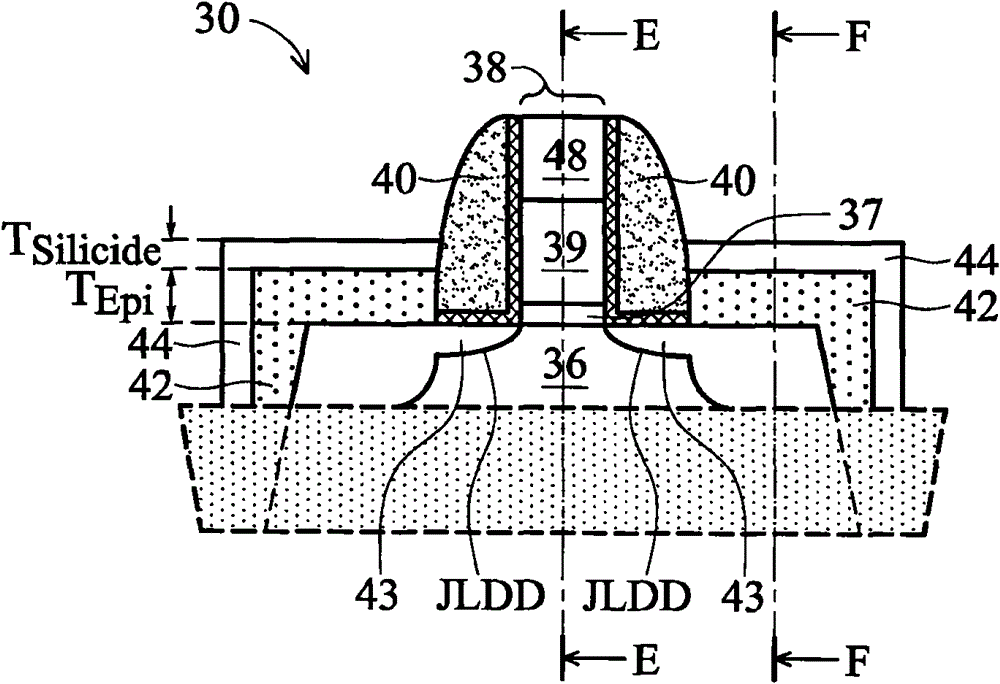

[0049] Figure 2A A perspective view of a fin field effect transistor (FinFET) 30 including a fin 36 and a gate stack 38 on the upper surface and sidewalls of the fin 36 is disclosed. For simplicity, the gate spacer 40, the epitaxial layer 42 (which is a semiconductor layer) and the metal silicide layer 44 (not shown in the Figure 2A in, see Figure 2B ). However, the interface between the epitaxial layer 42 and the metal suicide layer 44 is schematically shown by dashed line 46 . The width of the fin 36 is denoted as W fin , while the height of the fin 36 is denoted as H fin .

[0050] Fin 36 may directly overlie semiconductor strip 34 and may form a continuous region with semiconducto...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More