Electric test structure and method for measuring epitaxial graphic offset

A technology of testing structure and offset, which is applied in the field of epitaxy, can solve the problems of inaccurate compensation of epitaxy pattern offset and inability to effectively control registration errors, etc., and achieve the effect of reducing registration errors and high measurement accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] In order to illustrate the technical content, structural features, achieved goals and effects of the present invention in detail, the following will be described in detail in conjunction with the embodiments and accompanying drawings.

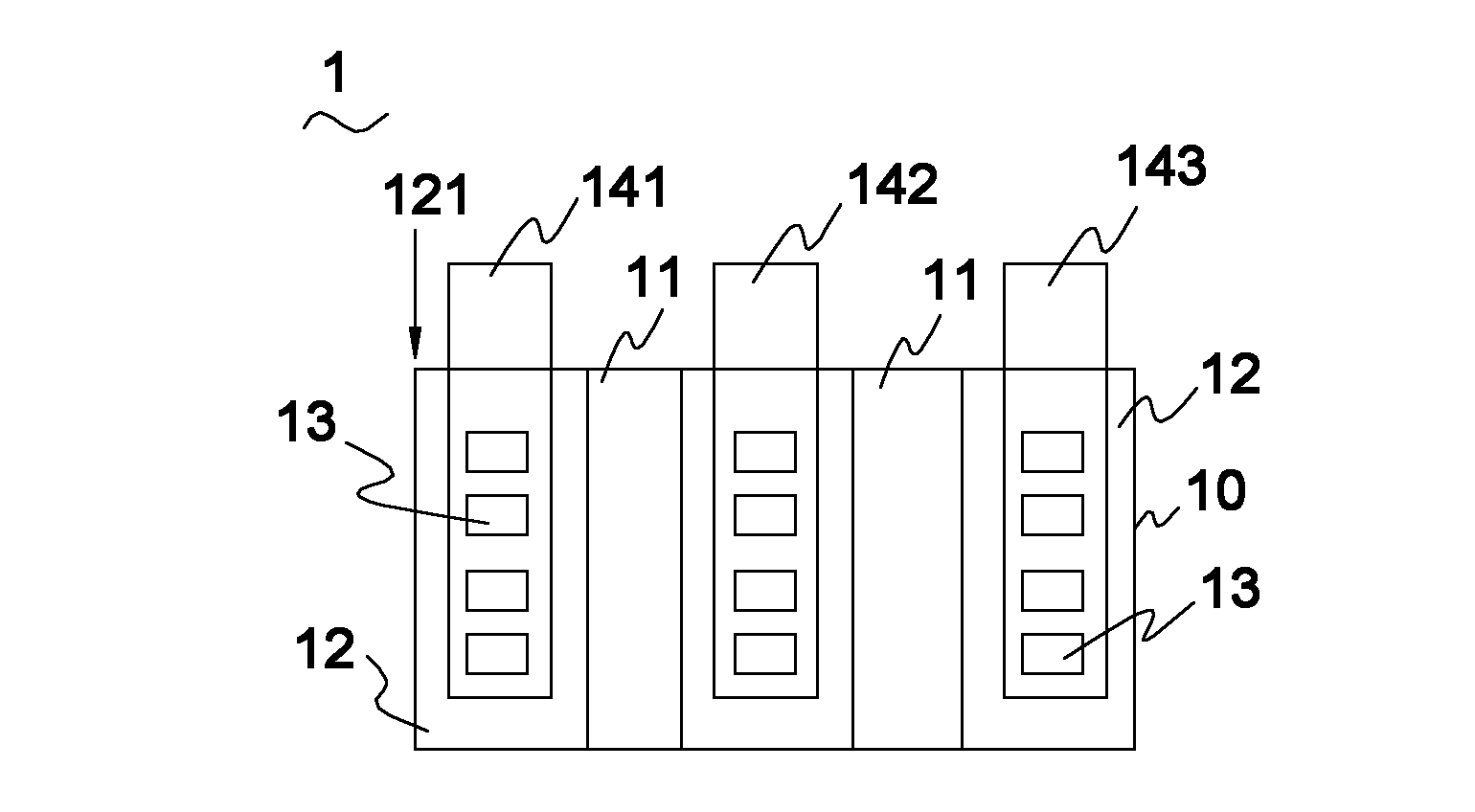

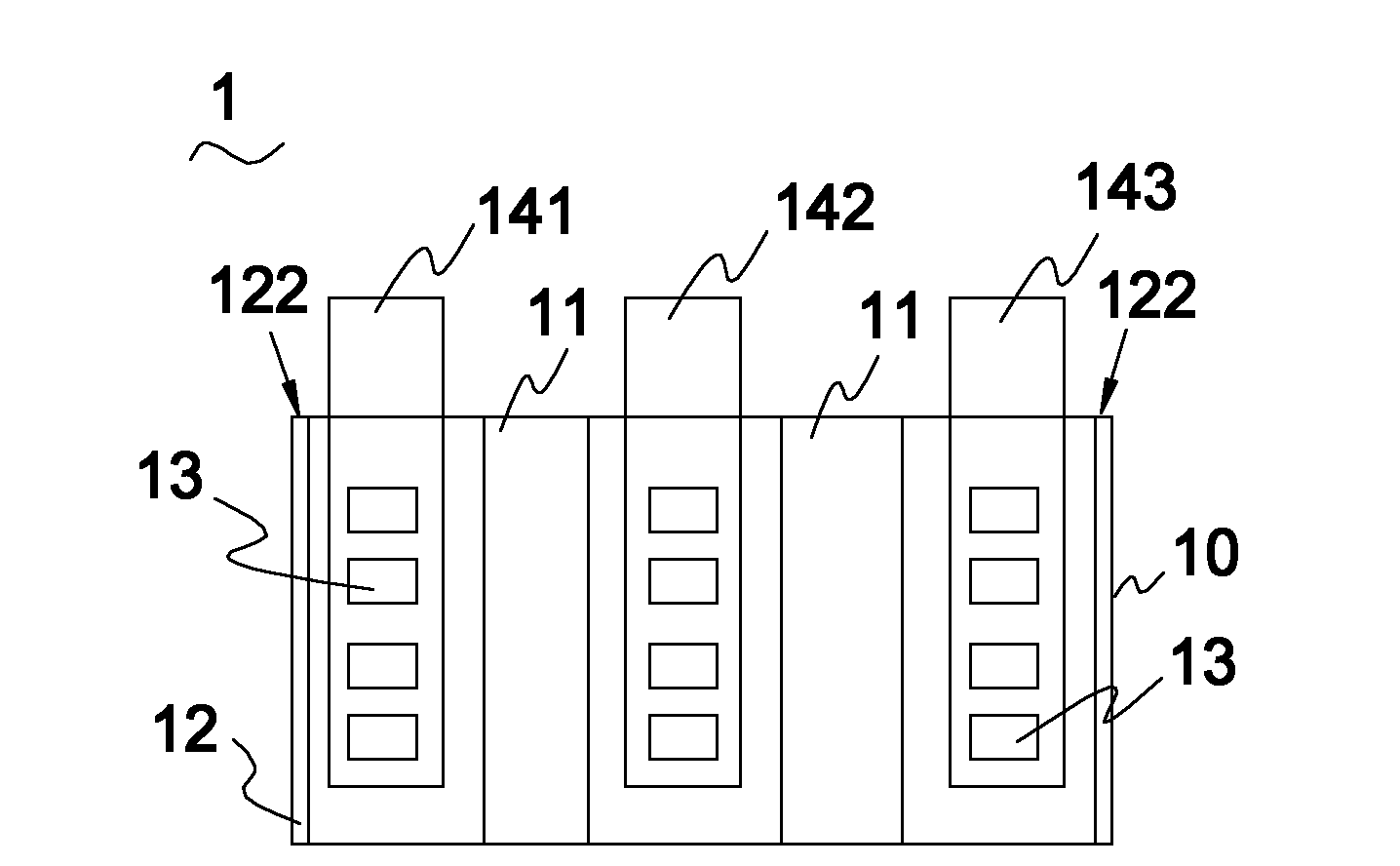

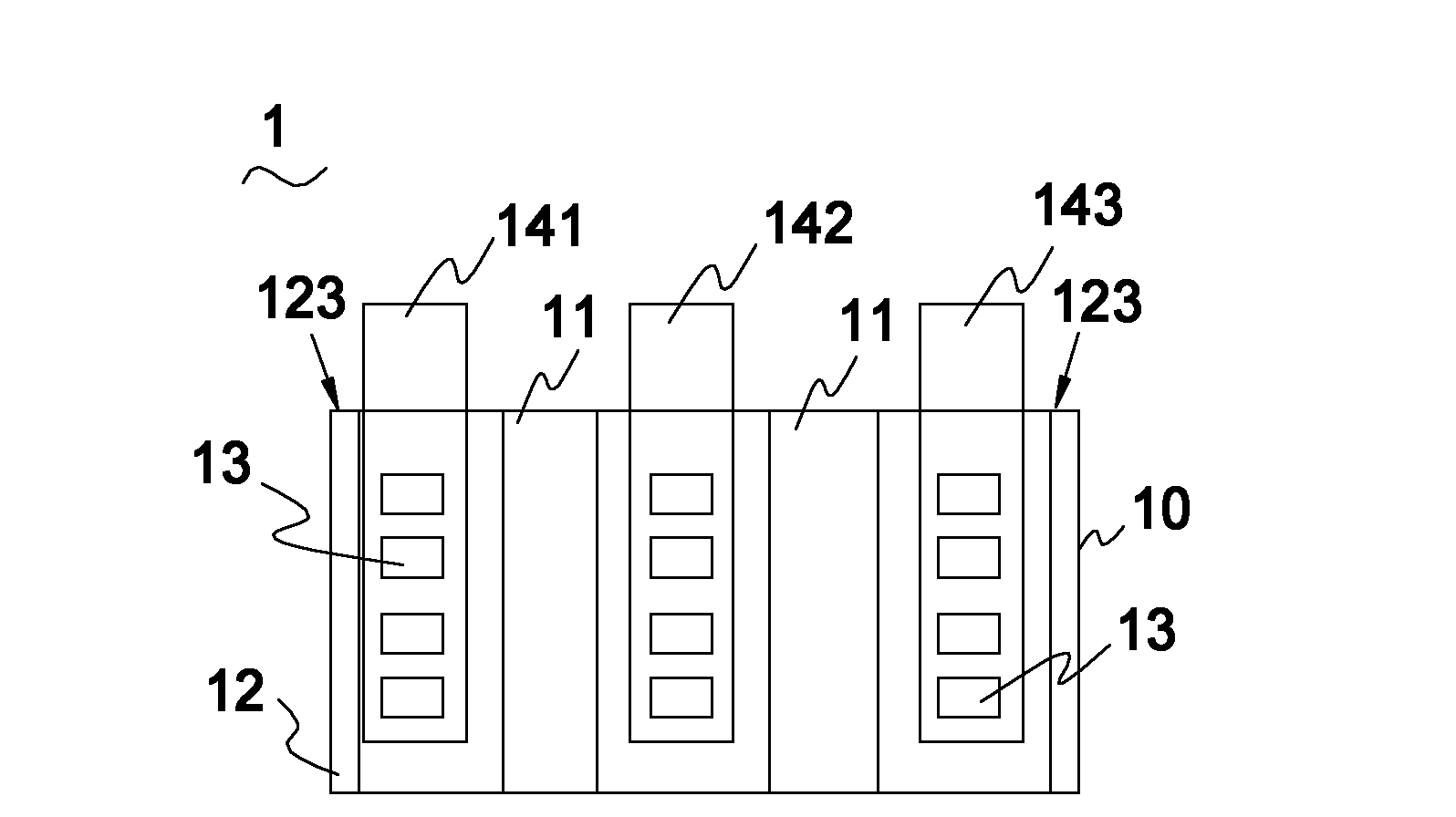

[0034] see Figure 1 to Figure 10 , Figure 1 to Figure 10 Shown is a schematic diagram of an electrical test structure 1 for measuring epitaxial pattern offset. The electrical test structure 1 includes diffusion of ions of the second conductivity type on the surface of a semiconductor substrate (not shown) having ions of the first conductivity type, so as to form buried ions of the second conductivity type on the surface of the semiconductor substrate. Layer 10. An epitaxial layer 11 having ions of the second conductivity type is epitaxially formed on the surface of the semiconductor substrate having the buried layer 10 . The buried layer 10 is located between the semiconductor substrate and the epitaxial layer 11 .

[0035] A plura...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More