High-speed full-difference clock duty cycle calibration circuit

一种校准电路、占空比的技术,应用在电气元件、产生电脉冲、脉冲处理等方向,能够解决不获得校准结果、校准精度离散性、工作的速度不能太高等问题,达到提高速度、可工作频率高、工作频率范围宽的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The present invention will be described in detail below in conjunction with the accompanying drawings and specific examples.

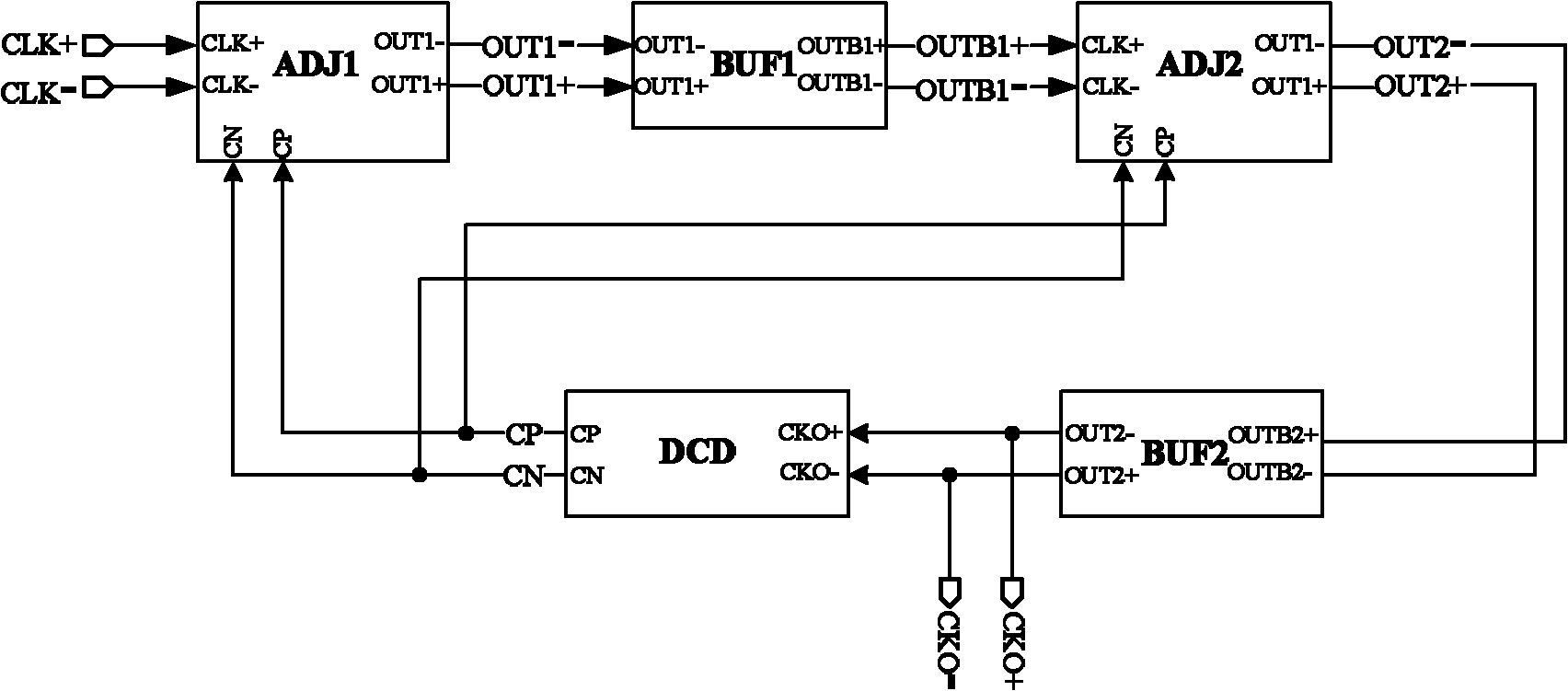

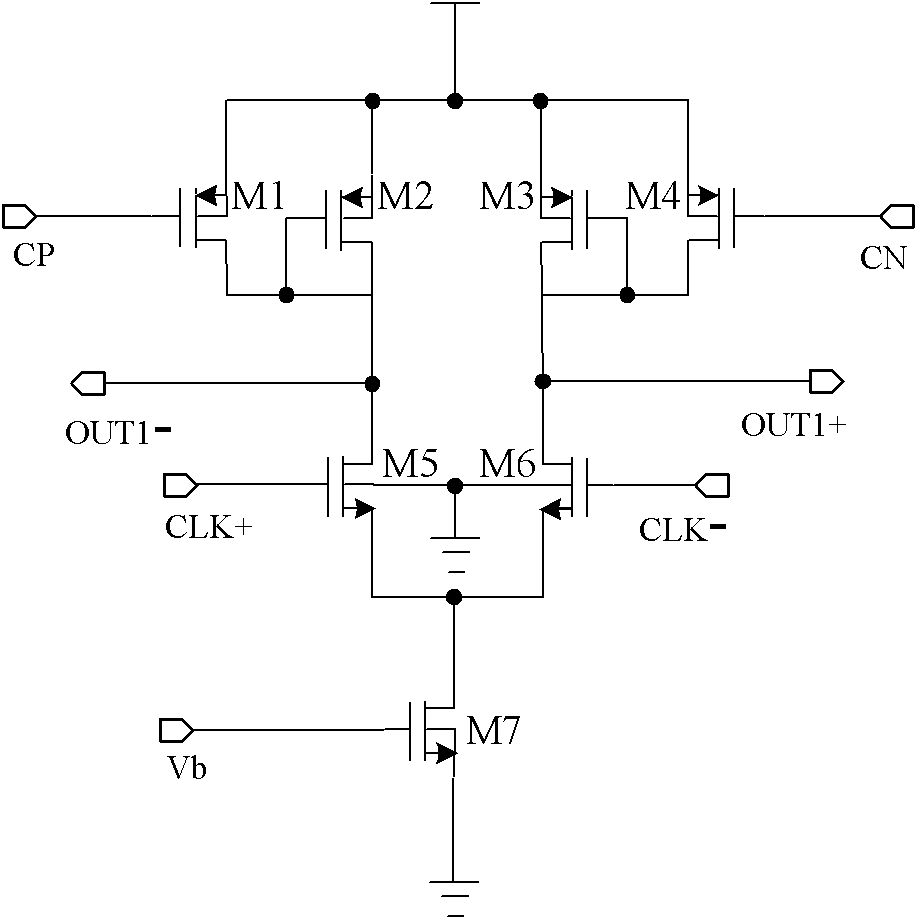

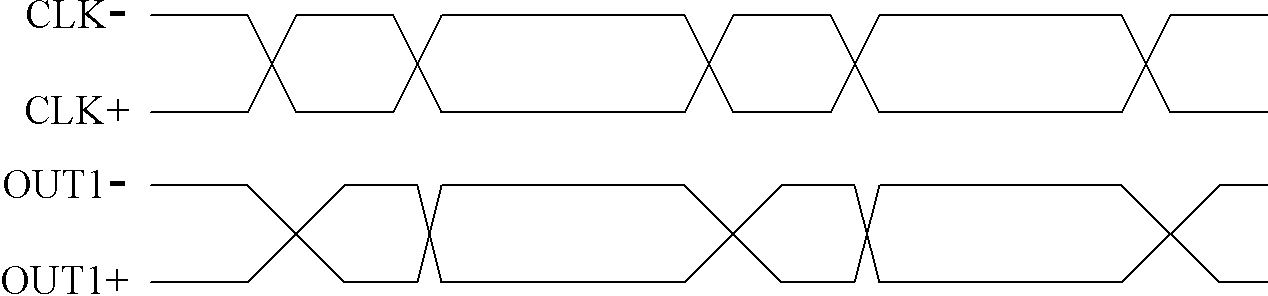

[0025] The present invention calibrates the duty cycle directly on the clock chain. Such as figure 1 As shown, the input differential clocks CLK+ and CLK- are directly input to the first adjustment stage, and the duty cycle is adjusted by adjusting the rise and fall time. The output signal enters the second adjustment stage after passing through the first buffer stage. The adjustment principle is the same as that of the first adjustment stage. Similarly, the output signal is a calibrated clock signal after passing through the second buffer stage. At the same time, the output clock signal enters the duty cycle detection stage to generate control voltages CP and CN to feed back to the first and second adjustment stages to form a duty cycle calibration loop until the final output clock signal duty cycle is 50%.

[0026] Duty Cycle Adjustment

[...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More