Keyboard scanning circuit and scanning method thereof

A keyboard scanning and scanning method technology, applied in the field of scanning, can solve the problems of increased cost of matrix keyboards, occupation of matrix keyboards, reduced stability of matrix keyboards, etc., and achieves strong circuit structure stability, fewer I/O ports, and concise scanning methods. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

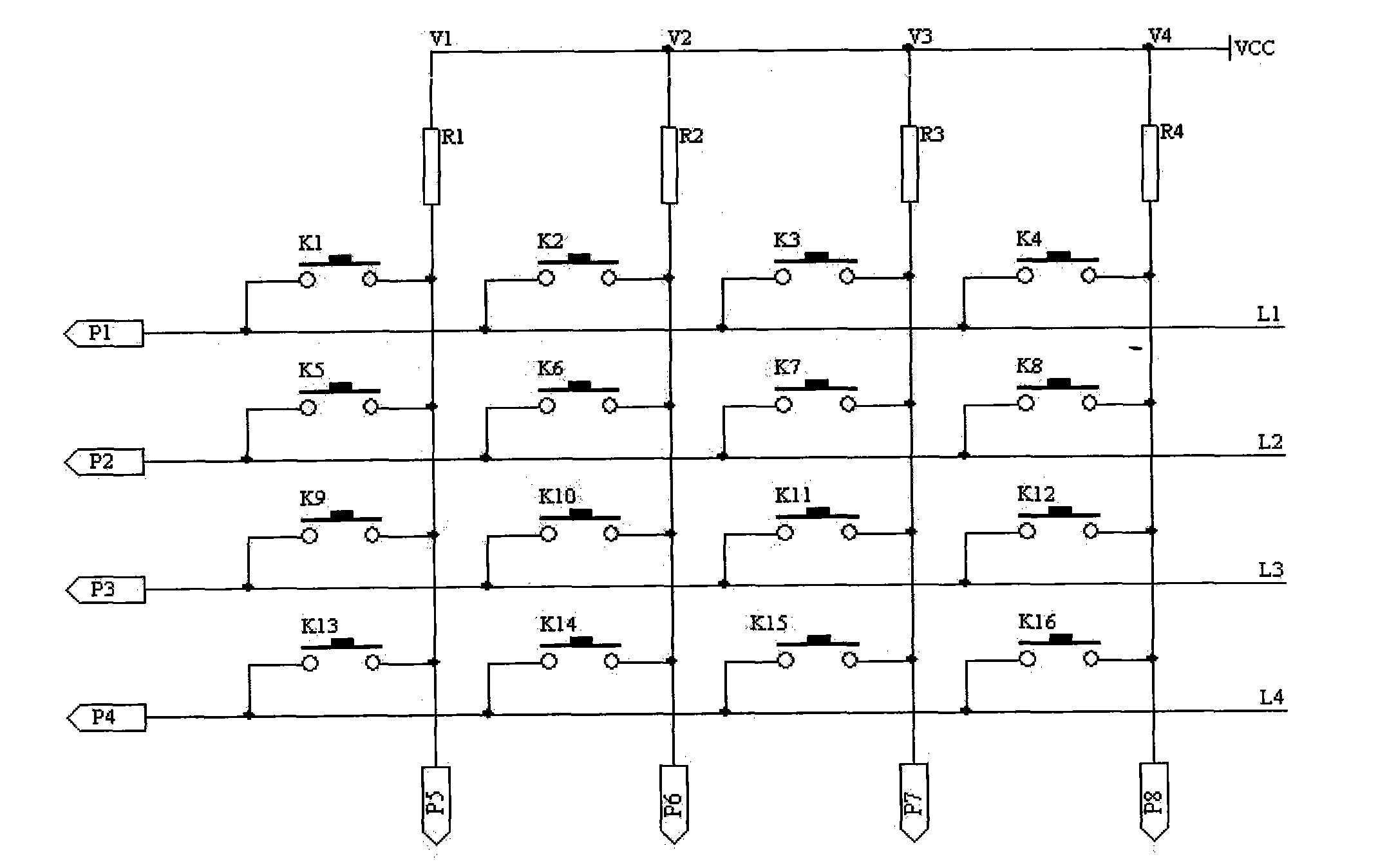

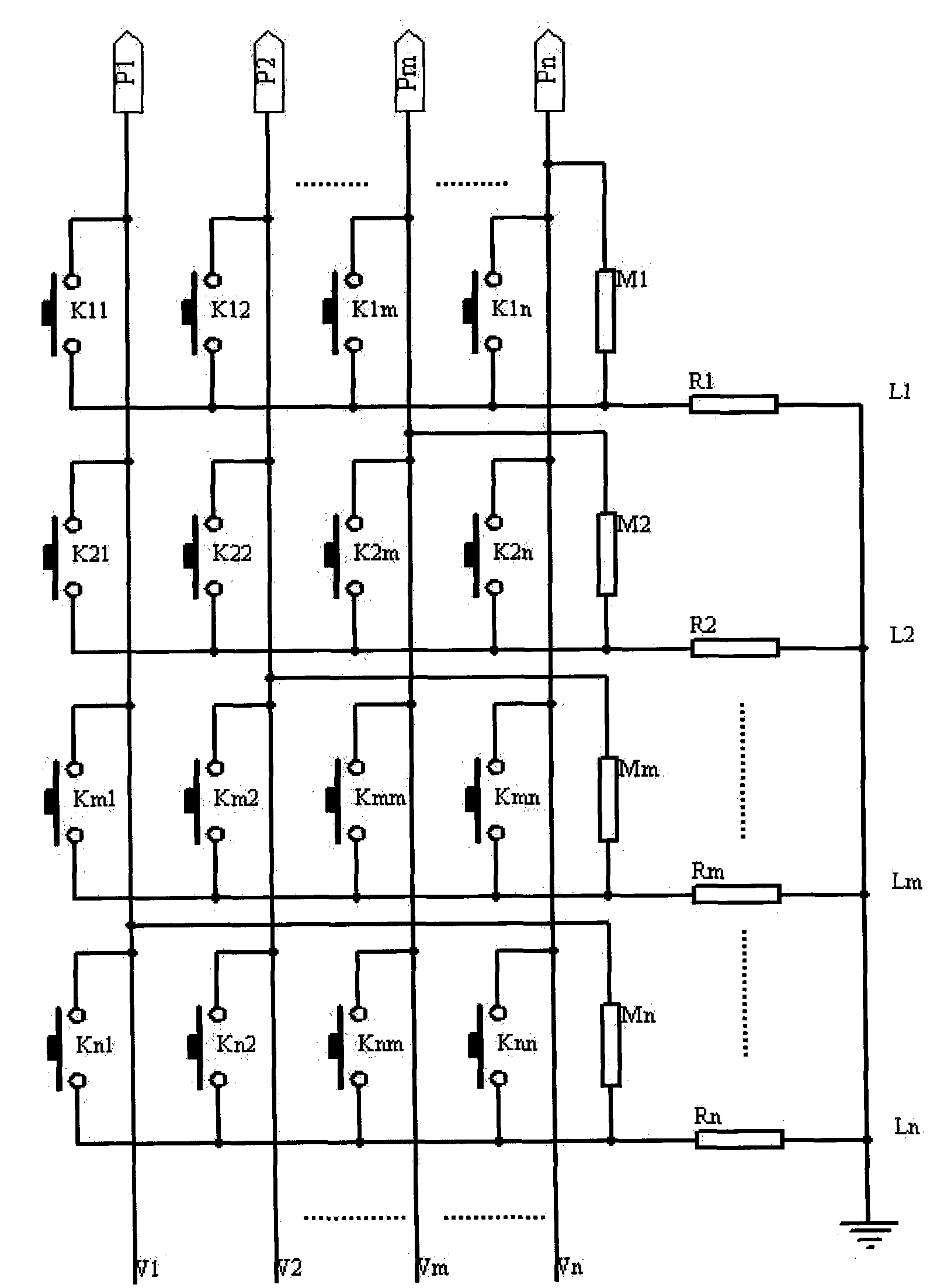

[0029] to combine figure 2 , a keyboard scanning circuit, including a processor with N I / O ports P1~Pn, N row lines L1~Ln and N column lines V1~Vn, and buttons K11~Knn are arranged at the crossing positions of the row lines and column lines , one end of the button is connected to the row line, and the other end is connected to the column line.

[0030] Each I / O port of the processor is a bidirectional I / O port with a pull-up resistor, the N row lines L1-Ln are respectively connected to a load resistor R1-Rn and then grounded, and one end of the N column lines V1-Vn Connect the I / O ports P1 to Pn of the processor respectively. The row lines from top to bottom are the first row line L1, the second row line L2, the third row line L3...the Nth row line Ln, and the column lines are the first column line V1 and the second column from left to right Line V2, 3rd column line V3...Nth column line Vn, 1st row line L1 and Nth column line Vn combination, 2nd row line L2 and N-1th column...

Embodiment 2

[0033] to combine figure 2 The scanning method of keyboard scanning circuit comprises the following steps:

[0034] (1) Initialize the N I / O ports of the processor, set each I / O port to an input state, and enable the pull-up resistor on the port.

[0035] (2) Read the level status of each I / O port. If the level status of the I / O port connected to the i-th column line is low, it means that the button on the i-th column line where the port is located is pressed, then Proceed to step (3); if no I / O port level status is low, return to step (1) to continue execution.

[0036] (3) Cancel the pull-up resistors on each I / O port, set the I / O port connected to the i-th column line as output, set the level state as high, and set the other I / O ports as low.

[0037] (4) Read the level status of each I / O port. If the level status of the I / O port connected to the j-th column line is high, it indicates the position where the N+1-j-th row line crosses the i-th column line The key on is pr...

Embodiment 3

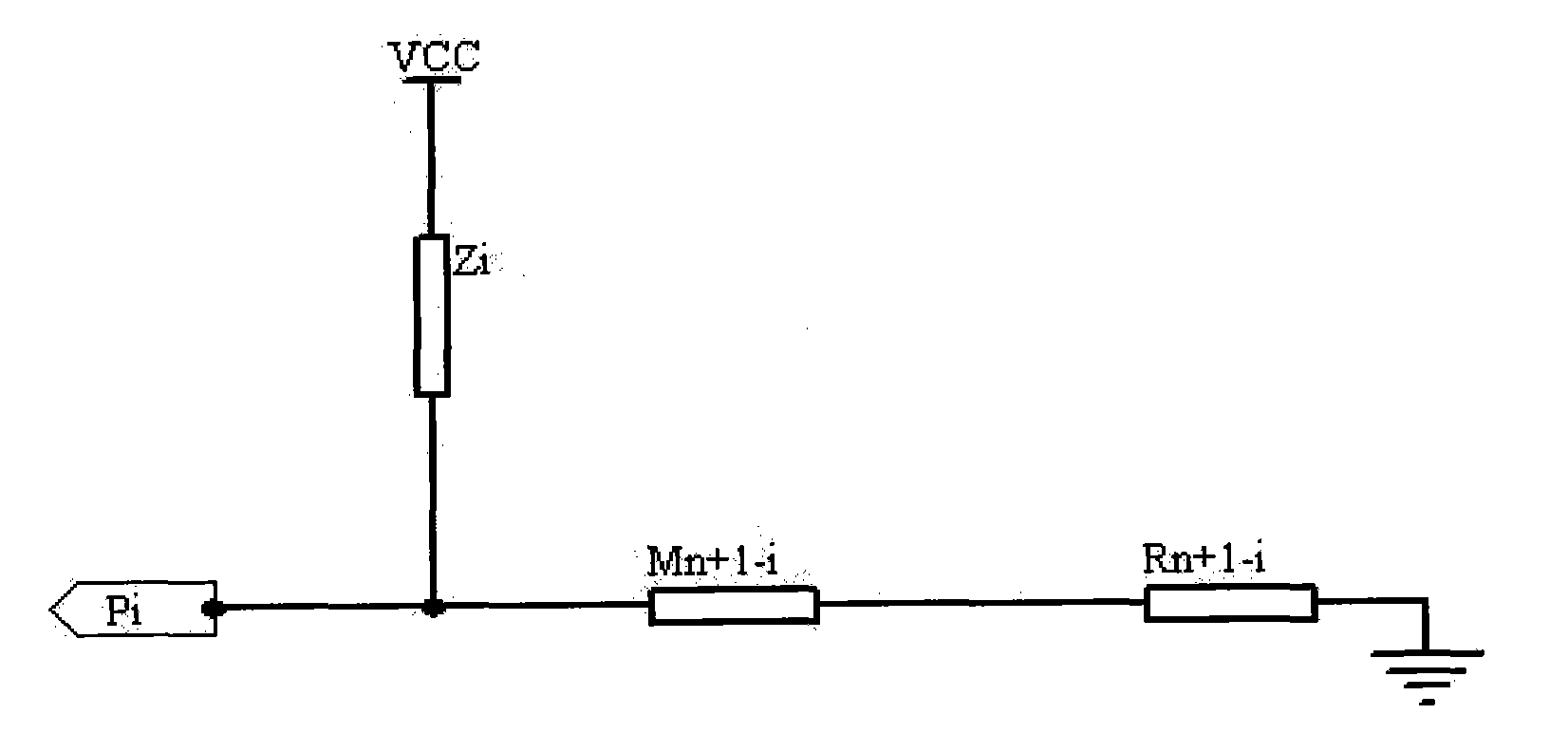

[0039] to combine figure 2 , image 3 , Figure 4 , Figure 5 , the internal pull-up resistors of N I / O ports P1~Pn are 10,000-ohm level Z1~Zn respectively. When the matrix keyboard circuit is scanning, all I / O ports are set as input, and the pull-up resistors on the ports are enabled. When the i-th column Vi where the port Pi is located is not pressed, the equivalent circuit connected to the port Pi is as follows: image 3 As shown, the port Pi is connected to the power supply VCC (high level) through the pull-up resistor Zi, and connected to the ground wire through the mega-ohm resistance element Mn+1-i and the kilo-ohm resistance element Rn+1-i. When the voltage of the port Pi is (Mn+1-i+Rn+1-i)×VCC / (Mn+1-i+Rn+1-i+Zi), the input register PIN of the port Pi is at a high level.

[0040] When a button is pressed in the i-th column Vi, the equivalent circuit of the port Pi connected to the i-th column Vi is as follows Figure 4 As shown, the port Pi is connected to the po...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More