Test package scan chain balancing method based on mean value allowance in SoC (System On Chip) test

A technology for testing packaging and scanning chains, which is applied in the direction of measuring devices, measuring electricity, and measuring electrical variables, etc. It can solve the problems that the global optimization guidelines are not close to the actual situation, and the BFD algorithm does not have global optimization.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

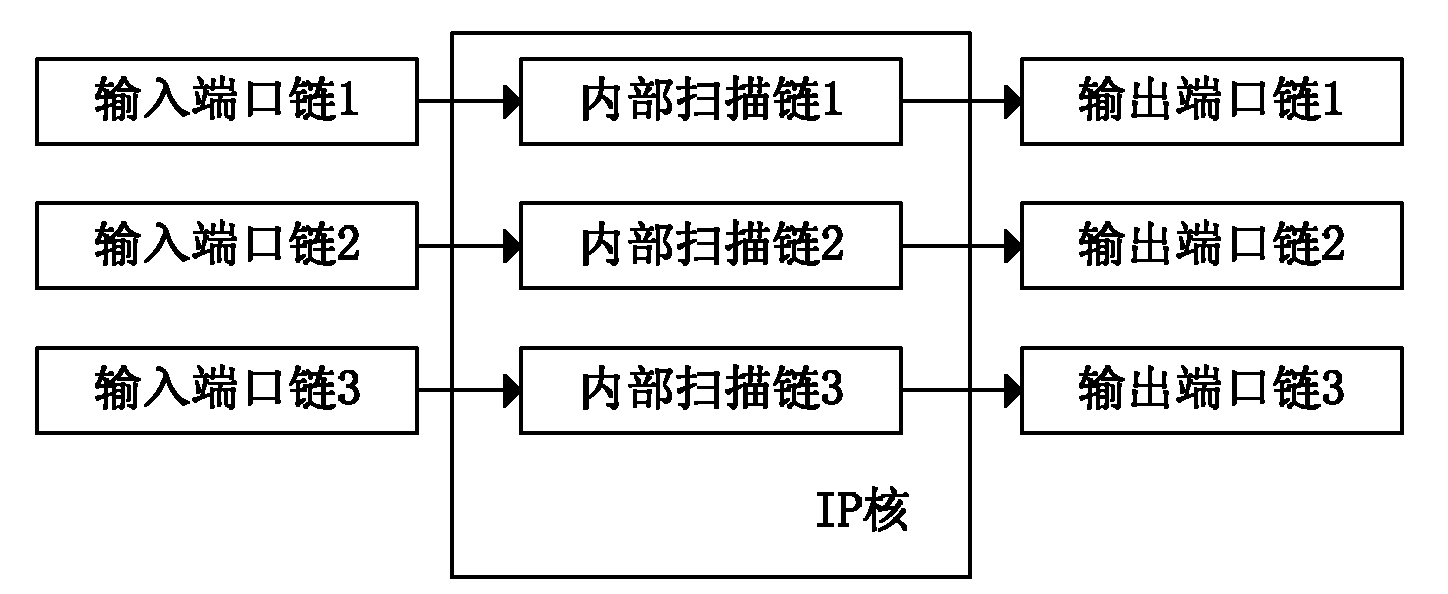

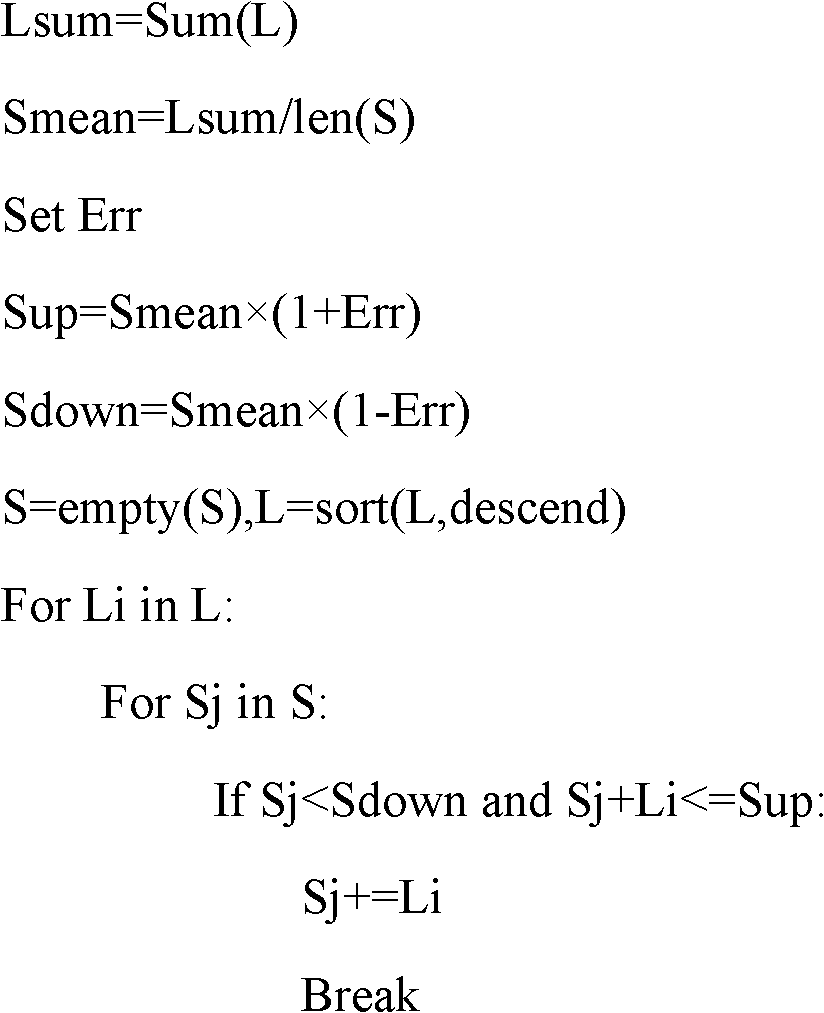

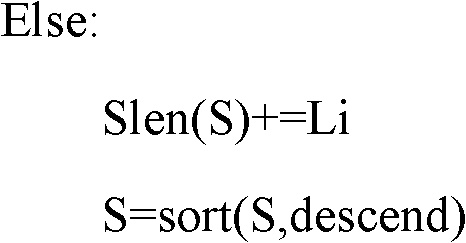

[0029] DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS 1. The process of the method for balancing the scan chain of the test package scan chain based on the average margin in the SoC test described in this embodiment is:

[0030] First, calculate the average length of the Wrapper scan chain;

[0031] Then, an error limit is determined according to the obtained average length, and the error limit is 1% to 3% of the average length;

[0032] Finally, the value range is calculated according to the error limit and the average value of the Wrapper scan chain length, and the value range is used as a guiding principle for global optimization to realize the balance of the test package scan chain.

[0033] The scan chain balancing method described in this embodiment uses a range near the average value of the Wrapper scan chain length as a guiding principle for global optimization, making it closer to the actual situation, and this algorithm always prioritizes the current longest inter...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More