Method and device for implementing interlacing or deinterlacing

A deinterleaving and matrix technology, applied in the field of data transmission, can solve the problems of large storage overhead and large processing delay, and achieve the effects of improving processing functions, reducing processing delay, and saving storage space

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

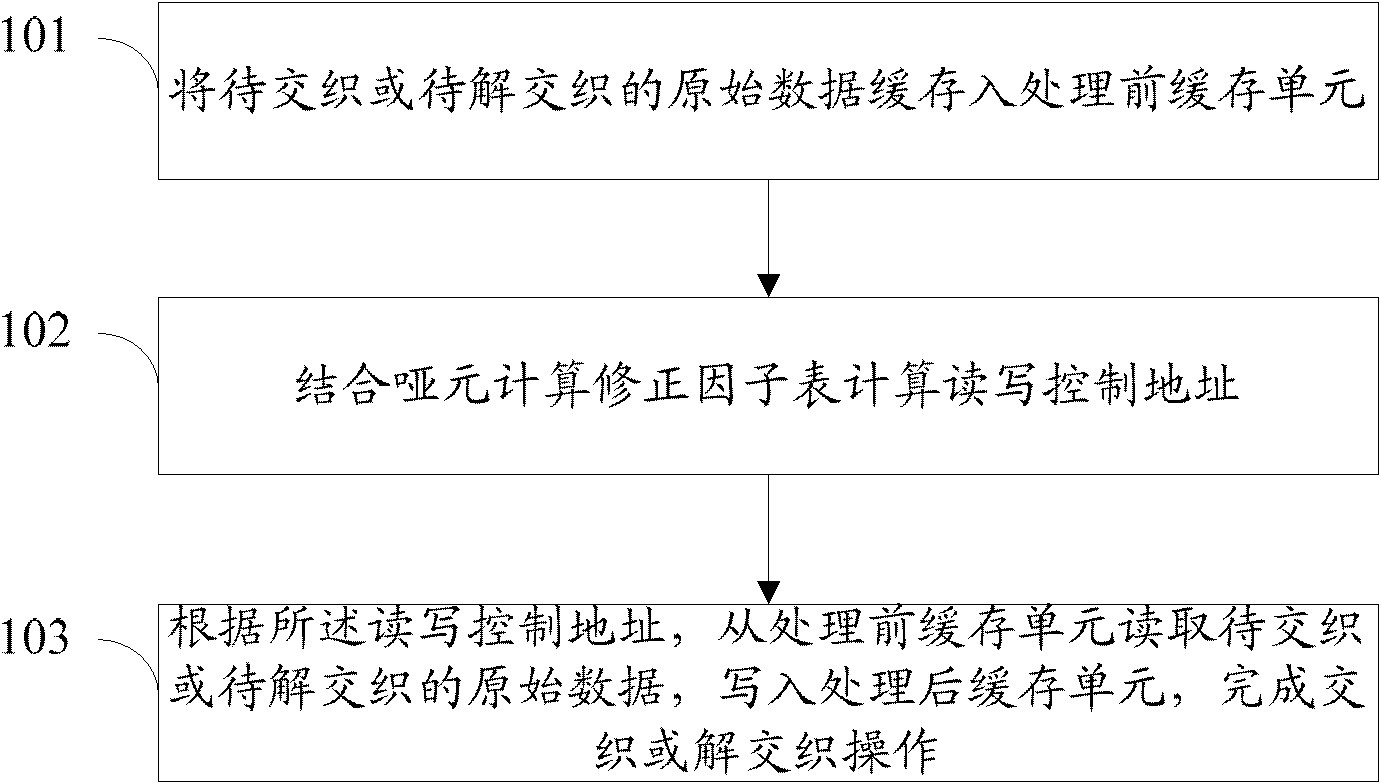

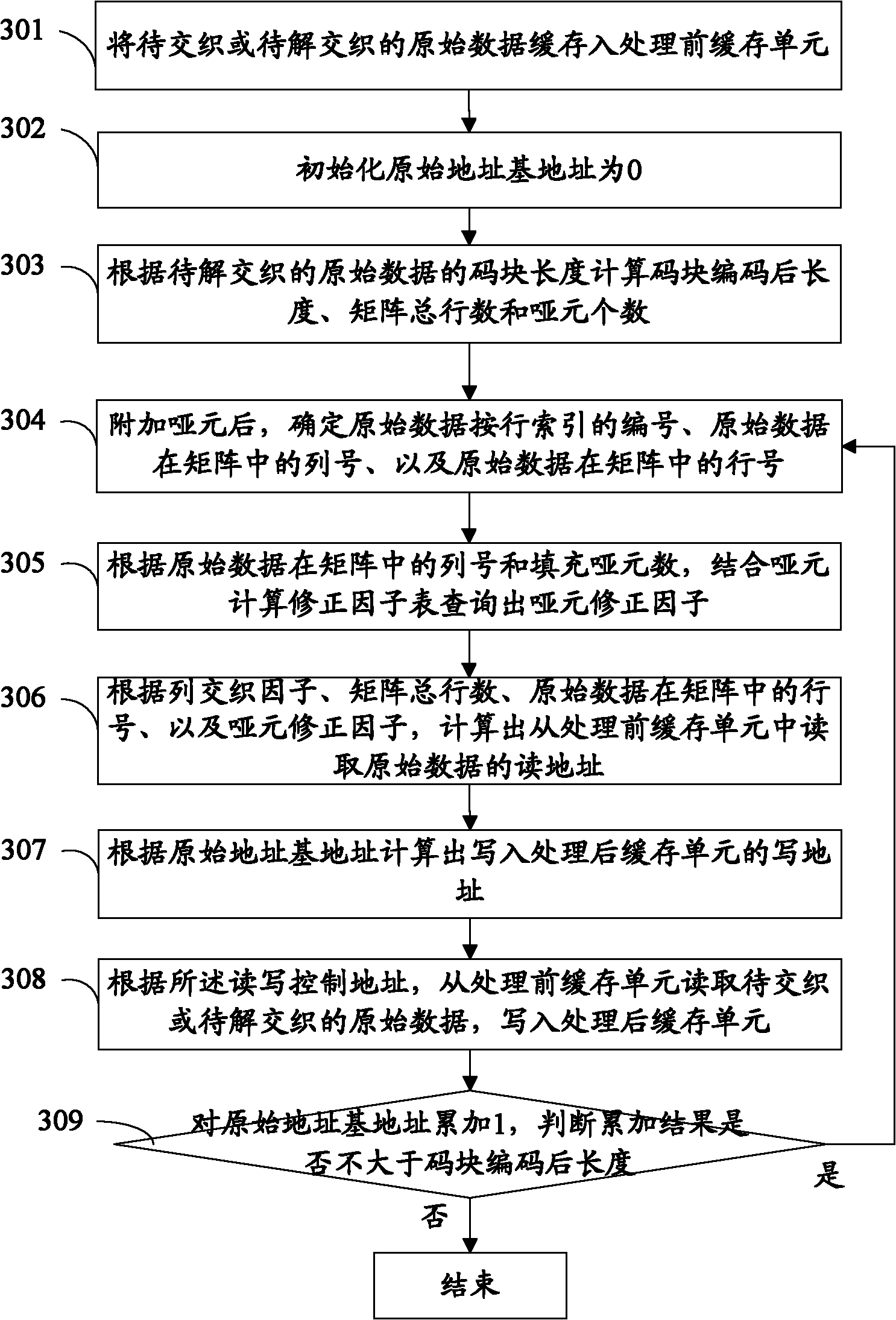

[0027] The basic idea of the present invention is to cache the original data to be interleaved or to be deinterleaved into the pre-processing cache unit; to calculate the correction factor table in conjunction with the dummy element to calculate the read-write control address; according to the read-write control address, read from the pre-process cache unit The original data to be interleaved or deinterleaved is taken, and the processed buffer unit is written to complete the interleaving or deinterleaving operation.

[0028] The technical solutions of the present invention will be further elaborated below in conjunction with the accompanying drawings and specific embodiments.

[0029] figure 1 It is a schematic flow chart of an implementation method of interleaving or deinterleaving in the present invention, such as figure 1 As shown, the method includes:

[0030] Step 101, buffering the original data to be interleaved or to be deinterleaved into the pre-processing buffer ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More