Fusion processing device and method for floating-point number multiplication-addition device

A technology of fusion processing and floating-point multiplication, which is applied in the direction of electrical digital data processing, digital data processing components, instruments, etc., can solve the problems that are not refined to hardware implementation, and do not further analyze the interface from multiplication output to addition input, etc. Achieve the effect of simple and easy hardware implementation, easy hardware implementation, and simplified operation steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

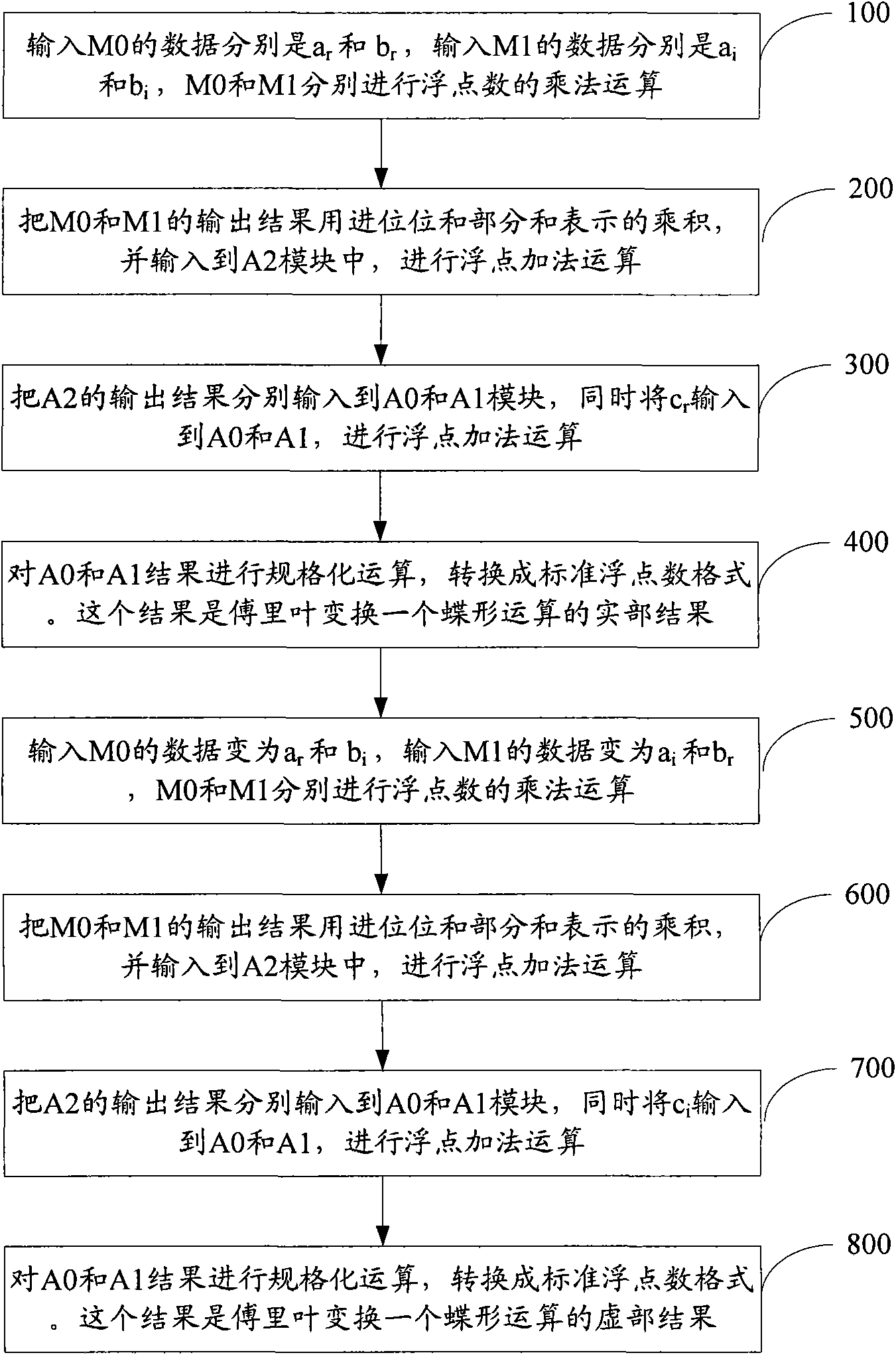

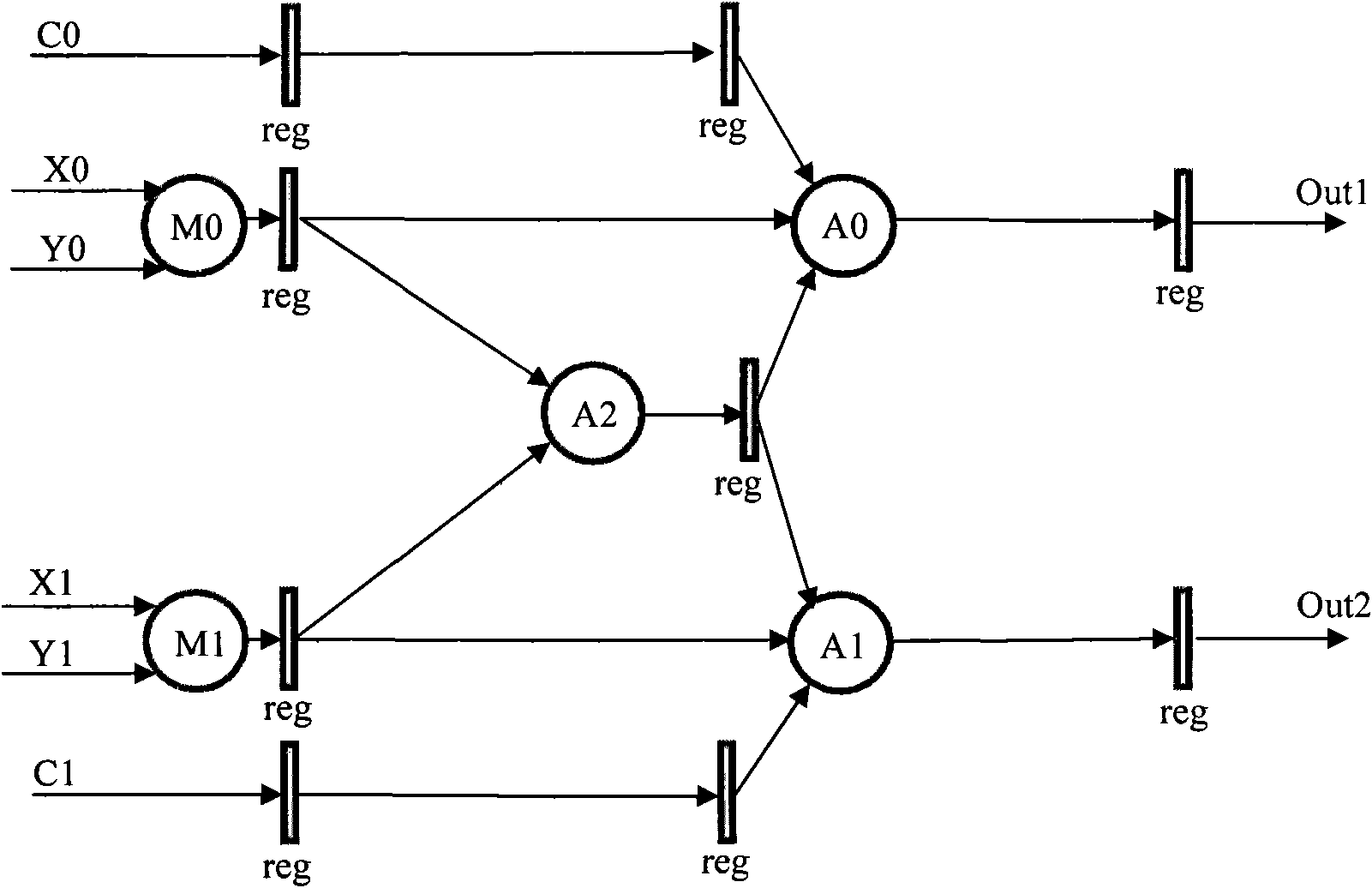

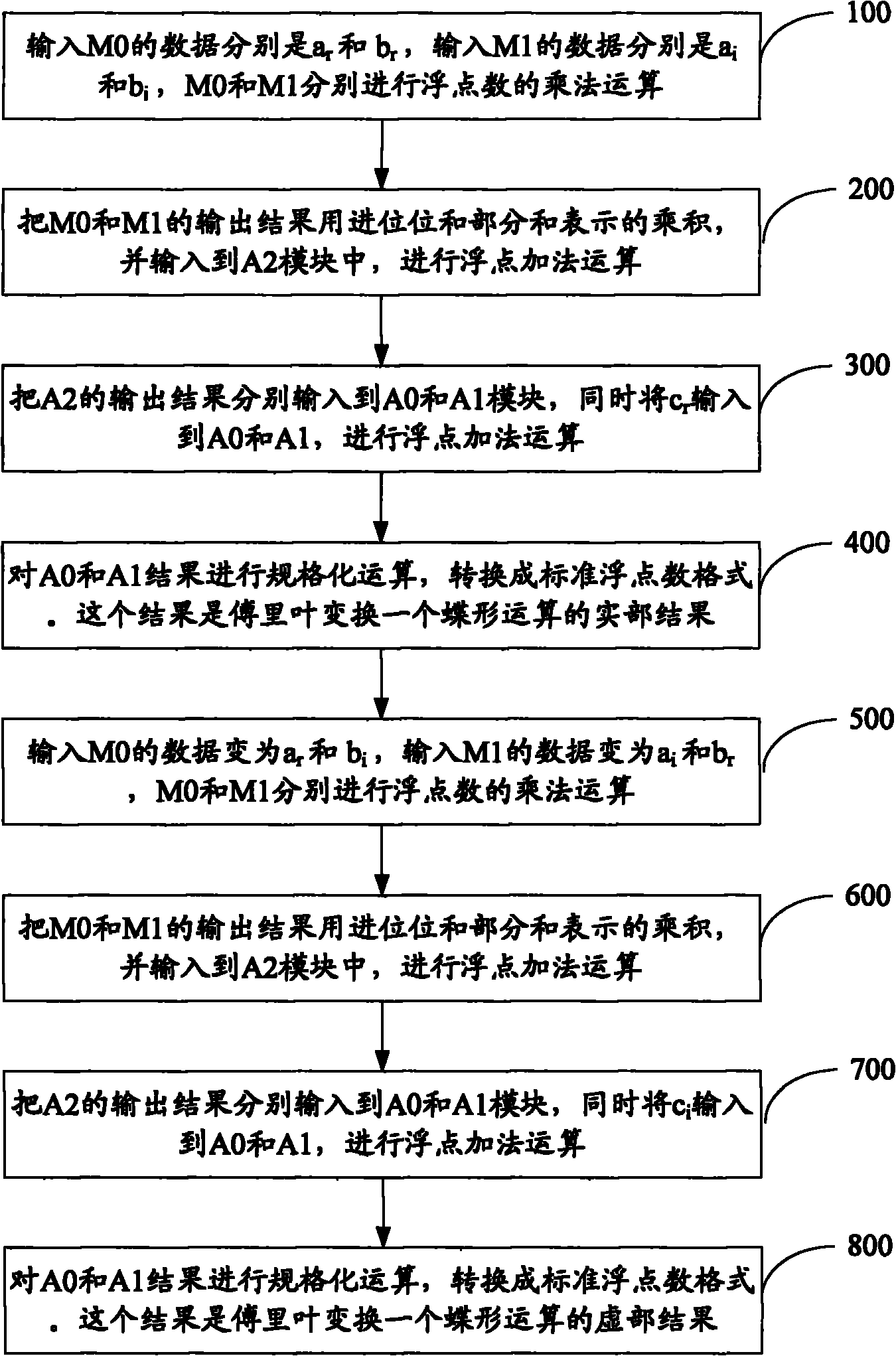

[0019] Below, refer to the attached Figure 1~2 Describe in detail the floating-point multiplier-adder fusion processing device and method of the present invention.

[0020] The core idea of the present invention is: input the real part and the imaginary part of the floating-point complex multiplier and the multiplicand to the floating-point multiplication modules M0 and M1, the data is first carried out in the floating-point multiplication operation, and the output result uses the carry bit and the partial sum Represented by the product, and input the result to the floating-point addition module A2 for addition, the output is also the form of the sum of the carry bit and the partial sum, and then input the result to the floating-point addition modules A0 and A1 at the same time, and then the external input The addend and the addend are also input to the floating-point addition modules A0 and A1 for floating-point addition operation, and finally the operation result is outpu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More