Method for allocating registers for mixed length instruction set

A technology of register allocation and mixed length, applied in the field of compilation, to achieve the effect of strong reliability and improved instruction density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

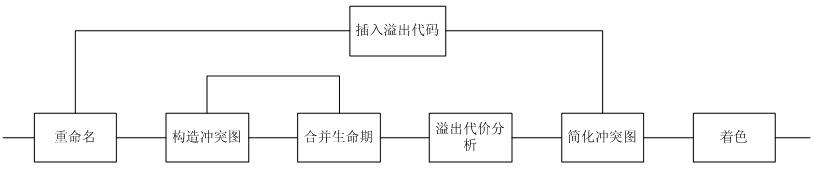

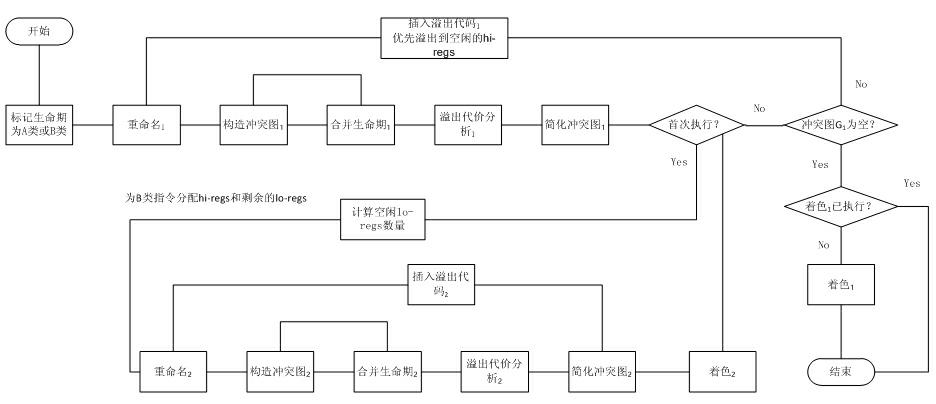

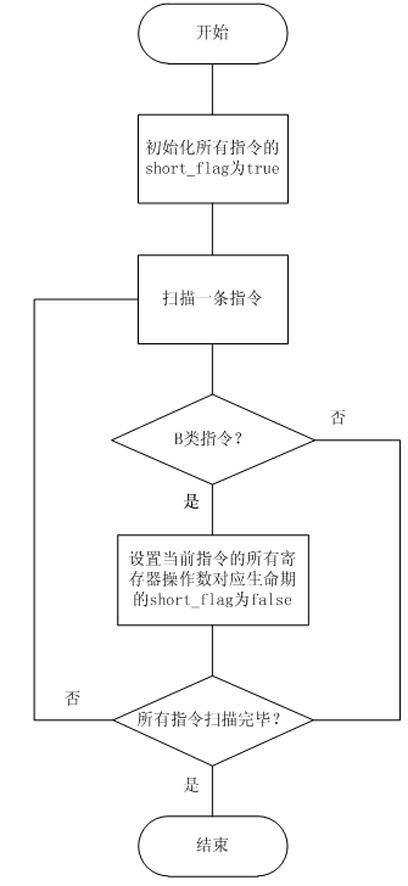

[0037] The invention is an improved register allocation method based on the graph coloring register allocation method. Graph coloring is the traditional and most commonly used method of register allocation. The basic process is as follows figure 1 A brief description of each phase is as follows:

[0038] Rename (Renumber): Before this stage, the intermediate code can refer to an unlimited number of "virtual registers". In this stage, based on data flow analysis, find all lifetimes in the function and assign unique numbers to them. A lifetime begins with one setting of a variable and ends with the last use of that value.

[0039] Construct conflict graph (Build): At this stage, a "conflict graph G" is established. The nodes in G are life periods, and the edges indicate that there is a conflict between the two life period...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More