Layout method for heterogeneous field programmable gate array (FPGA)

A layout method and gate array technology, applied in the field of field programmable gate array layout, to achieve the effect of optimizing layout results, improving performance, and reducing running time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

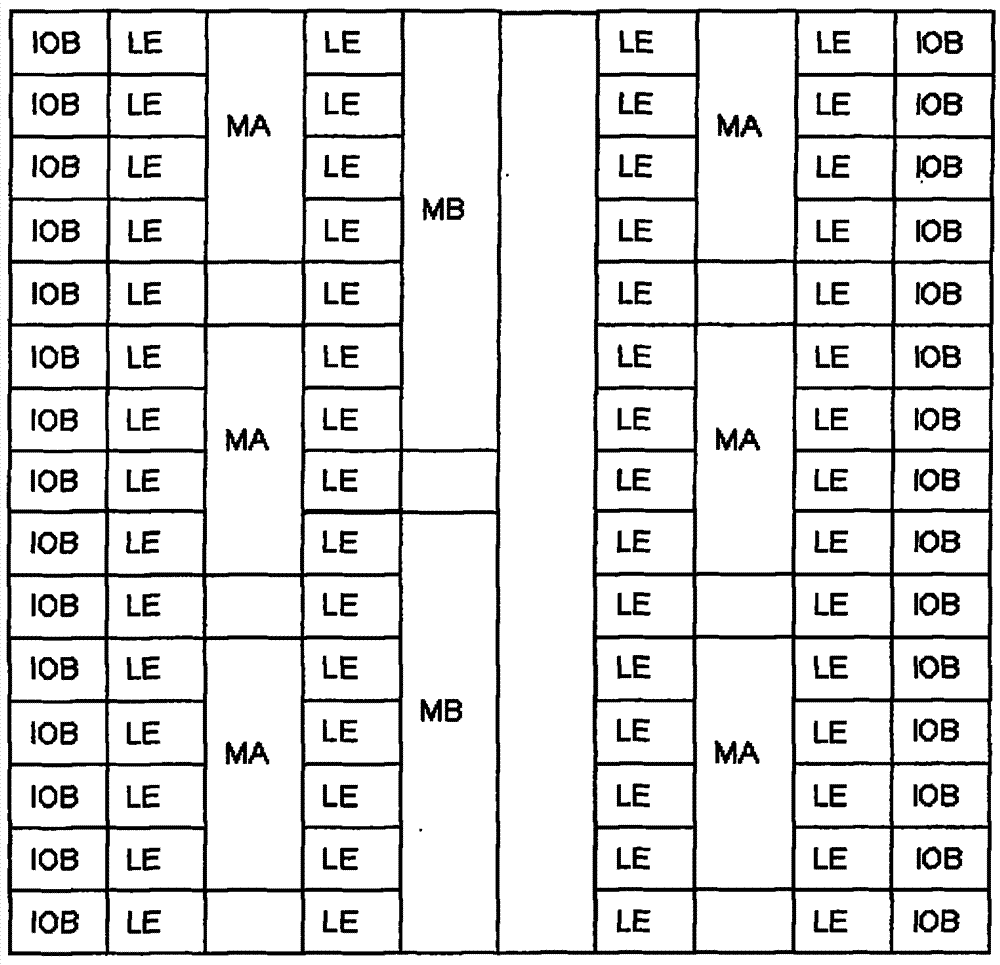

[0028] figure 1 It is a schematic diagram of a column structure FPGA. This type of FPGA has been used by many famous FPGA manufacturers such as Alteral and Xilinx. exist figure 1 Among them, IOB (IO-Block): input and output module; LE (Logic Element): basic logic unit, which consists of look-up tables, registers, etc.; MA (Macro A): macro unit of type A; MB (Macro B) : A macrocell of type B.

[0029] The embodiments of the present invention are not only applicable to FPGAs with a column structure type, but also applicable to FPGAs of various heterogeneous types.

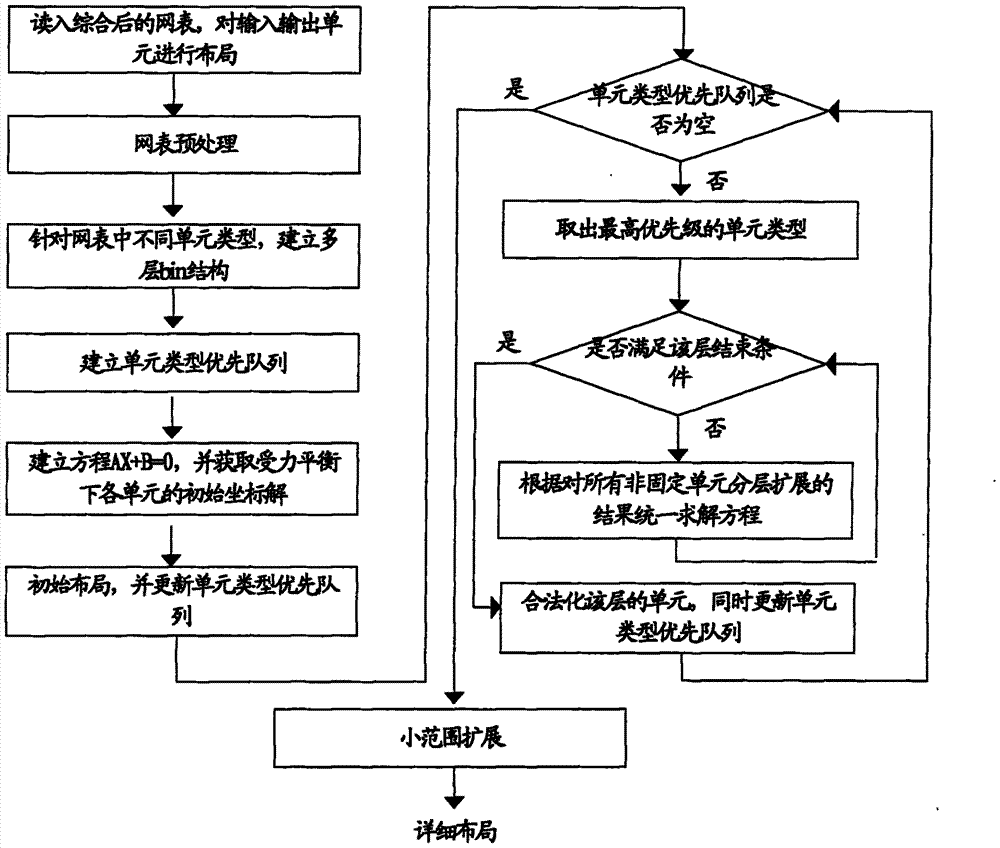

[0030] figure 2 It is a flowchart of a field programmable gate array layout method according to an embodiment of the present invention.

[0031] Step 1: Read in the synthesized netlist and lay out the input and output units. After synthesizing the design file into a gate-level circuit and analyzing it, then the peripheral input and output units ( figure 1 IOB in ) for layout. Use the random layout method com...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More