Settable and resettable D trigger resisting single event upset

An anti-single-event, trigger technology, applied in the direction of electrical pulse generator circuit, reliability improvement modification, pulse generation, etc., can solve the problem of low anti-single-event flipping ability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

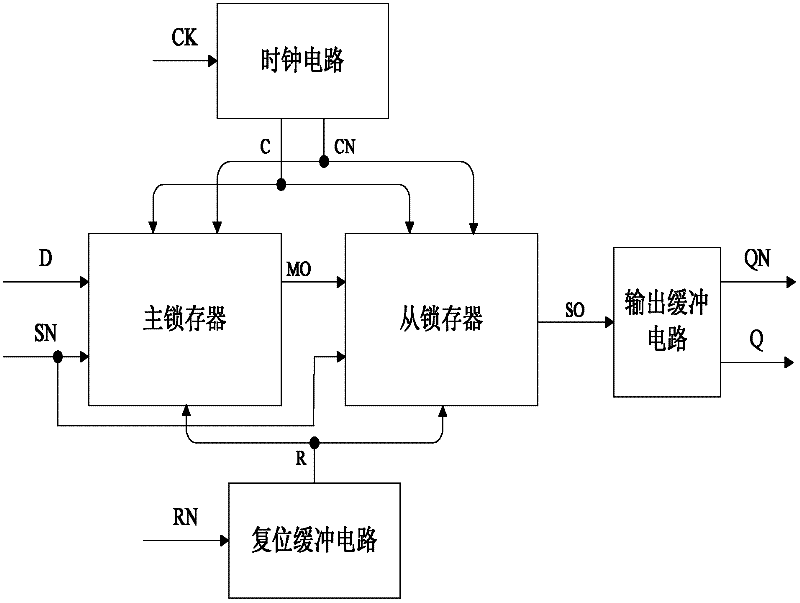

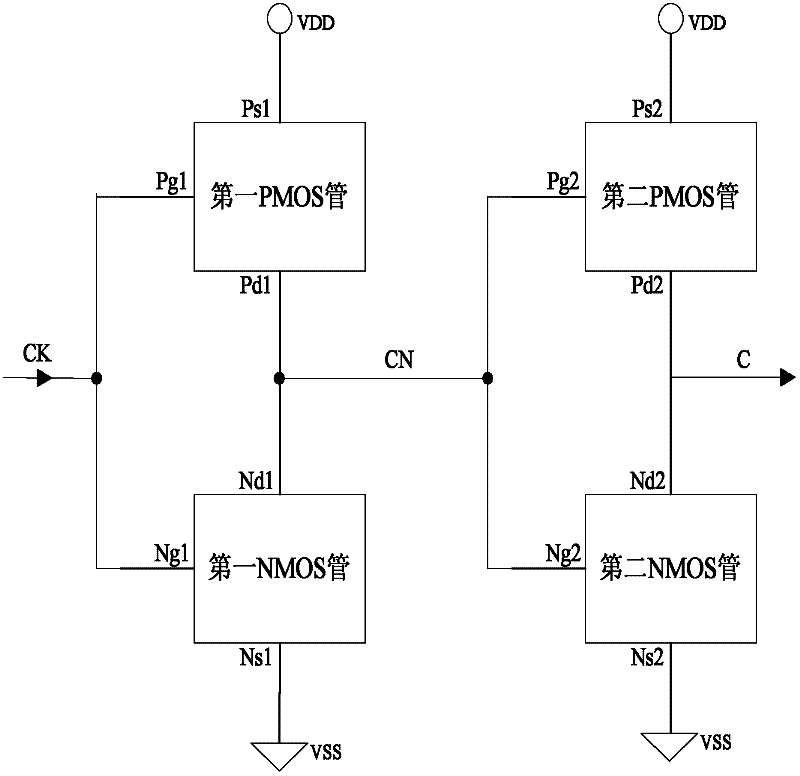

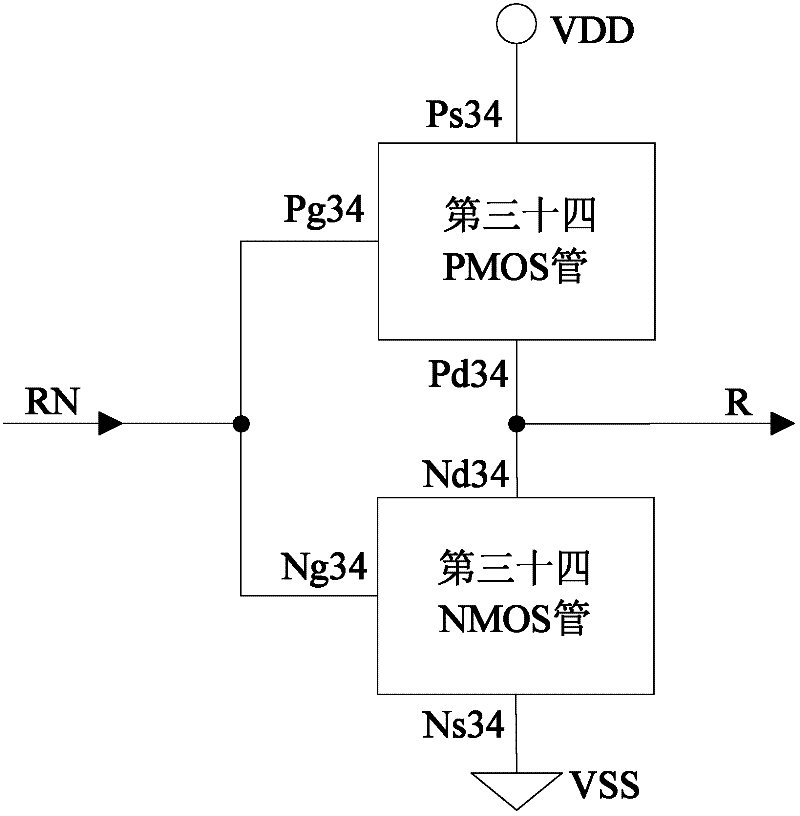

[0030] figure 1 It is a schematic diagram of the logic structure of the settable and resettable D flip-flop against single event upset of the present invention. The present invention consists of a clock circuit (such as figure 2 shown), reset buffer circuit (such as image 3 shown), the master latch (as Figure 4 shown), slave latches (such as Figure 5 shown) and the output buffer circuit (as Figure 6 shown) composition. The present invention has four inputs and two outputs. The four input terminals are CK, which is the clock signal input terminal, D, which is the data signal input terminal, SN, which is the set signal input terminal and RN reset signal input terminal; the two output terminals are Q and QN, and Q and QN output a pair opposite data signal. The clock circuit receives CK, and outputs C and CN respectively after buffering CK. The reset buffer circuit buffers RN, inputs R which is inverse to RN, and transfers R to the master latch and the slave latch. T...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More