System and method for testing universal interface

A test system and general interface technology, applied in error detection/correction, instrumentation, electrical digital data processing, etc., can solve the problems of low serial port data throughput, unable to meet the needs of testing, and the test platform is not fully automated. Achieve the effect of improving test efficiency and reducing test labor costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] specific implementation plan

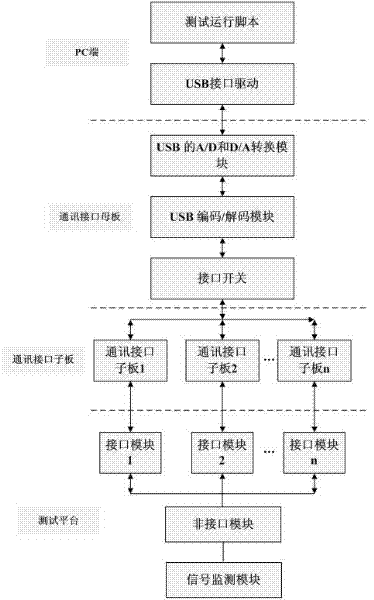

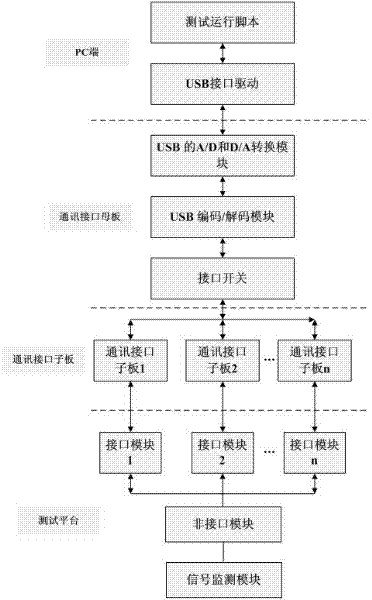

[0027] The following is attached figure 1 The general interface test system and its test method proposed by the present invention are described in detail.

[0028] The PC end is connected with the communication interface motherboard through the USB interface, and the script command is sent to the communication interface motherboard through the USB driver program at the PC end. The communication interface motherboard performs A / D conversion, protocol analysis, interface switching and other processing on the signal. The communication interface template is connected to the communication interface sub-board through a hard line, and the communication interface sub-board performs conversion according to each port protocol. The communication interface sub-board is connected to the test platform for test communication, and the test platform interfaces receive and test respectively.

[0029] The communication interface motherboard is mainly comp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More