Anti-interference error-correcting and sampling system and method in process of receiving asynchronous serial communication data

An asynchronous serial communication and data technology, applied in the direction of digital transmission system, transmission system, error prevention, etc., can solve problems such as sampling error data, and achieve the effect of increasing stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

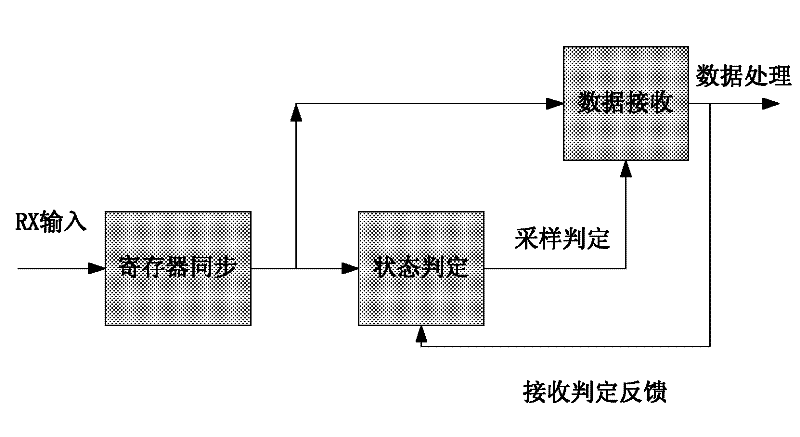

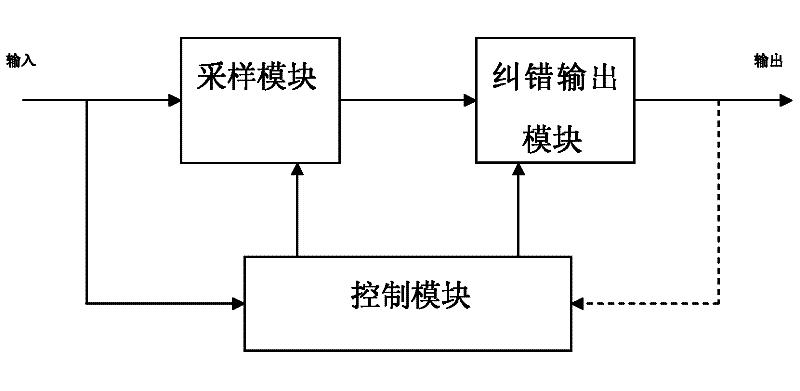

Method used

Image

Examples

example 1

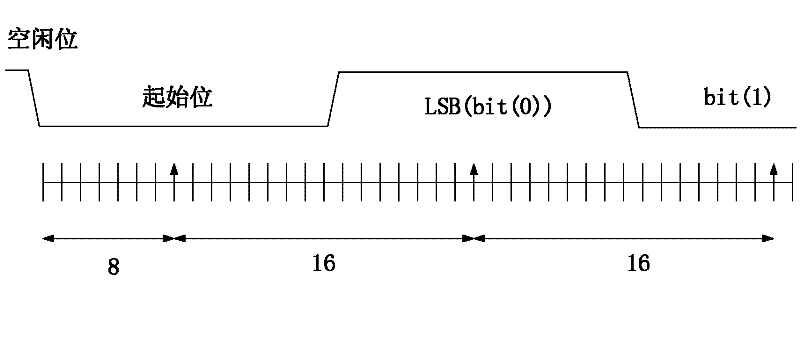

[0048] Assuming that the baud rate frequency division factor N of asynchronous serial communication is 16, the correct input level should be high level under the condition of no interference, but at the middle moment, the external input generates random pulse interference, such as No. 5-9 A baud rate clock has 5 periods of low level in succession. The data receiving module in the traditional data receiving system samples only the wrong low-level signal at the eighth baud rate clock. However, by Figure 6 Shown according to the data receiving system that adds filter sampling module of the present invention, the addition and subtraction counter in the filter sampling module adds 1 operation at the 5th-9th baud rate clock, and carries out at other 10 baud rate clocks Subtract 1 operation. At the 16th baud rate clock, the data receiving module samples the sign bit of the up-down counter in the filter sampling module. Since the value of the up-down counter in the filter sampling...

example 2

[0050] Assume that the baud rate frequency division factor N of asynchronous serial communication is 32, and the correct input level is low level under the condition of no interference. On the 3rd-9th, 15th-16th, and 30th-31st baud rate clocks, interference high-level signals randomly appeared one after another. These signals passed Figure 6 The up-down counter in the filter sampling module according to the present invention shown in the present invention generates 11 minus-1 operations afterwards, and generates plus-1 operations in the other 20 baud rate sampling periods. At the 32nd baud rate clock, the data receiving module samples the sign bit of the up-down counter in the filter sampling module. Since the value of the counter at this time is +9 (=0-7-2-2+20), the output value of the data receiving module remains at the correct low level 0.

[0051] The advantages of the present invention are obvious through the above detailed description in conjunction with the embodim...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More