Method for confirming memory controller clock calibration value and system thereof

A memory controller and clock calibration technology, applied in the direction of generating/distributing signals, etc., can solve the problems of increasing the user's operating burden and slow speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] In order to make the objects and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

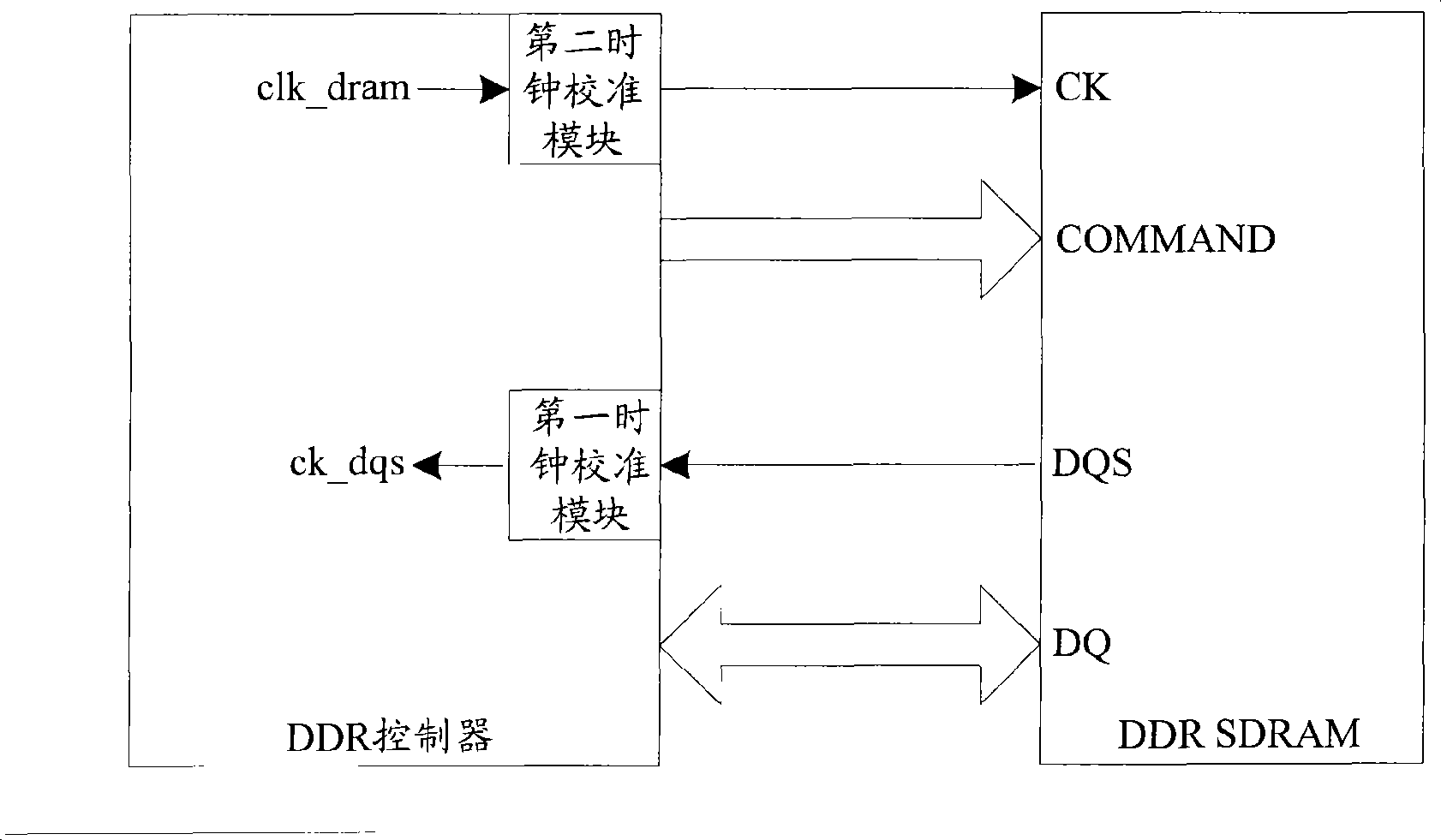

[0038] First, the system of the present invention for determining a memory controller clock calibration value is described.

[0039] Image 6It is a schematic structural diagram of a system for determining a clock calibration value of a memory controller in an embodiment of the present invention. In this embodiment, the memory controller can control the DDR memory and the SDR memory compatible. Combine below Image 6 , respectively explain the functions of each device in the system and the connection relationship between them.

[0040] 1) The first clock calibration device.

[0041] The first clock calibration device is used for calibrating the clock signal used for data sampling output by the selection device according to the first calibration value output by the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More