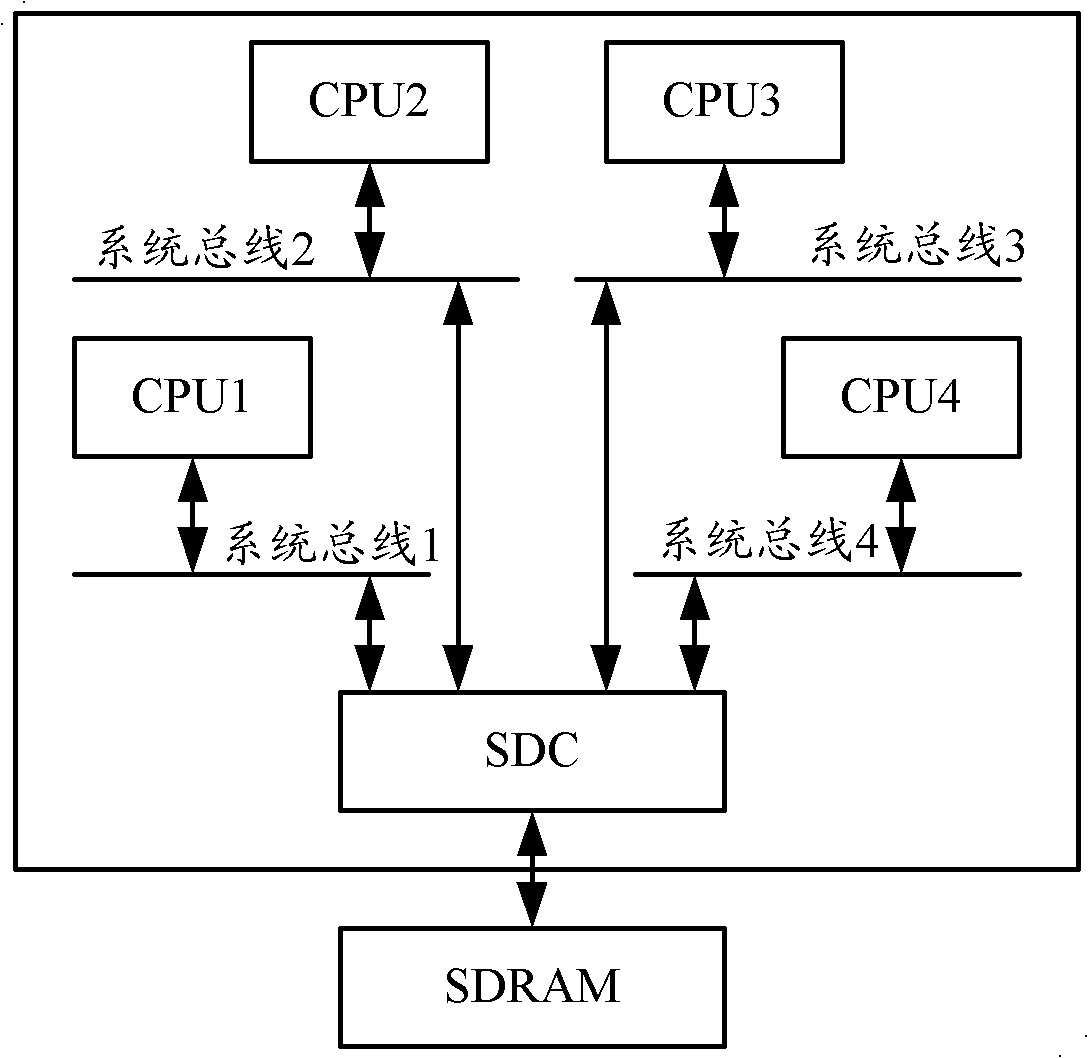

Dynamic bus frequency modulation method of off-chip memory and system thereof

An off-chip memory and dynamic frequency modulation technology, applied in the field of on-chip systems, can solve problems such as cumbersome software processing, unfavorable system development and debugging, and achieve the effects of reducing software overhead, reducing power consumption, and reducing complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

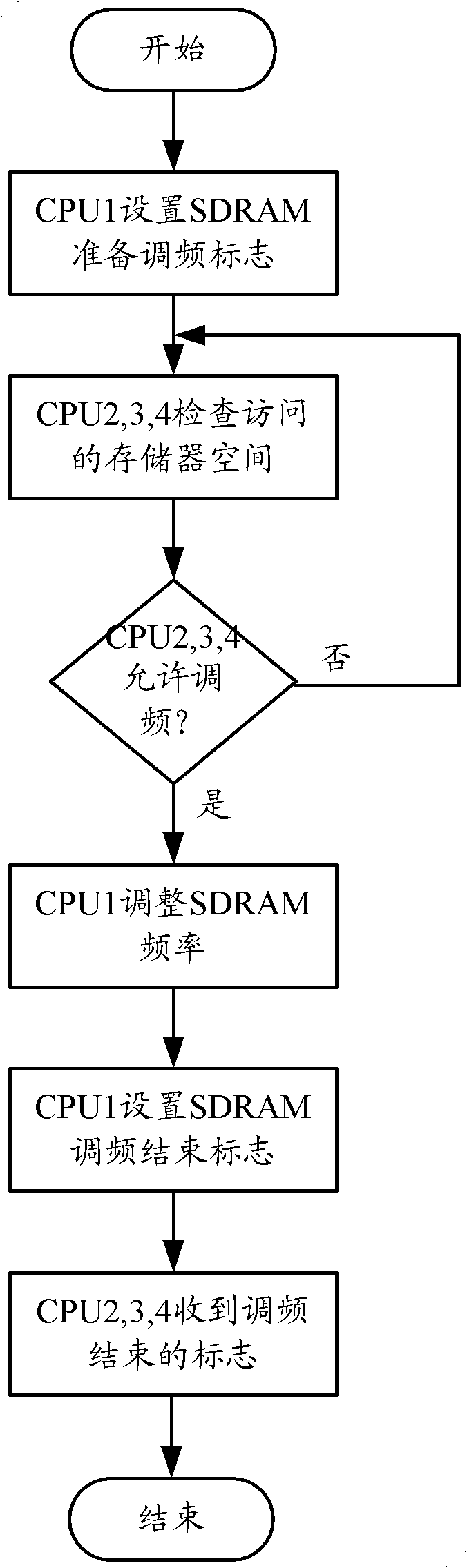

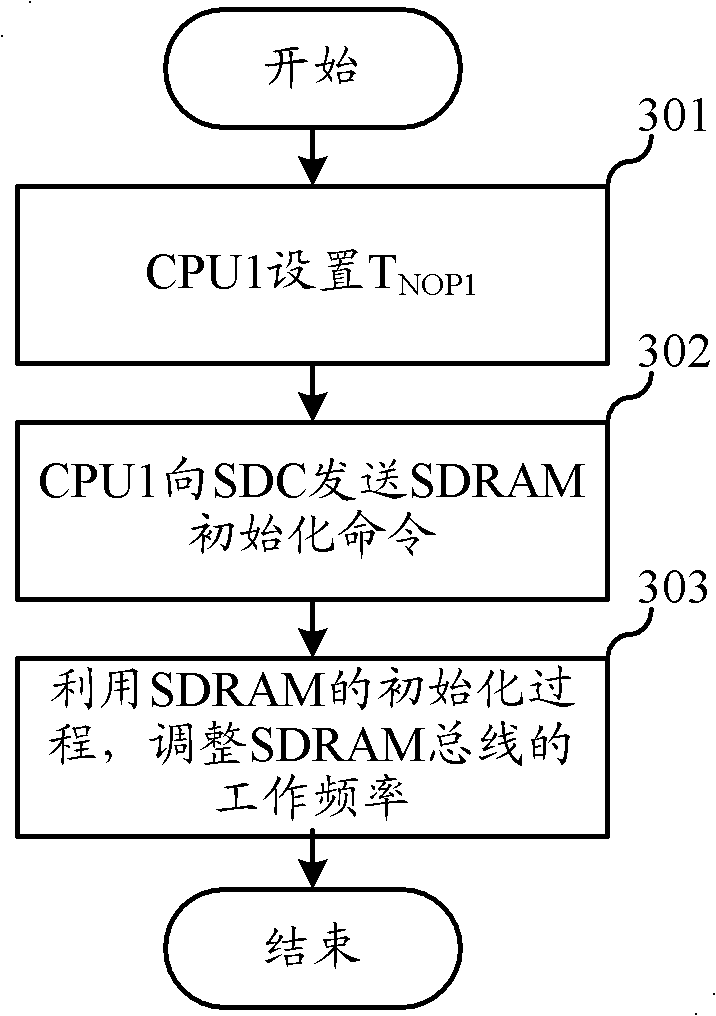

[0031] The first embodiment of the present invention relates to a bus dynamic frequency modulation method of an off-chip memory. The principle is as follows: when the CPU core performs frequency modulation, it first sends an SDRAM initialization command to the SDC controller. During the process of executing the SDRAM initialization command, the SDC controller queues up for access to the SDRAM outside the SDC controller, that is, At this stage, each CPU core cannot read and write access to off-chip SDRAM, and the SDRAM bus is in an idle state. Therefore, the operating frequency of the SDRAM bus can be adjusted by utilizing the idle state of the SDRAM bus.

[0032] In this embodiment, it will be described by taking CPU1 in the SOC chip to adjust the bus operating frequency of the SDRAM as an example.

[0033] The specific process is as image 3As shown, in step 301, CPU1 sets the duration of NOP1 during SDRAM initialization. Because in this embodiment, the SDRAM initializatio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com