FPGA (Field Programmable Gate Array) realization method for multi-code-length LDPC (Low Density Parity Check) code decoder on basis of hierarchical NMS (Network Management System) algorithm

A technology of LDPC codes and decoders, applied in the direction of using block codes for error correction/detection, applying multi-bit parity bit error detection coding, data representation error detection/correction, etc., which can solve the problem of reducing update information node updates The complexity of the connection between the unit and the memory, the complex connection between the node update unit and the memory, and the large storage capacity of update information have achieved the effects of fast read and write speed, ingenious structure, and reduced wiring difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

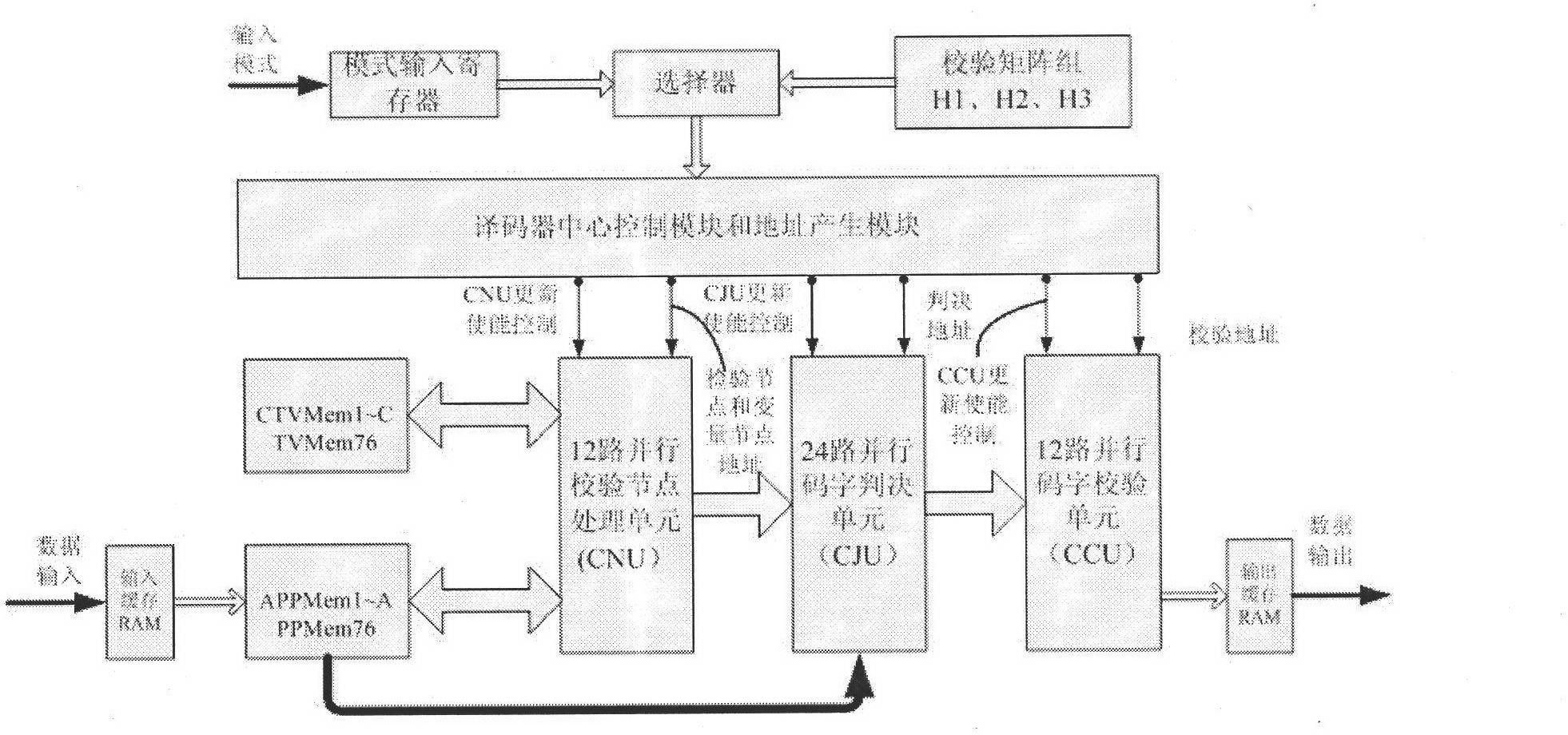

[0037] The invention discloses an FPGA implementation method of a multi-code length LDPC code decoder based on a layered NMS algorithm. The invention will be further described below in conjunction with the accompanying drawings.

[0038] First, the meanings of each letter and function representatives in the present invention are explained, specifically as follows:

[0039] R(j): refers to a set of all variable nodes connected to the verification node j, that is, all variable nodes participating in the verification equation j.

[0040] R(j)\i: refers to a set of all variable nodes connected to the verification node j, and then subtracts the variable node i in the set; that is, all other variables except the variable node i in the participating verification equation j variable node.

[0041] L i : Indicates the log likelihood value of the i-th bit of channel information received;

[0042] Λ ji : Indicates the external confidence information passed from check node j to variab...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More