Internal clock gating apparatus

An internal clock, clock technology, used in digital data processing components, instruments, electrical digital data processing, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The making and using of preferred embodiments of the invention are discussed in detail below. It should be appreciated, however, that the present invention provides many applicable inventive concepts that can be embodied in a wide variety of specific contexts. The specific embodiments discussed are merely illustrative of specific ways to make and use the invention, and do not limit the scope of the invention.

[0039] The invention will be described in the context of a preferred embodiment, the internal clock gating means comprising a domino logic clock and a static logic clock. However, the present invention can also be applied to various clock gating circuits.

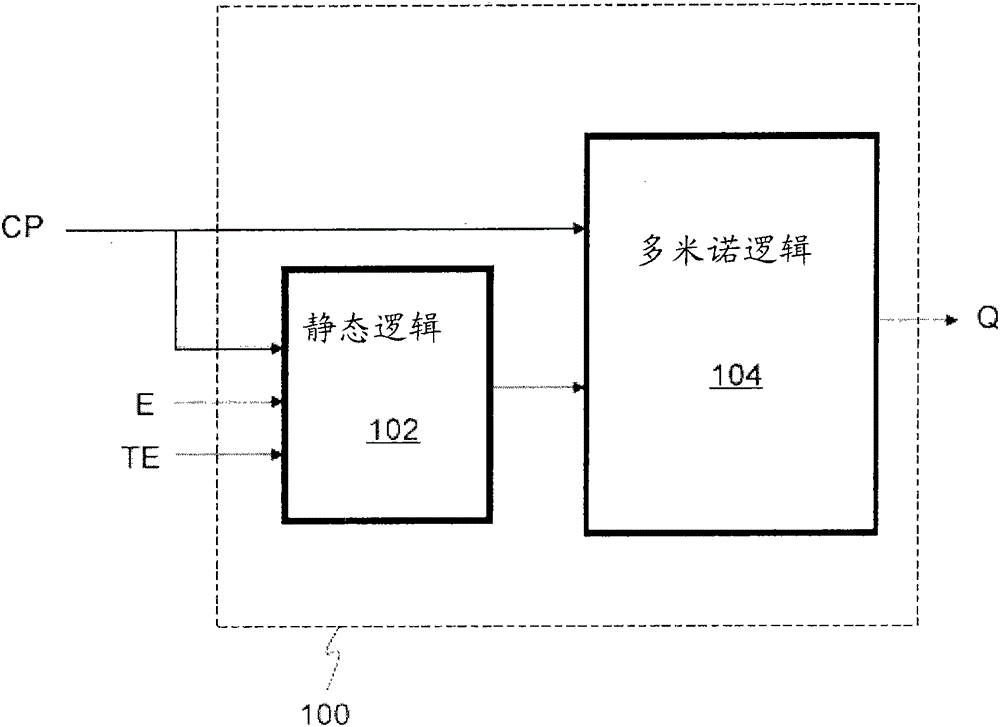

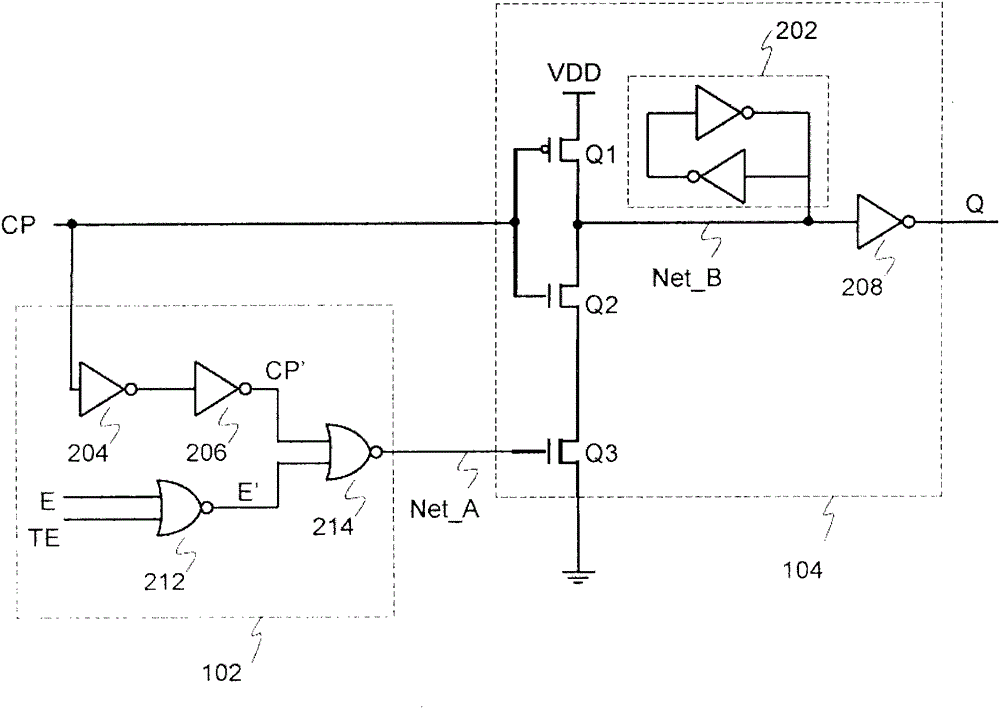

[0040] Initially, referring to figure 1 , shows a block diagram of an internal clock gating device according to an embodiment. The internal clock gating device 100 includes: a static logic module 102 and a domino logic module 104 . The domino logic block 104 includes: a first input connected to the clock s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More