Device and method for improving maintenance efficiency of 283-series digital signal processor

An efficient and series technology, applied in the field of improving the maintenance efficiency of 283 series DSP, it can solve the problems of abnormal CPU operation, reduce product reliability, and leave room for operation, so as to improve program maintenance efficiency, reduce hardware cost, and operate simple and fast. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

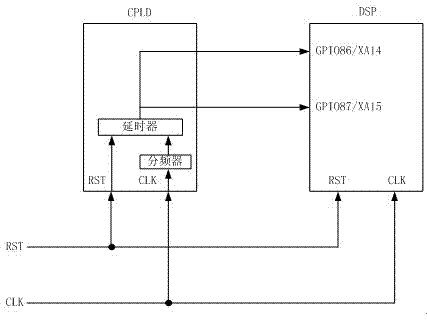

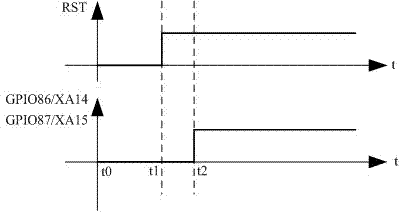

[0020] figure 1 It is the working principle figure of an embodiment of the present invention, and present embodiment device comprises the CPLD that is connected with DSP, comprises frequency divider and time delay device in CPLD; Wherein the input end of frequency divider is connected with the clock input end of DSP; Time delay One input terminal of the delayer is connected to the output terminal of the frequency divider, the other output terminal is connected to the reset input terminal of the DSP, and the output terminal of the delayer is connected to the GPIO86 / XA14 and GPIO87 / XA15 pins of the DSP at the same time. The reset signal RST and the system clock signal CLK are sent to the CPLD and DSP at the same time. Inside the CPLD, firstly, the clock signal with a lower frequency is obtained by dividing the frequency of the clock signal CLK, and then the clock signal with a lower frequency is used to reset the reset signal. RST counts and delays, and sends its output to the p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More