Parallel matrix full-selected primary element Gauss-Jordan inversion algorithm based on multi-core DSP (Digital Signal Processor)

A technology of all-selected pivot and inverse algorithm, which is applied in the field of mobile communication, can solve the problems that the inverse matrix algorithm cannot satisfy all matrices, and cannot meet the requirements of high-speed operation, so as to improve the solution accuracy, fast operation speed, and small memory usage Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

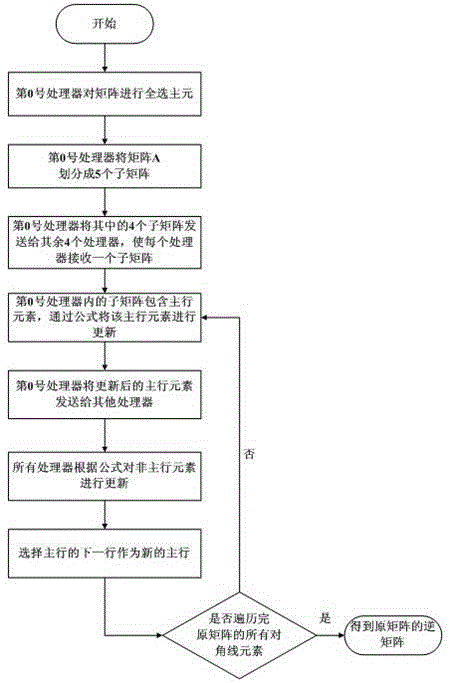

[0042] like figure 1 The parallel matrix inversion algorithm based on multi-core DSP is shown, which is Gaussian Jordan algorithm with all selected pivots, which occupies less memory, has fast operation speed and high precision, and is easy to implement in parallel.

[0043] Each update of the Gaussian Jordan inversion algorithm matrix element is based on the elements on the diagonal, and the elements are updated with different formulas for the elements in different columns, in the same column and different rows, and in different columns and rows. The row where the current diagonal element is located in each update is called the main row, each matrix element on the main row is called the main row element, and the rest of the matrix elements are called non-main row elements.

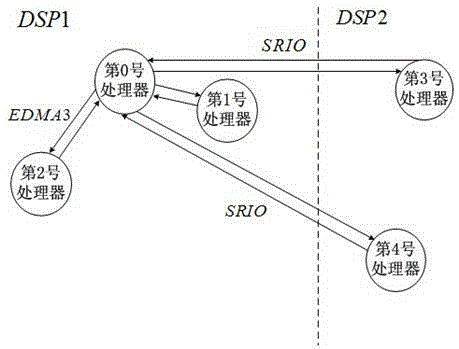

[0044] like figure 1 , 2 As shown, in this embodiment, j=5 block processors are used to invert the matrix A of order n, and the processors are numbered from 0 to 4. Among them, the digital signal proce...

Embodiment 2

[0065] The difference from Example 1 is that steps 3-5 are different.

[0066] The specific implementation of steps 3 to 5 in this embodiment is as follows:

[0067] Step 3: The processor with the main row in the sub-matrix is the No. 1 processor, so the No. 1 processor uses the formula:

[0068]

[0069] and the formula:

[0070]

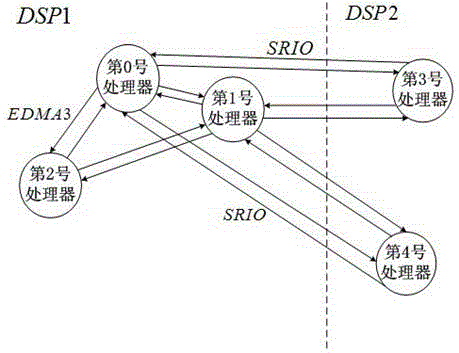

[0071] Update the main row elements, and use EDMA3 to send the updated main row elements to No. 2 processor, and use SRIO to send the updated main row elements to No. 3 and No. 4 processors, where the formula middle is the element value in the sub-matrix, is the element value in the updated sub-matrix, n is the number of sub-matrix rows, j is an integer and 0≤j image 3 As shown, the figure is a communication schematic diagram when the main row element is located in the No. 1 processor sub-matrix.

[0072] Step 4: The other processors use the formula according to the received updated main row element value:

[0073]

[0074] and th...

Embodiment 3

[0080] The difference from Example 1 is that steps 3-5 are different.

[0081] The specific implementation of steps 3 to 5 in this embodiment is as follows:

[0082] Step 3: The processor with the main row in the sub-matrix is the No. 2 processor, so the No. 2 processor uses the formula:

[0083]

[0084] and the formula:

[0085]

[0086] Update the main row elements, and use EDMA3 to send the updated main row elements to No. 1 processor, and use SRIO to send the updated main row elements to No. 3 processors and No. 4 processors.

[0087] Step 4: After receiving the updated value of the main row element, the rest of the processors use the formula

[0088]

[0089] and the formula

[0090]

[0091] Update its sub-matrix, where i is an integer and 0≤i

[0092] Step 5: After the sub-matrix of processor No. 1, processor No. 3 and processor No. 4 is updated, processor No. 1 and processor No. 2 use EDMA3, and processor No. Processor 4 uses SRIO to sen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More