Cache-coherence multi-core processor data transmission system based on no-write allocation

A data transmission system and multi-core processor technology, applied in the direction of electrical digital data processing, instruments, digital computer components, etc., can solve the problems of long access delay and low performance, and achieve the effect of reducing access operations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

[0092] Example 1: Reference Figure 5 ~ Figure 8 , taking a multi-core processor system composed of four processors as an example, the processing of various situations in various operations by a cache coherency protocol based on non-write allocation proposed by the present invention is illustrated.

[0093] Regarding read hit operations, such as Figure 5 Shown: Processor 1 read hit, the state of the cache line may be Exclusive Modified State (ED), Exclusive Clean State (EC), Shared Clean State (SC) or Shared Modified State (SD), at this time processor 1 The cache served data, the state of the cache line is unchanged.

[0094] Regarding read miss operations, such as Image 6 Shown: Processor 1 reads a miss, needs to get data, and allocate the cache line. Processor 1 sends a read miss request. After processors 2, 3, and 4 receive the read miss request, they check their respective caches. If there is no valid cache line or the cache line is in the shared clean state (SC), giv...

example 2

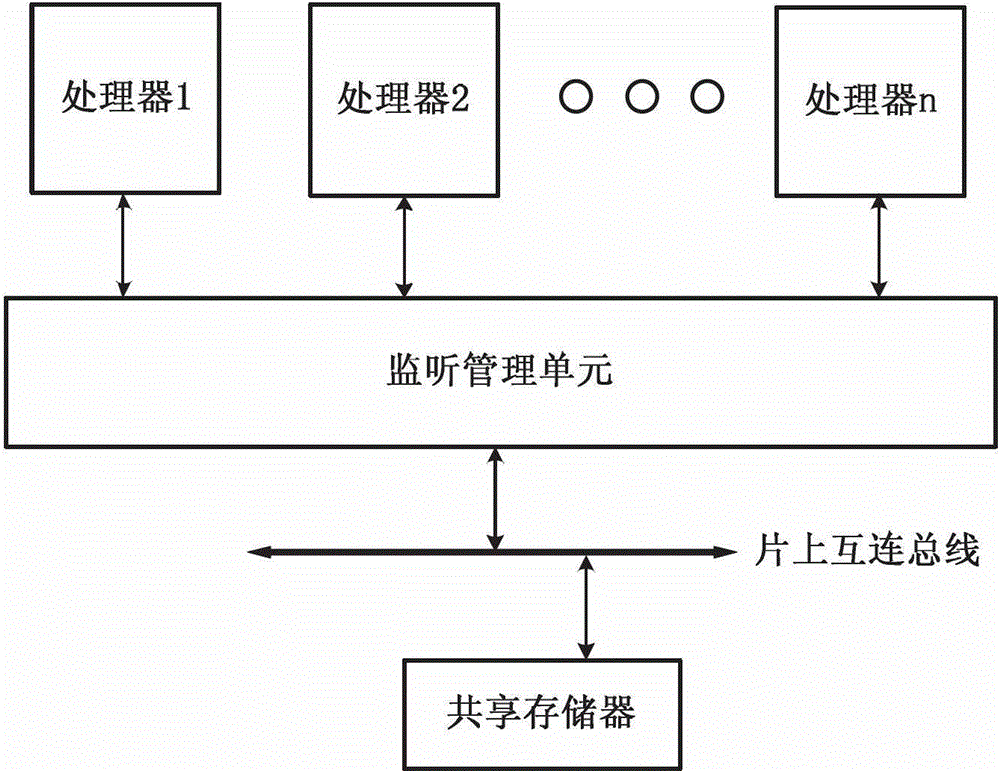

[0097] Example 2: Reference Figure 9 , taking a multi-core processor system composed of four processors as an example, the workflow of a hardware device for implementing the non-write allocation-based cache coherency protocol proposed by the present invention is described.

[0098] Such as Figure 9 As shown, when processor 1 generates a read miss, write miss or write hit in a cache line in a shared state (SD or SC), it will perform the following steps.

[0099] In the first step, the processor 1 sends a consistency message to the monitoring management unit through the consistency request interface. Among them, the consistency request interface includes: a consistency request signal, used to indicate whether the consistency request is valid; a consistency type signal, used to indicate whether the consistency operation is a write hit, a write miss, or a read miss; an address signal, used to indicate On which address the processor generates a consistency request; write data s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More