Forming method of grid electrode

A grid and gate electrode technology, which is applied in the photoplate making process of the pattern surface, microlithography exposure equipment, optics, etc., can solve the problem of shortening of the line end, and achieve the effect of improving the yield rate and improving the shortening of the line end

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

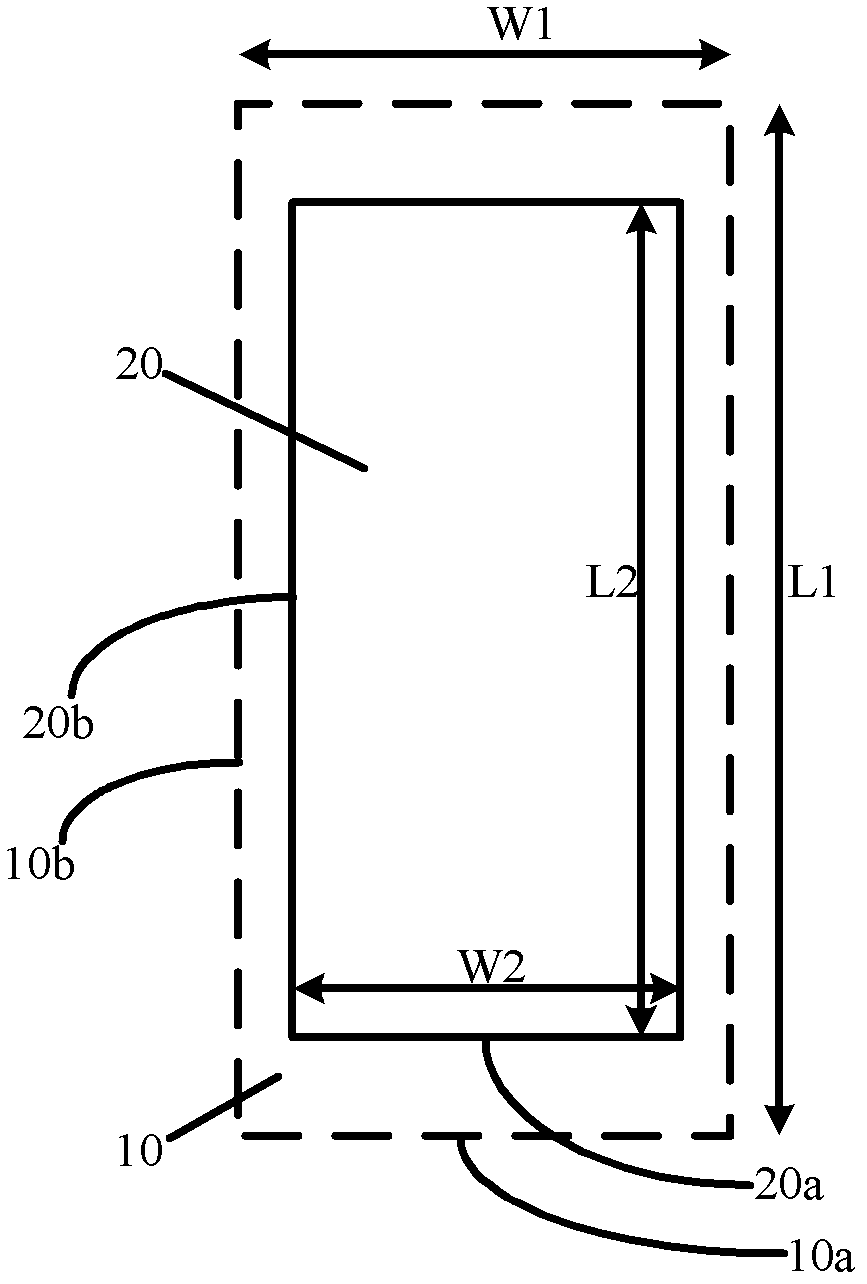

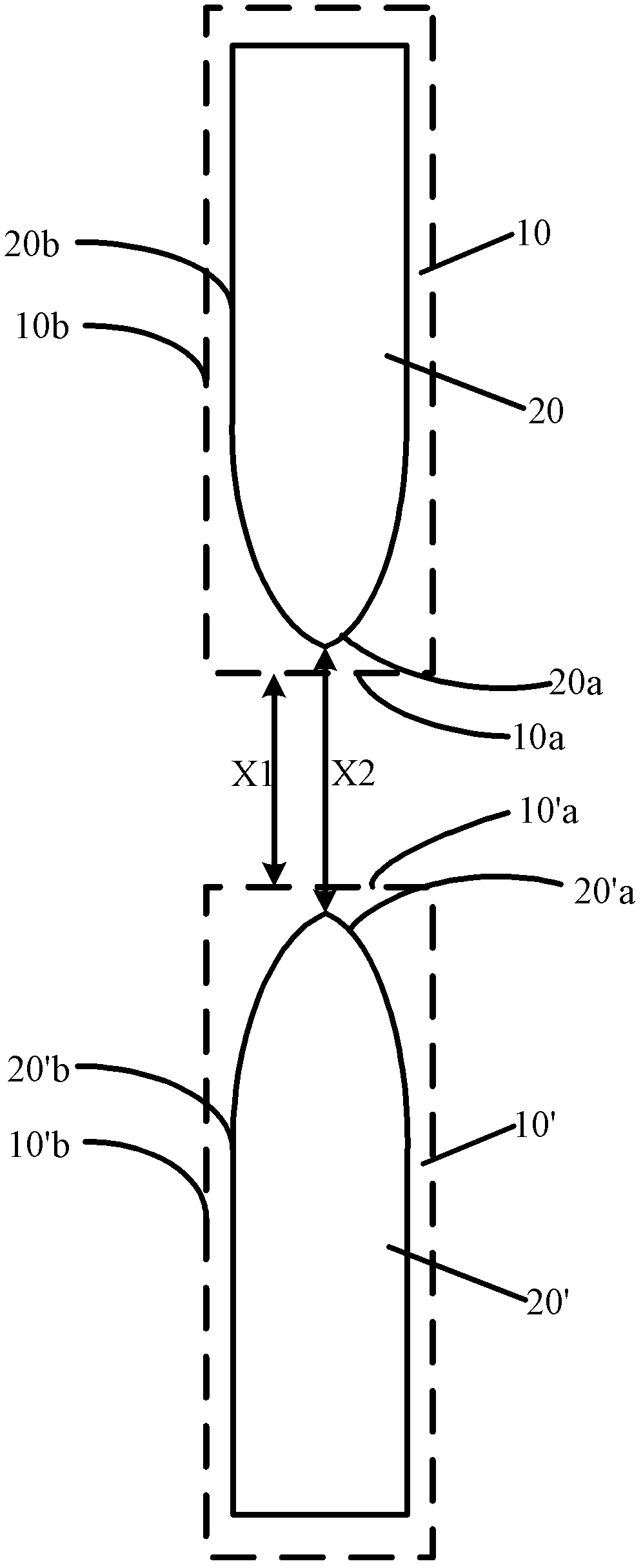

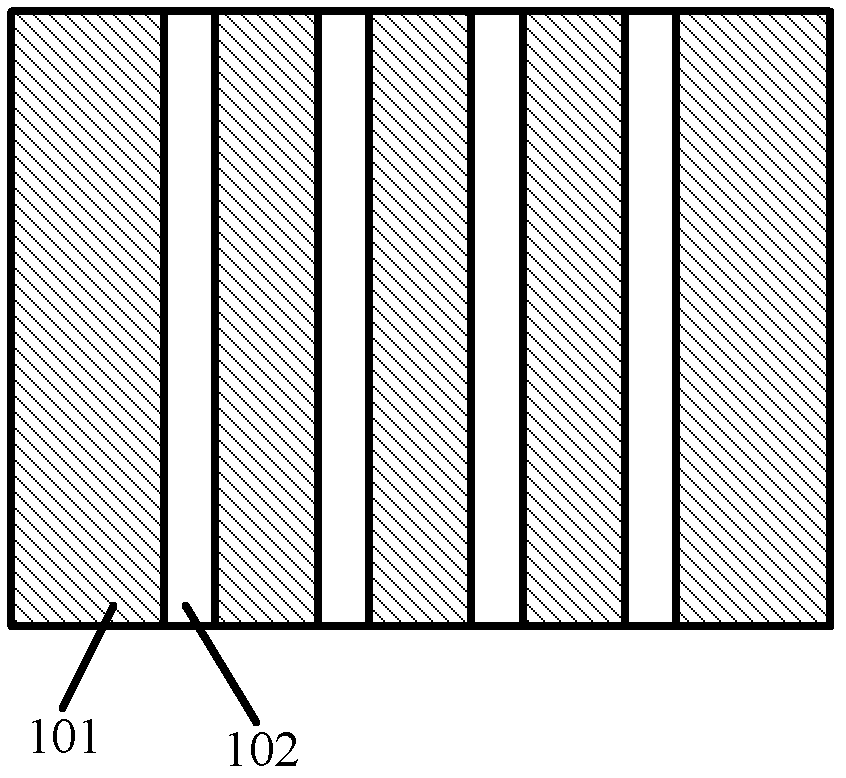

[0036] As mentioned in the background art, in the etching process of the prior art to form the gate, there will be a more obvious problem of shortening of the line ends. As the feature size (CD, Critical Dimension) of semiconductor devices becomes smaller and smaller, double patterning Forming the gate by the method can prevent the end of the line and the side end of the line from being etched at the same time, but the problem of shortening the end of the line has not been effectively solved.

[0037] In order to improve the problem of shortening of the line ends in the process of forming the gate by etching, the present invention provides a method for forming the gate.

[0038] In order to make the above objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0039] In the following description, specific details are set fo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More