Method for forming gate electrode

A gate and gate layer technology, applied in semiconductor devices and other directions, can solve problems such as shortening of wire ends, and achieve the effect of improving yield and shortening wire ends

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] In order to make the above objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0036] In the following description, specific details are set forth in order to provide a thorough understanding of the present invention. However, the present invention can be implemented in many other ways than those described here, and those skilled in the art can make similar extensions without departing from the connotation of the present invention. Accordingly, the present invention is not limited to the specific embodiments disclosed below.

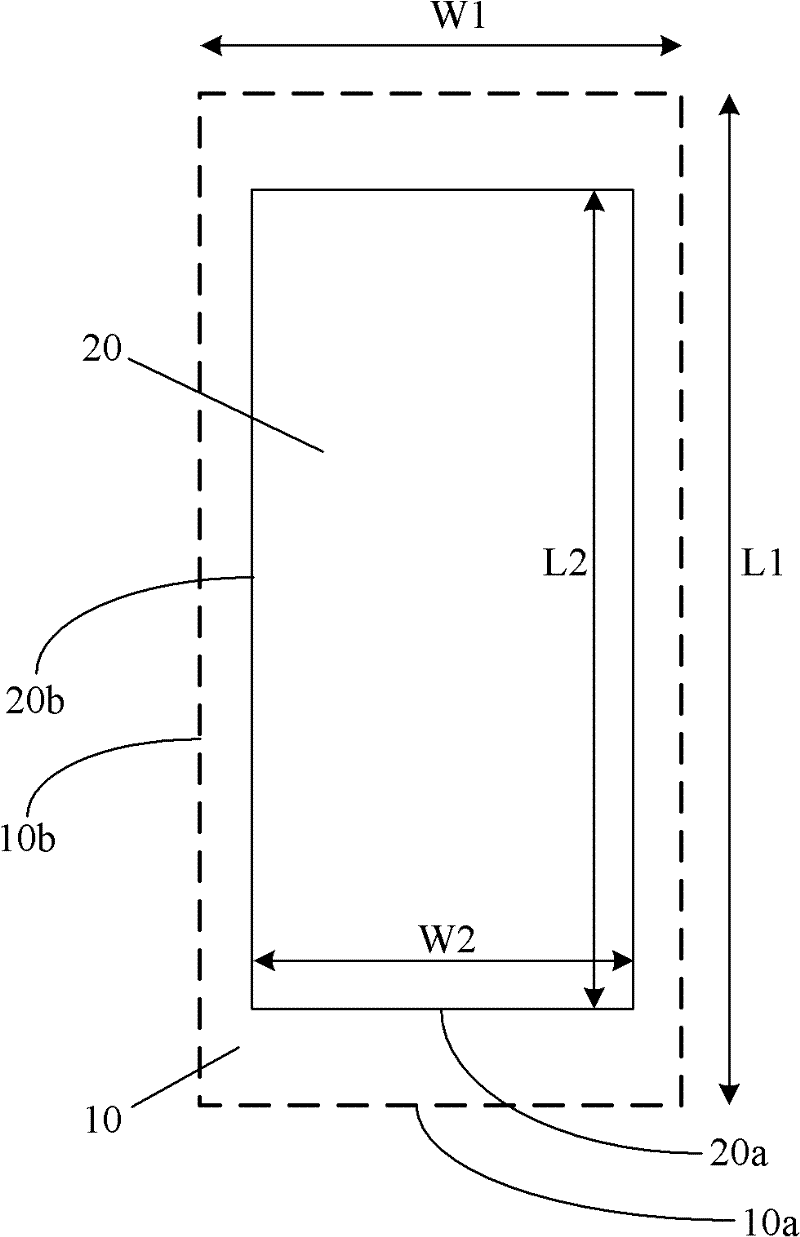

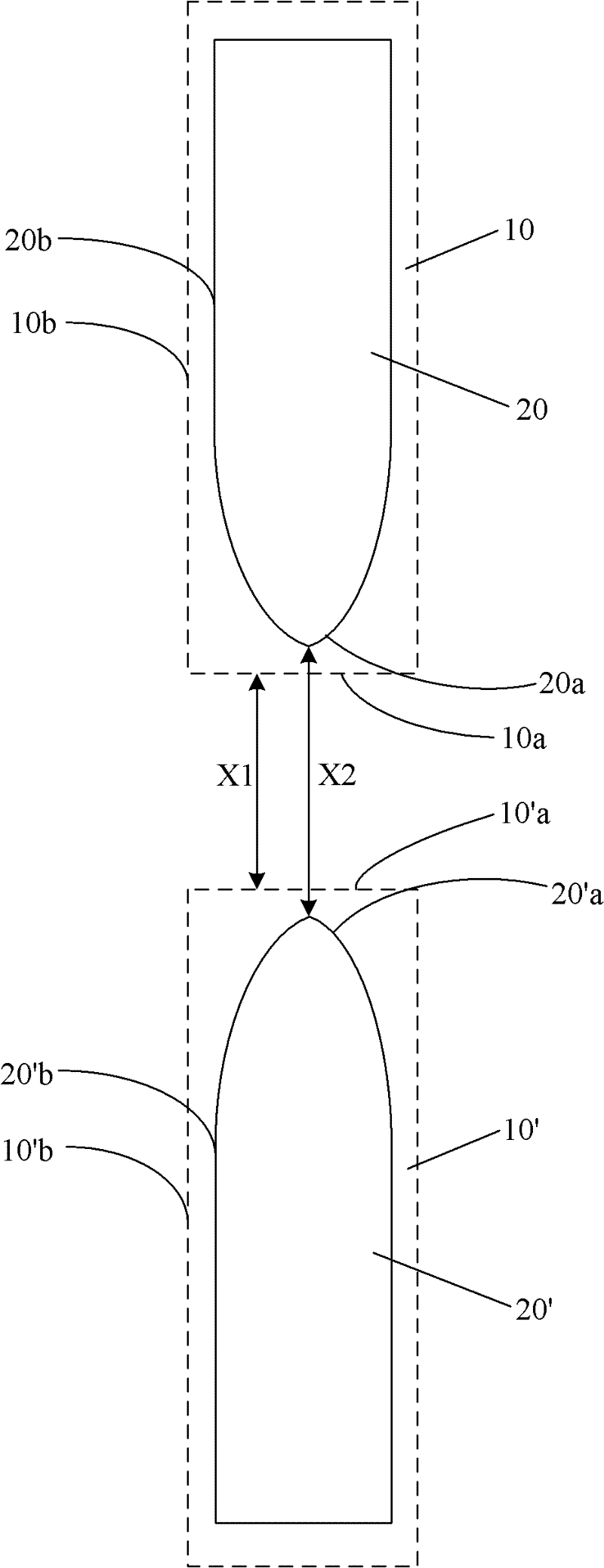

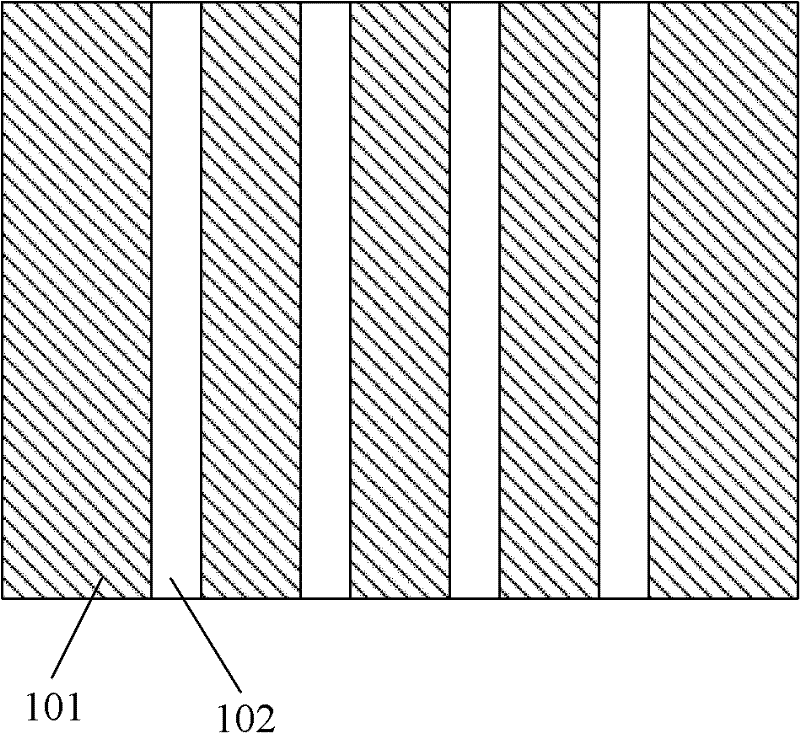

[0037]In the gate formation process of etching in the prior art, there will be a more obvious problem of line terminal shortening. As the feature size (CD, Critical Dimension) of semiconductor devices becomes smaller and smaller, even if the gate is formed by double patterning, Although it...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More