Compact charge transfer refresh circuit and refresh method thereof

A charge transfer, compact technology, applied in the field of memory, which can solve the problems of low data accessibility of memory, complex switching mechanism, complex inductive switch controller, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

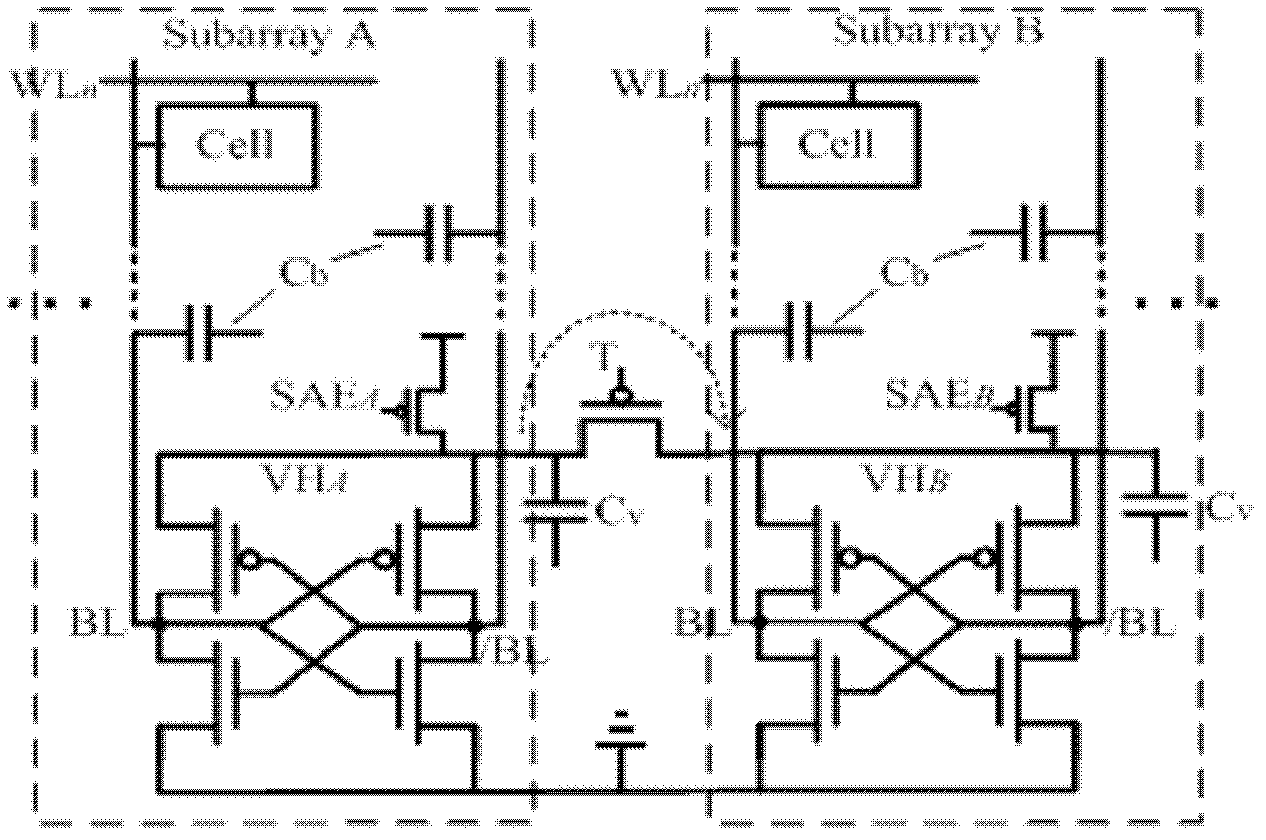

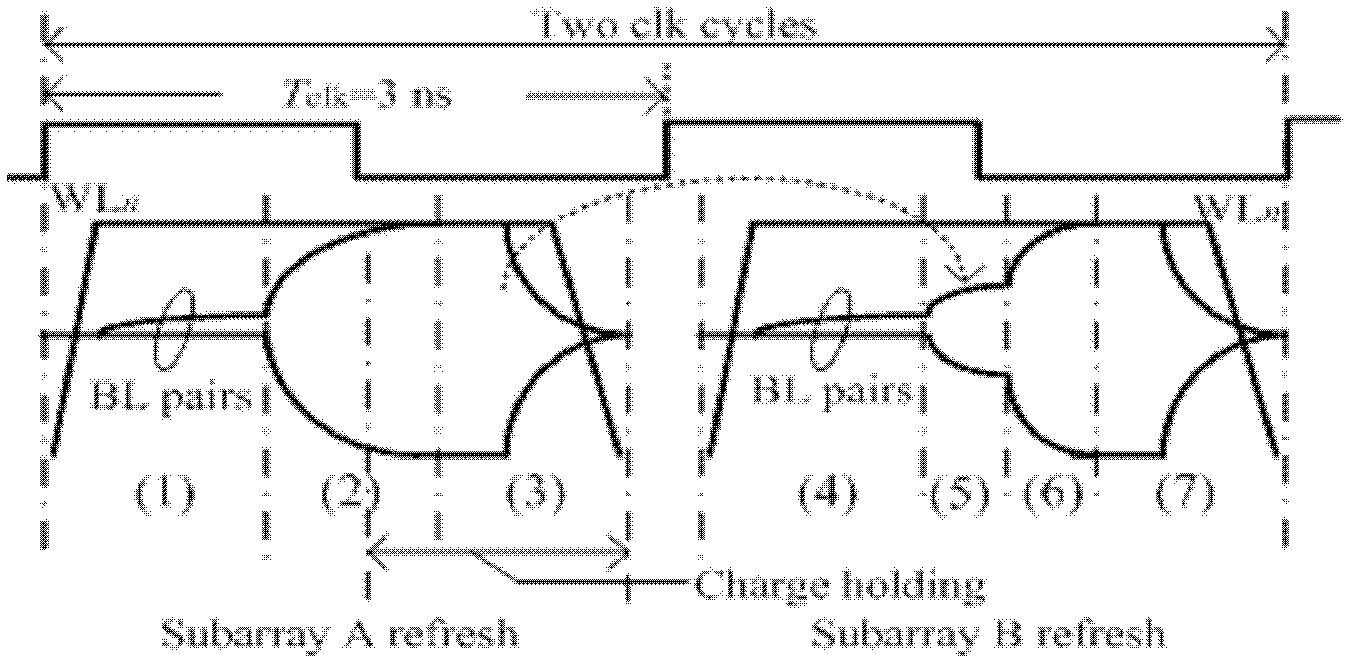

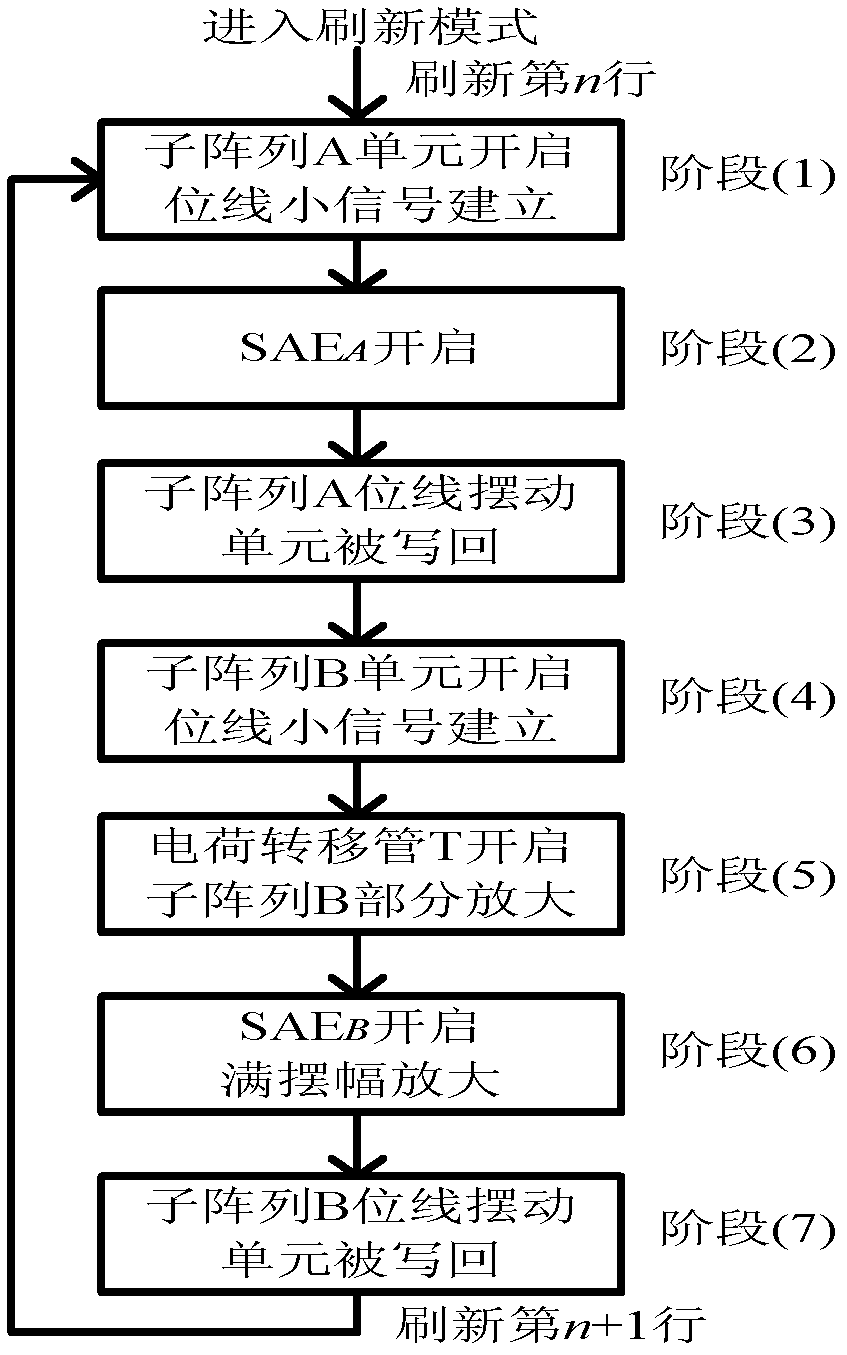

[0032] attached Figure 4 It is a schematic diagram of a compact charge transfer refresh circuit according to an embodiment of the present invention. Divide the array with a size of 128×256 into four 128×64 sub-arrays in the column direction (each sub-array is numbered 1~n), and all the sense amplifiers of each sub-array are connected to the virtual power supply terminals, which are denoted as VHn, and the sub-arrays are The virtual power terminal VHn is connected through the charge transfer switch Tn. As an example, only sub-arrays A, B, C, D are shown in the figure. It is worth noting that the embodiment here only exemplifies that the array with a size of 128×256 is divided into four 128×64 sub-arrays (each sub-array is numbered 1-n) in the column direction, and those skilled in the art can understand that it is not limited to Therefore, it can be extended to general arrays. For example, an array with a size of M*N is divided into t M×(N / t) subarrays (each subarray is numb...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More