Chip with scan chain test function and test method

A scanning chain and chip technology, applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc., can solve the problems that the circuit cannot be completely tested, reduce the scanning test coverage of the chip combination circuit, and cannot change the excitation signal, etc., to achieve reduction Effects of occupancy, increased coverage, time saved

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment 1

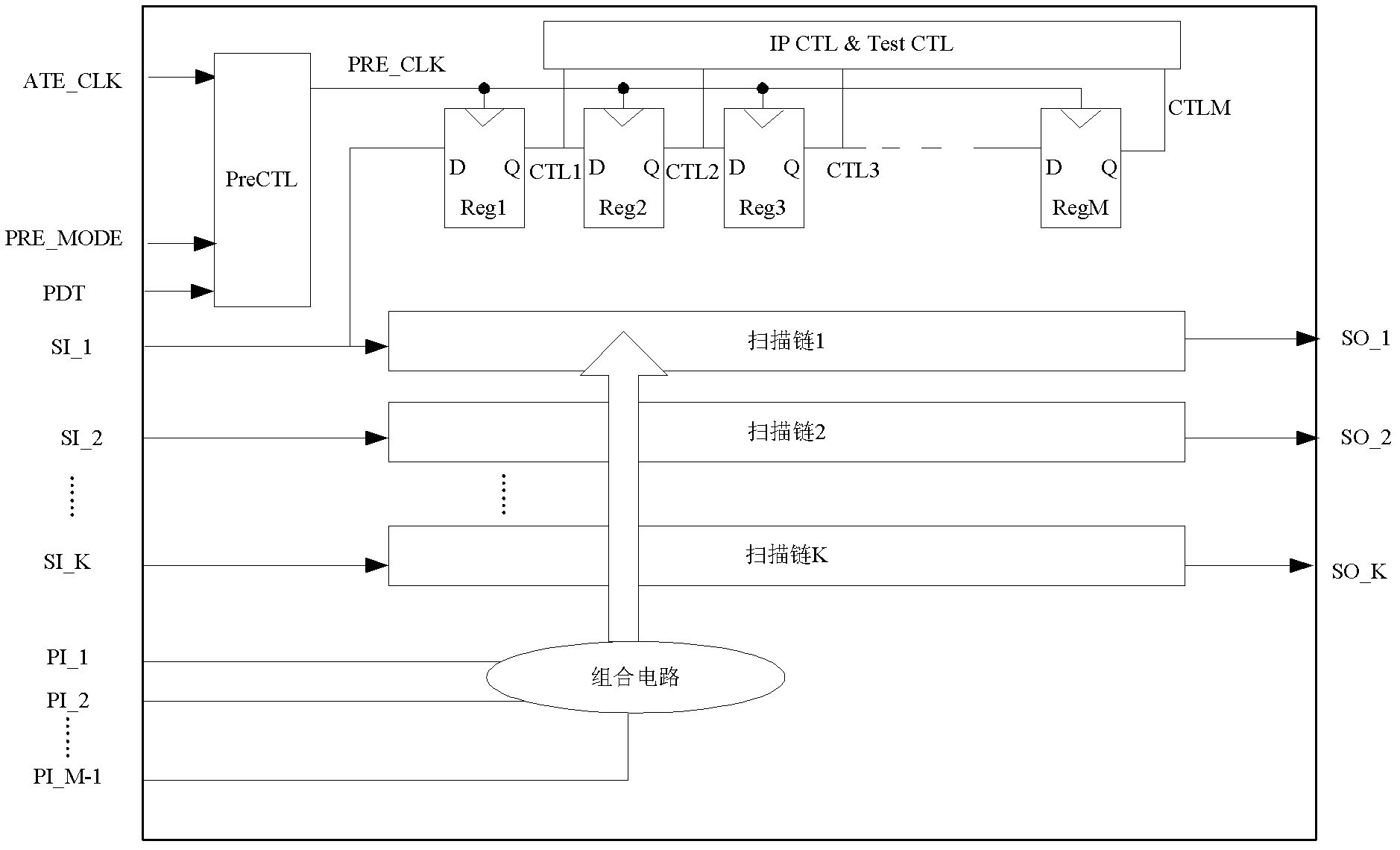

[0055] This embodiment is a preferred implementation of the chip with scan chain test function of the present invention, the specific structure is as follows image 3 shown, including:

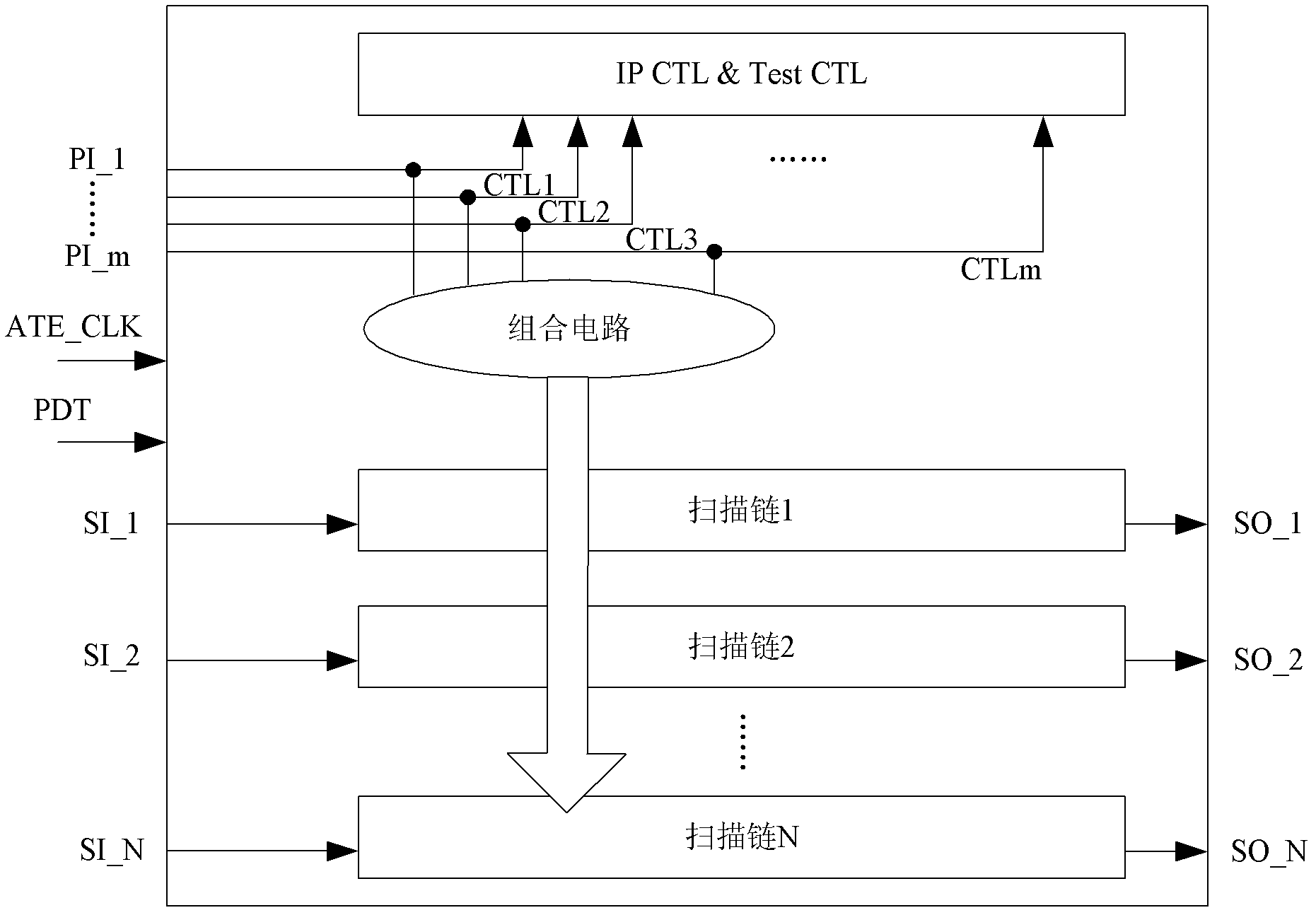

[0056] Test mode and function module parameter configuration module (IP CTL & Test CTL), combined circuit, multiple scan chains (for example, K scan chains, scan chain 1 to scan chain K); and:

[0057] The parameter latching trigger chain is composed of multiple (m) flip-flops (Reg1~Regm) connected in series, and is used to receive and latch test mode parameters and function module configuration parameters; the previous trigger in the trigger chain The data output terminal Q of the flip-flop is connected to the data input terminal D of the next flip-flop; the data output terminals of each flip-flop are respectively connected to the control value input terminals CTL1~CTLm of IP CTL & Test CTL; provide test mode for IP CTL & Test CTL And function module parameter control value; The clock input ...

specific Embodiment 2

[0070] This embodiment is a preferred implementation manner of the chip with scan chain testing function of the present invention.

[0071] The chip in this embodiment includes all the modules of the chip in Embodiment 1. At the same time, the data output end of the parameter latch flip-flop chain, that is, the data output end Q of the last flip-flop is also coupled to a pin of the chip.

[0072] In this way, after the parameter setting control module turns on the clock of each trigger of the parameter latch trigger chain, before configuring the test mode and function parameters, each trigger in the parameter latch trigger chain can be tested. The specific test method is: Under the control of the scan clock, the test vectors are moved into the parameter latching flip-flop chain one by one through the chip pins connected to the data input end of the first flip-flop in the parameter latching flip-flop chain, and the last flip-flop in the parameter latching flip-flop chain The ou...

specific Embodiment 3

[0077] This embodiment is a preferred implementation of the chip testing method with scan chain testing function of the present invention, the specific process is as follows Figure 8 shown, including:

[0078] 1. The parameter setting control module outputs the scan clock signal to each trigger clock input end of the parameter latch trigger chain;

[0079] 101. Set the PDT pin of the chip to 1 (valid), and enter the scan test;

[0080] 102. Set the pin connected to PRE_MODE to 1 (valid), and the parameter setting control module outputs the scan clock signal to each trigger clock input end of the parameter latch trigger chain through PRE_CLK;

[0081] 2. Under the control of the scan clock, the test mode and the parameter control value of the function module are serially moved into each flip-flop of the parameter latch flip-flop chain;

[0082] 3. The parameter setting control module closes the scan clock signal output, and each trigger output terminal of the parameter latch...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More