Manufacturing method of high voltage isolating N type laterally diffused metal oxide semiconductor (LDMOS) component

A manufacturing method, high-voltage isolation technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problem of high cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

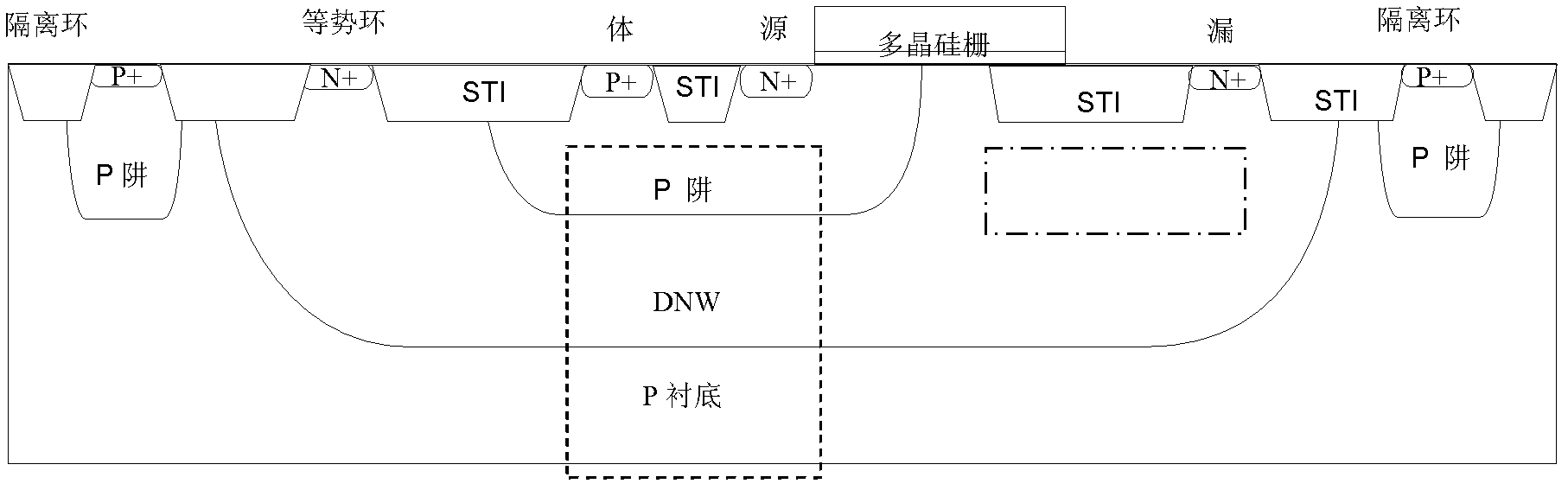

[0039] An embodiment of the manufacturing method of the high-voltage isolation N-type LDMOS device of the present invention is as follows Figure 2 to Figure 10 shown, including the following steps:

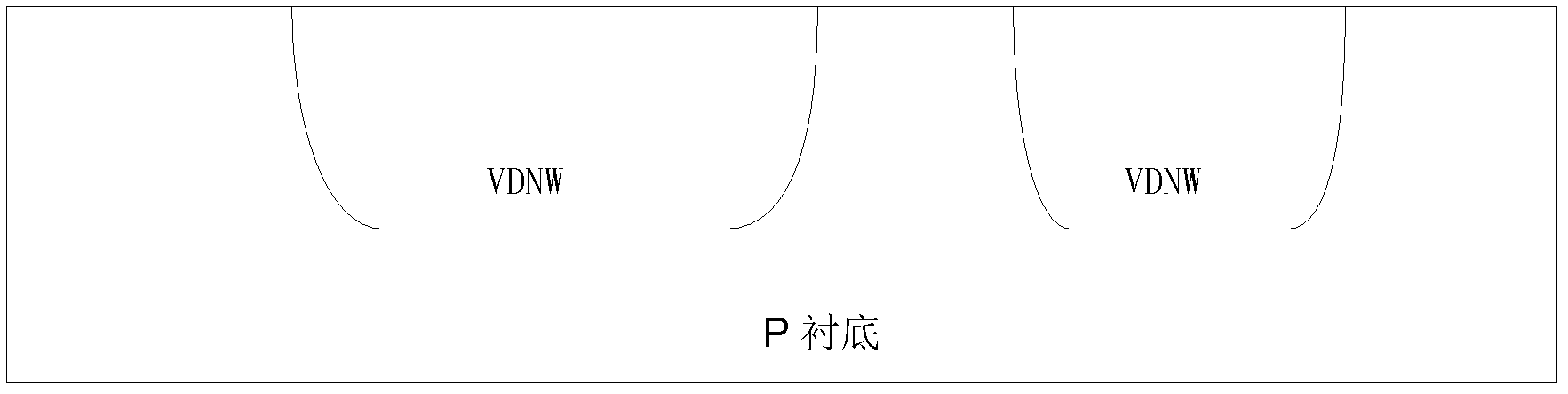

[0040] 1. Form a masking film on the P-type silicon substrate, etch the masking film to the upper surface of the silicon substrate, and form two very deep N-type wells on the left and right VDNW ion implantation selection windows, and the formed two very deep N-type wells on the left and right The width W of the masking film between the ion implantation selection windows is greater than 2um, such as figure 2 shown;

[0041] 2. Perform N-type ion implantation at the first concentration, such as 6E12 to 1E13 ions / CM 2 , Phosphorus ion implantation with an energy of 1000Kev~2000Kev, such as figure 2 shown;

[0042] 3. Diffusion of N-type ions of the first intensity, such as phosphorus ion diffusion at a temperature of 1100°C to 1200°C for 5 to 10 hours, to form two very deep N...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Width | aaaaa | aaaaa |

| Width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More