High voltage isolated n-type ldmos device and method of manufacturing the same

A high-voltage isolation, N-type technology, used in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problem of high cost, achieve the effect of performance improvement, simple and flexible process, and cost reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

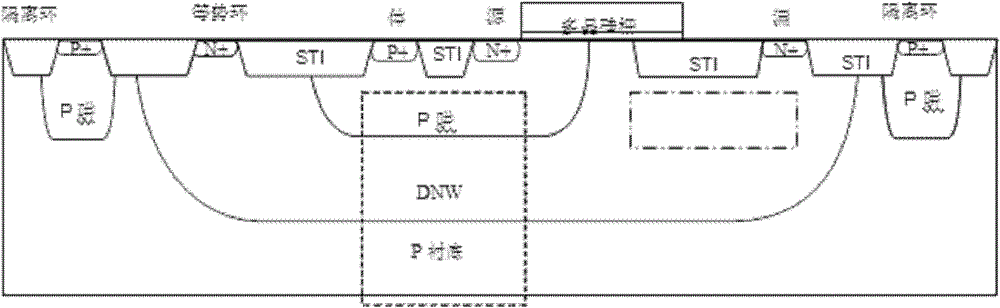

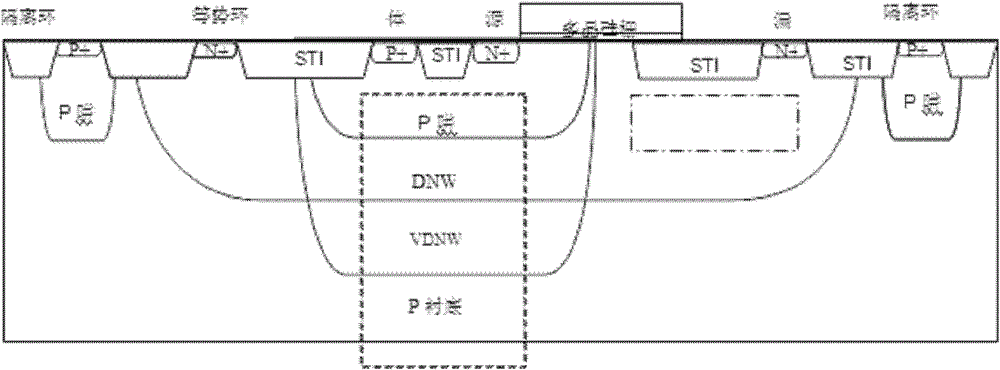

[0028] An embodiment of the high-voltage isolation N-type LDMOS device of the present invention is figure 2 As shown, a deep N-type well DNW is formed on the P-type substrate, and a very deep N-type well VDNW deeper than the deep N-type well DNW is formed in the deep N-type well DNW. A P-type well is formed in the N-type well VDNW, a polysilicon gate is formed above the adjacent region of the P-type well and the deep N-type well DNW, and a polysilicon gate is formed on the P-type well located on one side of the polysilicon gate. The source terminal and the body terminal are formed with a drain terminal on the deep N-type well on the opposite side of the polysilicon gate. figure 2 In the dotted line area is the PNP (Pbody-DNW-P type substrate) structure in the vertical direction, and the dotted line area is the drain terminal N-type drift region (draindrift).

[0029] Preferably, the depth of the deep N-type well is one-third to three-quarters of the depth of the very deep N...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More