Optimization method of capturing power consumption in scan test

An optimization method and scanning test technology, applied in the direction of generating/distributing signals, can solve the problems of increasing test design complexity and prolonging test time, and achieve the effect of reducing capture power consumption and being easy to implement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The present invention will be described in further detail below in conjunction with the accompanying drawings.

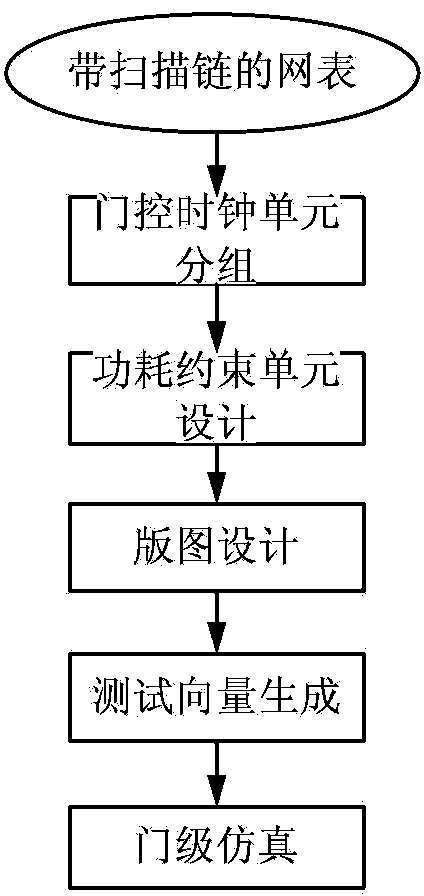

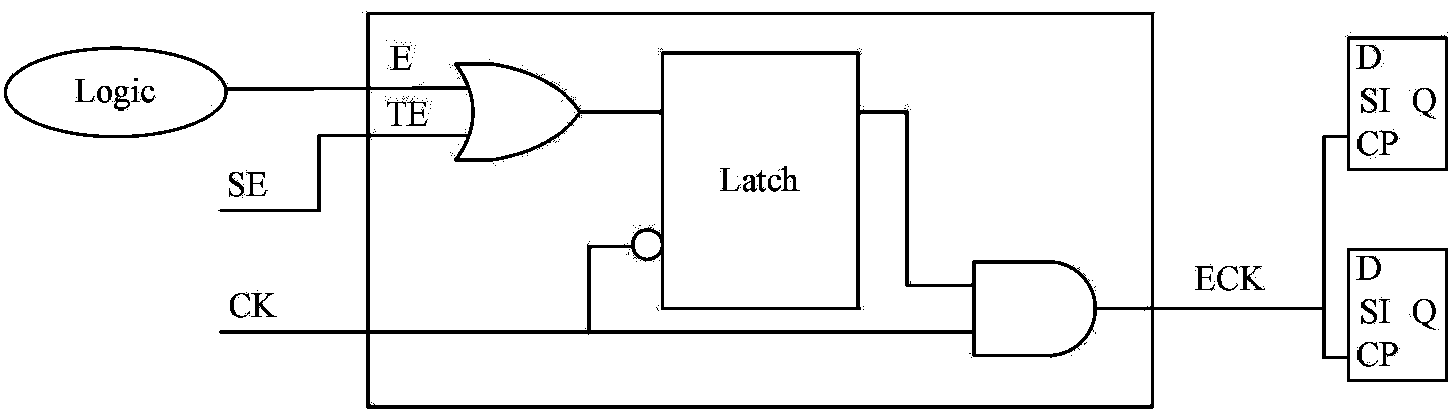

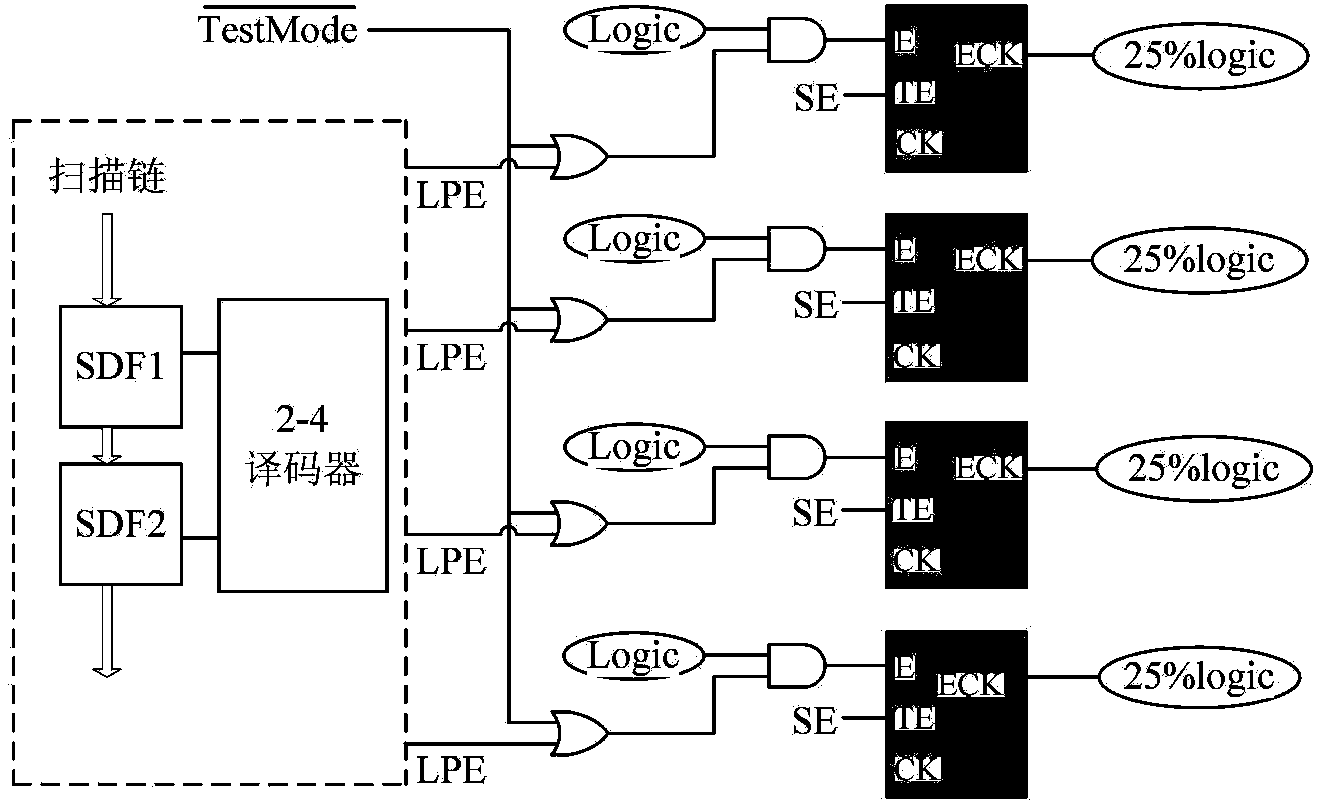

[0022] The invention analyzes the test power consumption of each part in detail, focuses on reducing the capture test power consumption, and finally provides a low power consumption test scheme based on the power consumption optimization of the gating clock. On the basis of the basic test flow, the present invention adds two steps of gate control clock unit grouping and power consumption constrained unit design, the technical scheme is as follows figure 1 As shown, the overall process is as follows:

[0023] (1) Generate a netlist with a scan chain. Described as follows:

[0024] ① Carry out testability analysis on the RTL code of the chip, and modify the RTL code of the chip.

[0025] ② Use the process library provided by the process manufacturer to map the modified RTL code into a gate-level netlist, and at the same time, according to the design constrai...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More