Method of achieving high-definition transmission of videos

A video and high-definition technology, applied in digital video signal modification, TV, electrical components, etc., can solve problems such as poor video quality and poor real-time performance, and achieve the effects of reducing the amount of calculation, improving efficiency, and ensuring quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

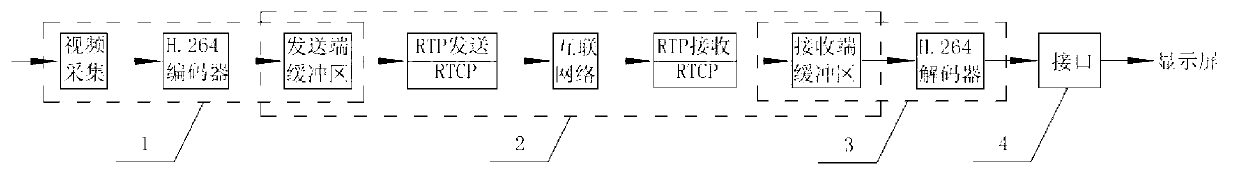

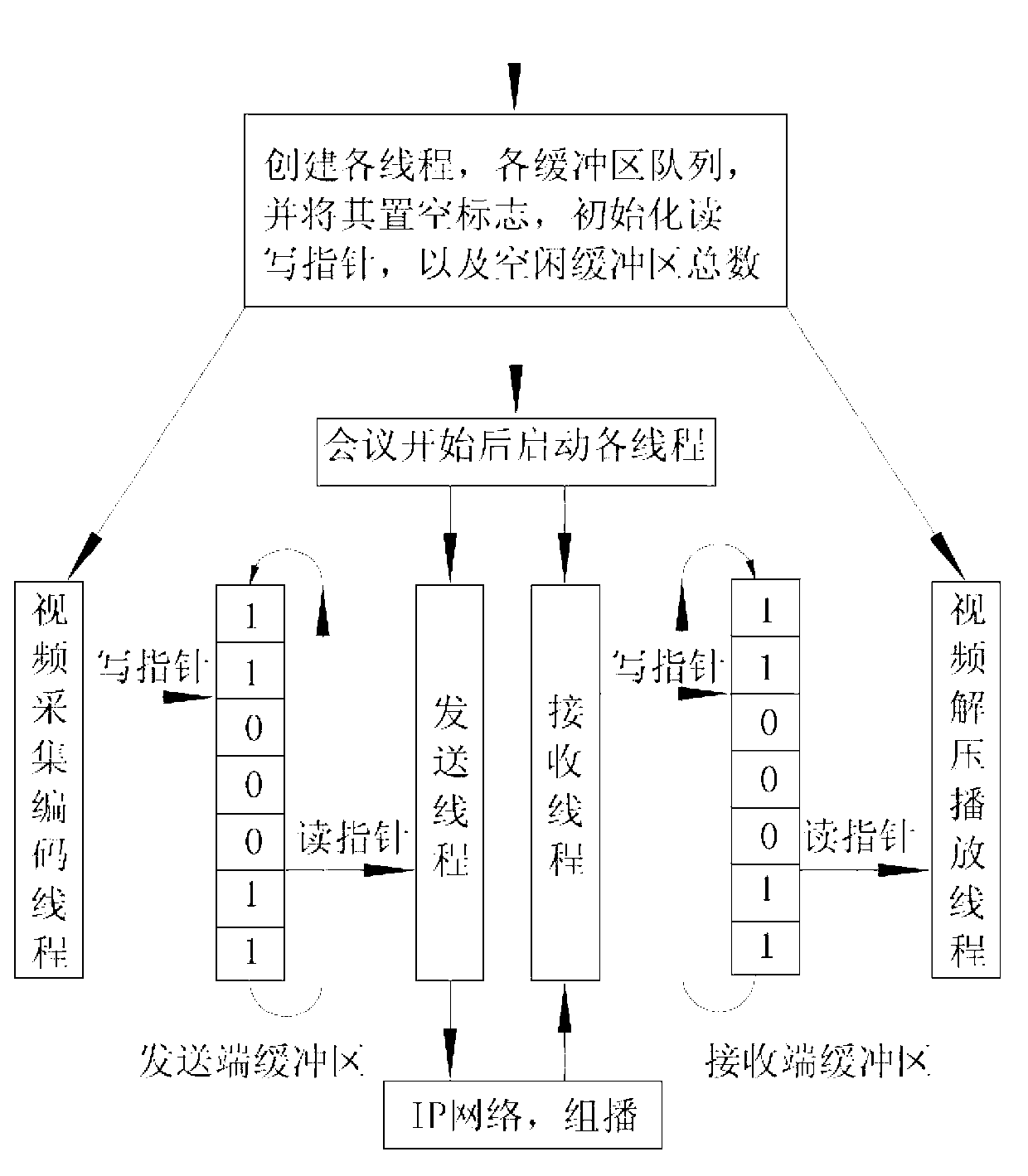

[0042] refer to figure 1 , figure 2 with image 3 , where the CPU is IntelCore2Q9400, the main frequency is 2.66GHz, and the memory is 3G; the GPU is GeForceGT425M (128bit memory interface, core frequency 1120MHz, memory frequency 800MHz, memory bandwidth 25.6GB / s). In double-buffer multi-threaded operation, the buffer block structure is defined as follows:

[0043]

[0044] Among them, link is the connection pointer of the buffer block in the buffer; data is the pointer pointing to the current buffer block.

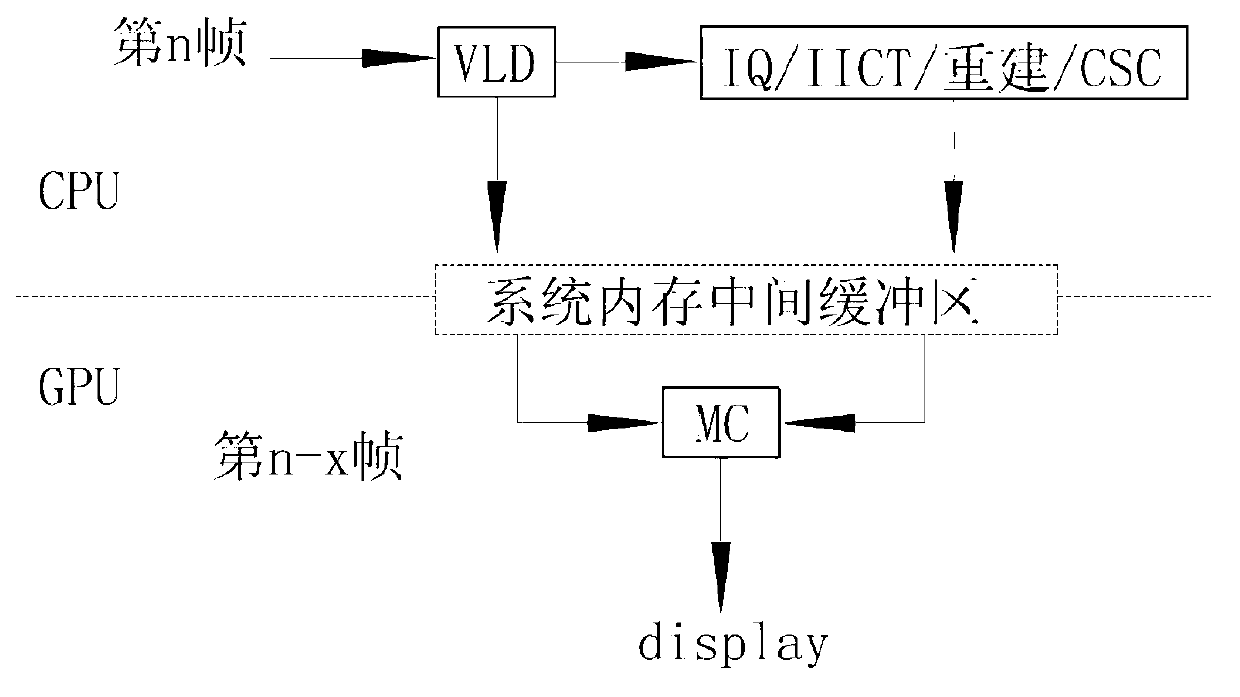

[0045] use figure 2 The shown level 1 is decoded based on the CPU+GPU parallel decoding architecture of H.264.

[0046] Under the above conditions, a 720x576 video sequence was selected for testing, 300 frames were extracted, and repeated 800 times, and the average time-consuming of each frame of MC was counted. Compared with the traditional CPU algorithm, the algorithm of the present invention has an overall acceleration ratio of 9.6 times, and the video quali...

Embodiment 2

[0048] refer to figure 1 , figure 2 with Figure 4 , the CPU is IntelCore2DuoCUPE8400, the main frequency is 3.0GHz, and the memory is 1.9G; the GPU is GeForceGT425M (128bit memory interface, core frequency 1120MHz, memory frequency 800MHz, memory bandwidth 25.6GB / s). The definition of the buffer block structure in the double-buffer multi-thread operation is the same as the real-time example 1. use image 3 The shown level 4 is decoded based on the CPU+GPU parallel decoding architecture of H.264. Under the above conditions, a 1280x720 video sequence was selected for testing, 200 frames were extracted, and the execution was repeated 1000 times, and the average time-consuming was counted. Compared with the traditional CPU algorithm, the algorithm of the present invention has an overall speed-up ratio of 8.5 times; and the video quality is clear, effectively realizing the high-definition and real-time transmission of the video.

Embodiment 3

[0050] refer to figure 1 , figure 2 with Figure 5 , the CPU is IntelCore2DuoCUPE8400, the main frequency is 3.0GHz, and the memory is 1.9G; the GPU is NVIDIAGeForceGTX460 (256bit memory interface, core frequency 1350MHz, memory frequency 3600MHz, memory bandwidth 115.2GB / s). The definition of the buffer block structure in the double-buffer multi-thread operation is the same as [Embodiment 1]. use Figure 5 The shown level 3 is decoded based on the CPU+GPU parallel decoding architecture of H.264. Under the above conditions, a low-resolution video sequence with a resolution of 352x288 and a video sequence with a high resolution and a very violent motion were selected for testing, and 200 video sequences were extracted from each video sequence. Frames are executed repeatedly 1000 times, and the average time-consuming is counted. Adopting the algorithm of the present invention compared with the traditional CPU algorithm, for the video sequence of 352x288, the overall speed-...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More