Data processing method and data processing device

A data processing and data technology, applied in the field of communication, can solve problems affecting FPGA processing performance, achieve the effect of reducing the use of memory resources, improving processing efficiency, and improving processing performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

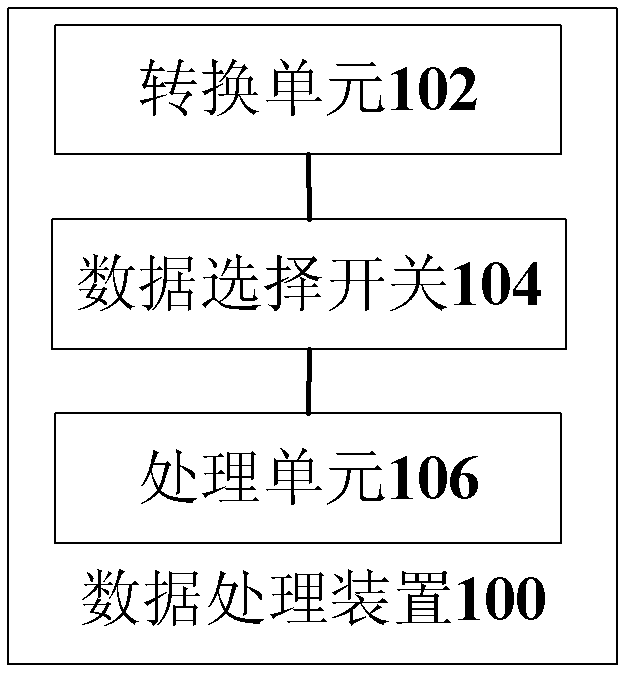

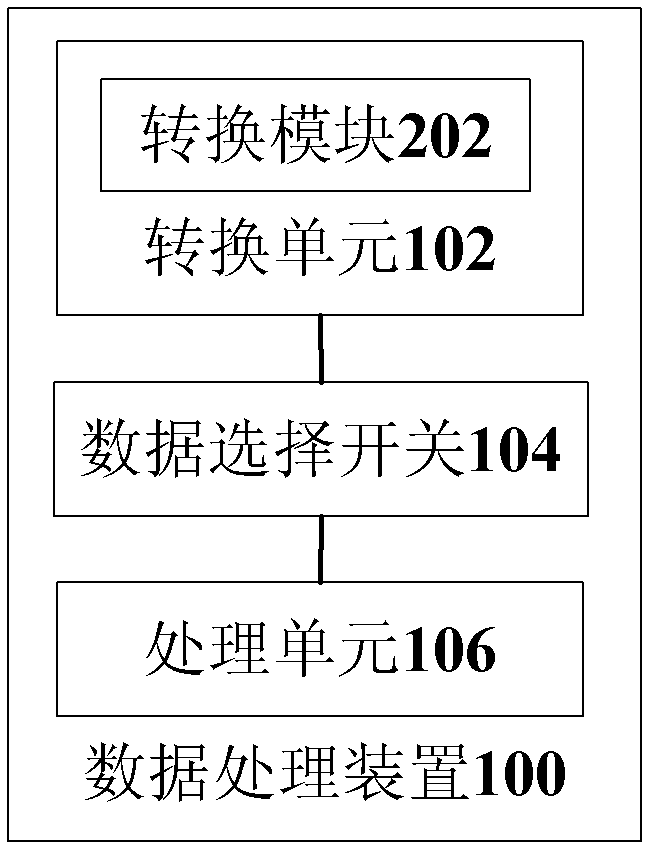

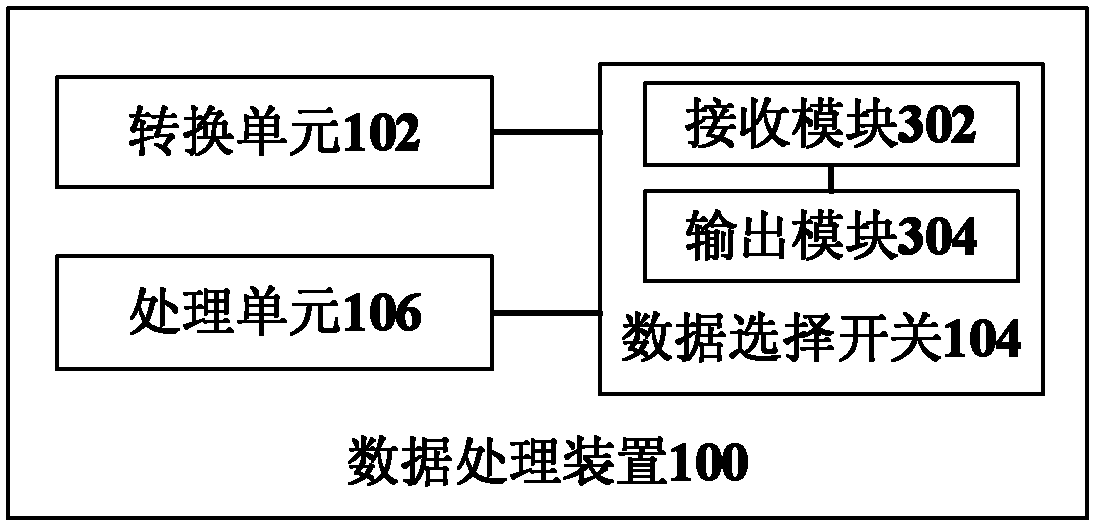

[0030] Such as figure 1 As shown, the present invention provides a preferred data processing device 100, which includes: a conversion unit 102, which is used to convert a plurality of serially input data into multiple parallel input data through a multi-way delay shift register ; The data selection switch 104 is used to select data to be processed from multiple channels of parallel input data; the processing unit 106 is used to perform calculation processing on the selected data to be processed.

[0031] In the above-mentioned preferred embodiment, by converting the serial input data into parallel input data through the delay shift register, the serial data is delayed and output through the delay shift register, thereby realizing the need not to use a special memory unit To save the data to be calculated, the purpose of reducing the use of FPGA memory resources is achieved, and the processing performance of the FPGA is improved; at the same time, the data to be processed is se...

Embodiment 2

[0041] based on Figure 1-4 As shown in the preferred data processing device, the present invention also provides a preferred data processing method, such as Figure 5 As shown, the specific steps of the method include:

[0042] S502: Convert multiple serially input data into multiple parallel input data through multiple delay shift registers;

[0043] S504: Select the data to be processed from multiple parallel input data through the data selection switch;

[0044] S506: Perform calculation processing on the selected data to be processed.

[0045] In the above-mentioned preferred embodiment, by converting the serial input data into parallel input data through the delay shift register, the serial data is delayed and output through the delay shift register, thereby realizing the need not to use a special memory unit To save the data to be calculated, the purpose of reducing the use of FPGA memory resources is achieved, and the processing performance of the FPGA is improved; ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More