System and method for realizing plc high-speed pulse counting based on fpga

A high-speed pulse and system realization technology, applied in the field of PLC counting, can solve the problem of consuming large FPGA lookup table resources, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

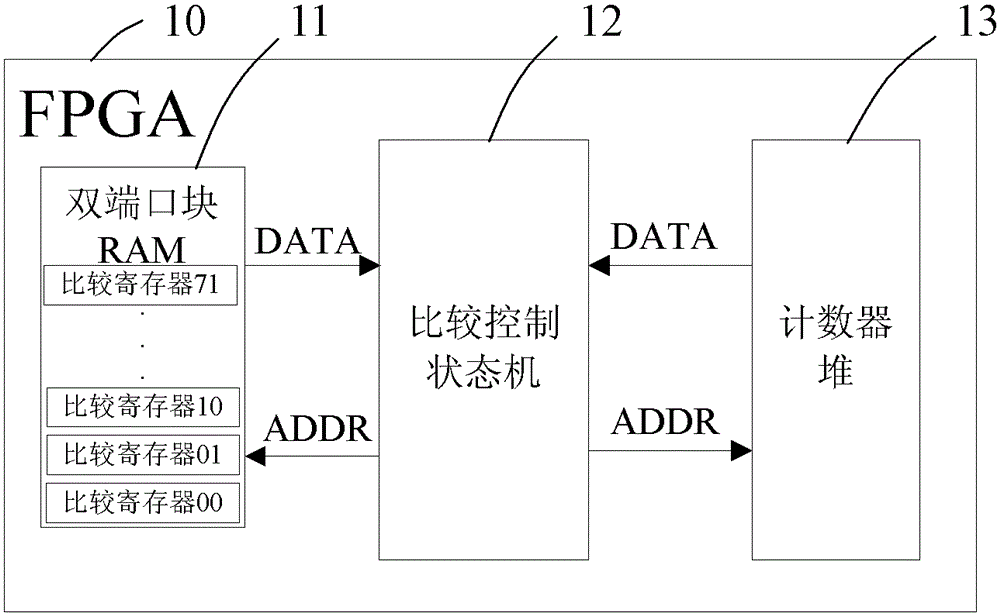

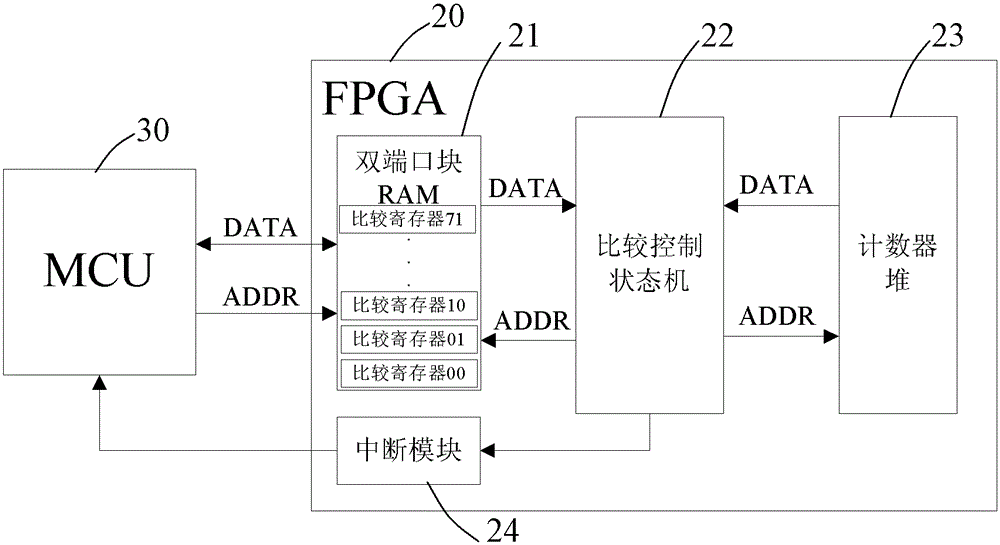

[0025] Such as figure 1 Shown is a schematic diagram of the first embodiment of the FPGA-based PLC high-speed pulse counting realization system of the present invention. The system includes an FPGA 10 including a dual-port block RAM 11 , a comparison control state machine 12 and a counter stack 13 . The above-mentioned dual-port block RAM11 has two ports, and the two ports are respectively connected to the micro-control unit of the PLC and the comparison control state machine 12 .

[0026] The dual-port block RAM 11 includes multiple sets of compare registers. For example, the dual-port block RA...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More