Simulation method and device for chip surface morphology

A surface topography and chip technology, applied in the field of chip surface topography simulation, can solve problems such as large errors, avoid wrong conclusions, and improve prediction accuracy and accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] In order to make the above objects, features and advantages of the present invention more comprehensible, the embodiments of the present invention will be further described in detail below in conjunction with the accompanying drawings and specific implementation methods.

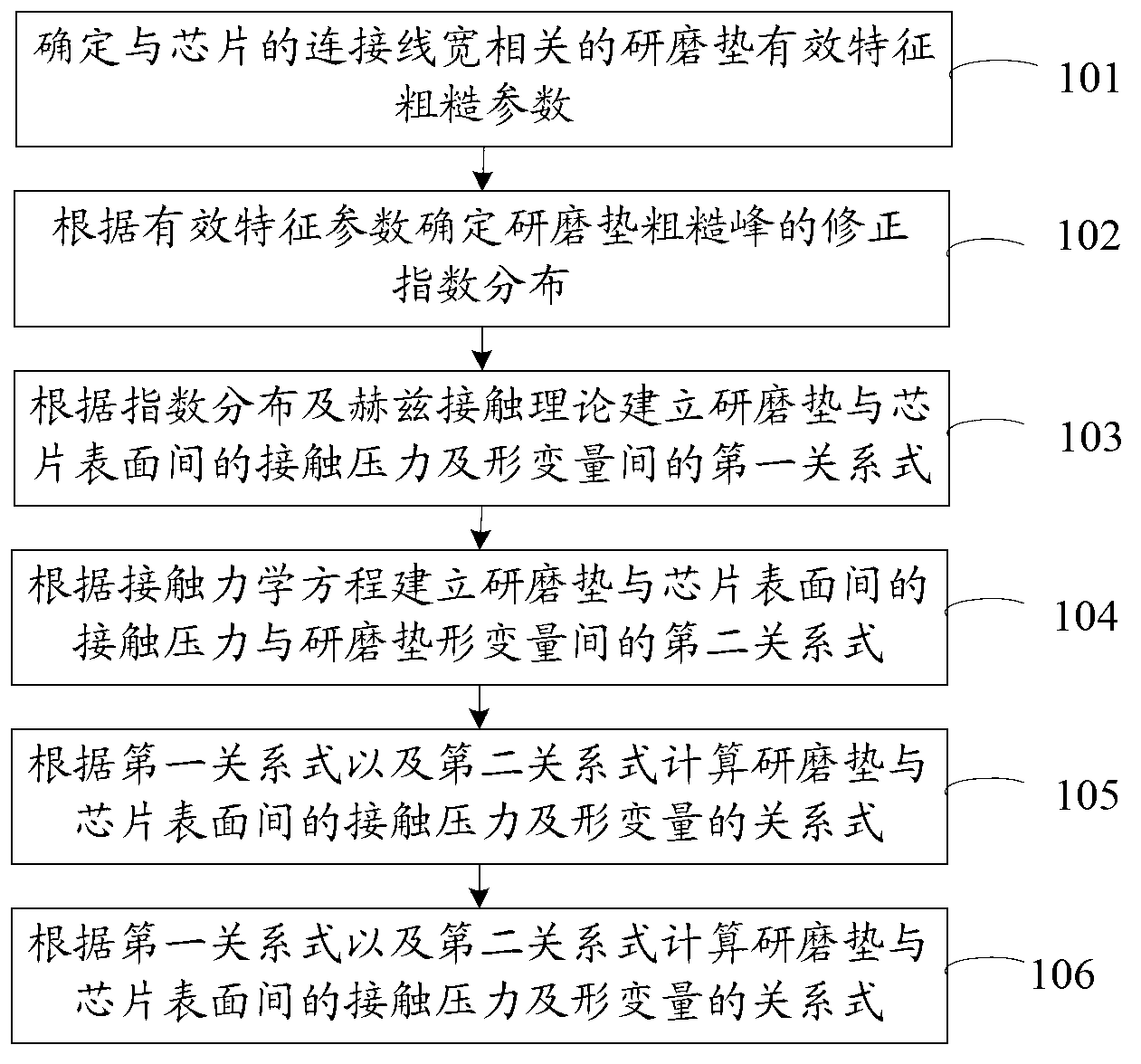

[0023] figure 1 It is a flow chart of the chip surface topography simulation method of the present invention.

[0024] Such as figure 1 As shown, the method includes the following steps:

[0025] Step 101: Determine the effective characteristic roughness parameters of the polishing pad related to the connection line width of the chip;

[0026] Step 102: Determine the modified exponential distribution of the roughness peak of the polishing pad according to the effective characteristic parameters;

[0027] Step 103: Establish a first relationship between the contact pressure between the polishing pad and the chip surface and the deformation of the polishing pad according to the exponential distributi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More