CLB-bus-based NorFLASH memory interface chip with high utilization ratio

A storage interface and utilization technology, applied in the field of NorFLASH storage interface chips, can solve the problems of multiple CPU resource operation steps, many port control signals, cumbersome and other problems, and achieve simple read and write operation steps, strong versatility, and improved utilization. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

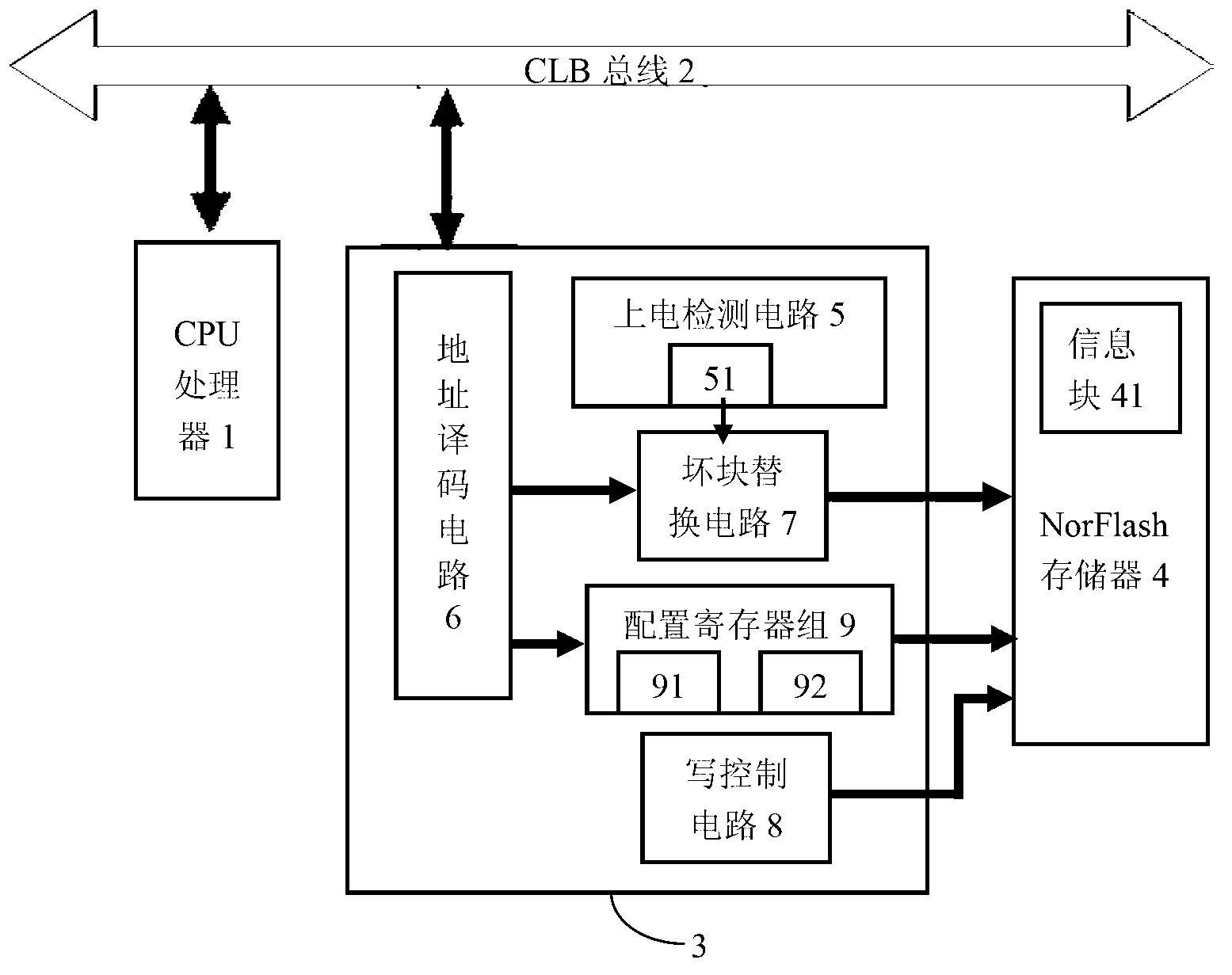

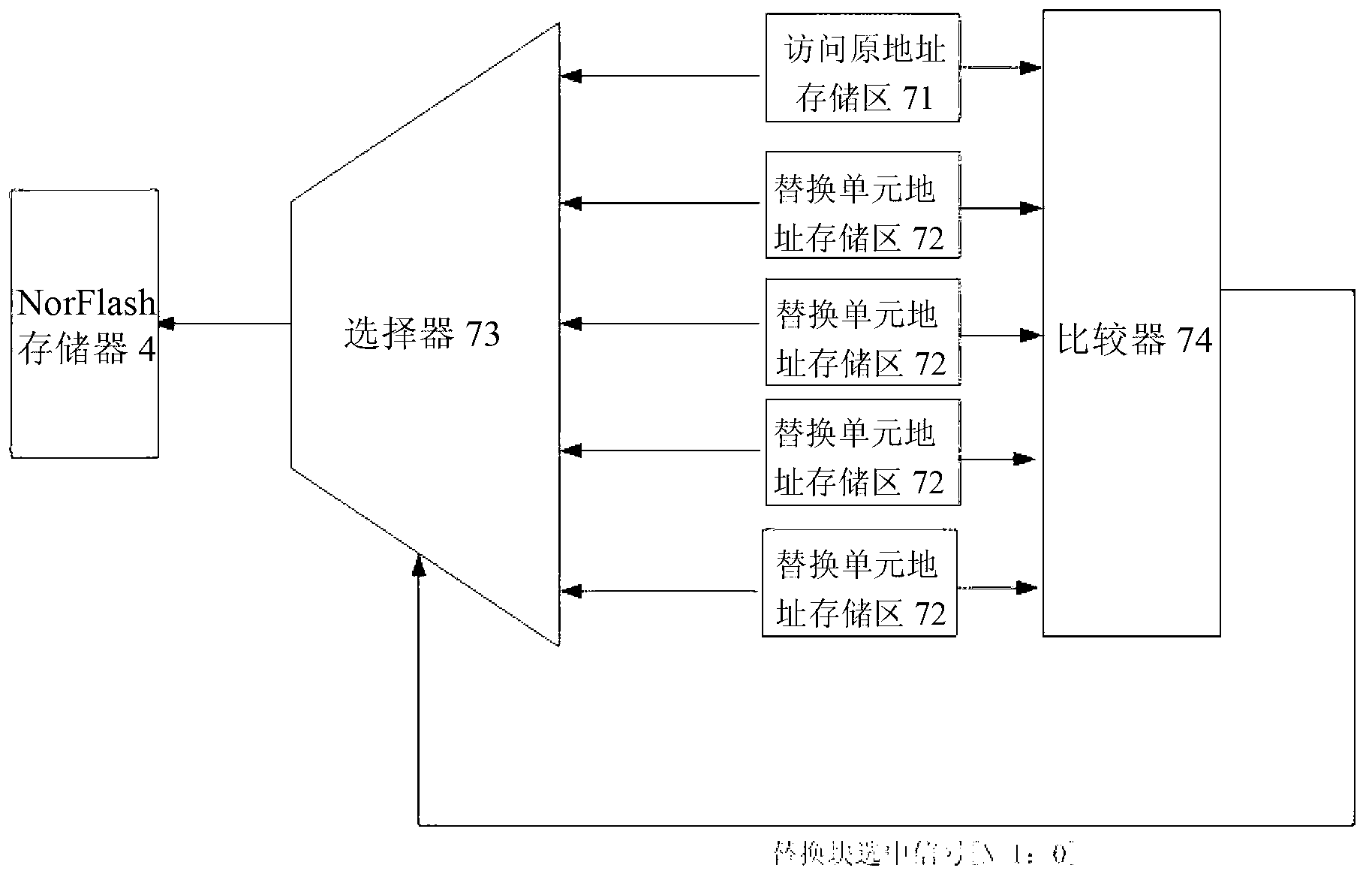

[0029] Embodiment: a kind of NorFLASH storage interface chip with high utilization rate based on CLB bus, comprising CPU processor 1, CLB bus 2, NorFlash interface unit 3, NorFlash memory 4, described NorFlash memory 4 passes CLB bus 2 via NorFlash interface unit 3 Communicate with CPU processor 1; Described NorFlash interface unit 3 further comprises power-on detection circuit 5, address decoding circuit 6, bad block replacement circuit 7, write control circuit 8 and configuration register group 9 and are used to display last operating state The status register group 10;

[0030] There is an information block 41 in the described NorFlash memory 4, and this information block 41 records the address of the bad block unit in the NorFlash memory 4, the address of the number, the replacement unit and the replacement unit to replace the bad block function enabling bit information, and this enabling bit is effective There is a bad block in the identification NorFlash memory 4, and th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More